Thin film transistor and its manufacturing method

A technology of a thin film transistor and a manufacturing method, applied in the field of lightly doped drain structures, can solve the problems of low product production rate, LDD structure position shift, complex process and the like

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0047] The first embodiment of the present invention is to manufacture LDD structures of different lengths for TFT components with different operating voltages. By using the lateral length of the gate insulating layer exposed on both sides of the gate layer as a mask and matching an ion implantation process, it can be simultaneously The fabrication of a self-aligned LDD structure and a source / drain region is achieved. The TFT component structure and its manufacturing method of the present invention can be applied to a P-type TFT component or an N-type TFT component, and can be applied to a TFT component in a pixel array area and a peripheral driver circuit area. The following is a detailed description of self-aligned LDD structure and method of manufacture.

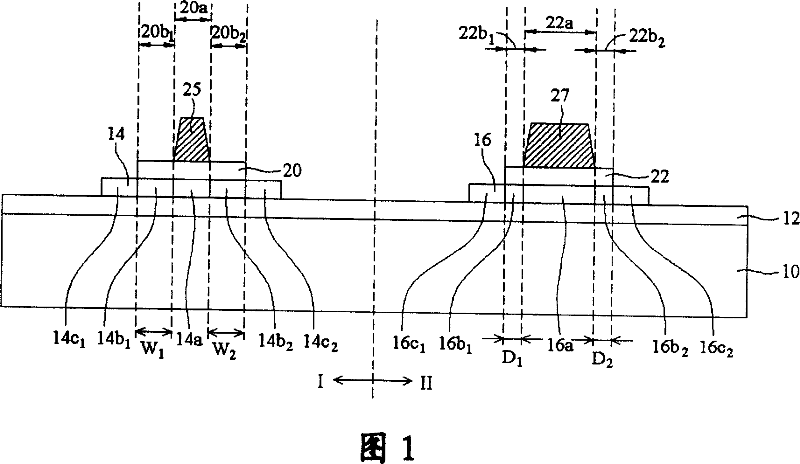

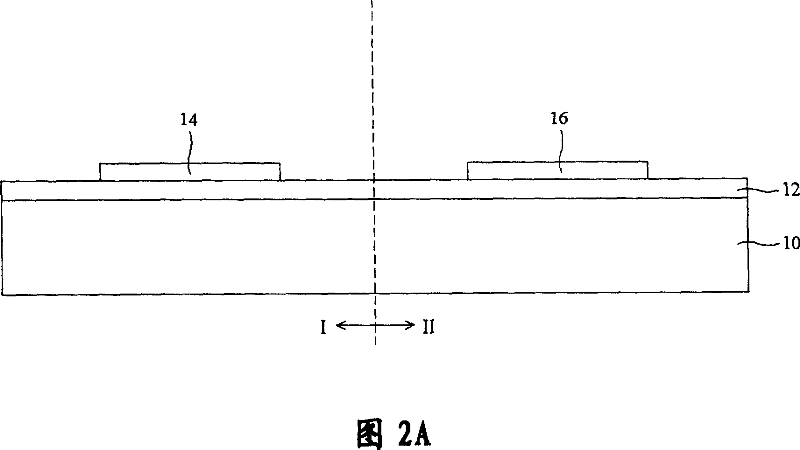

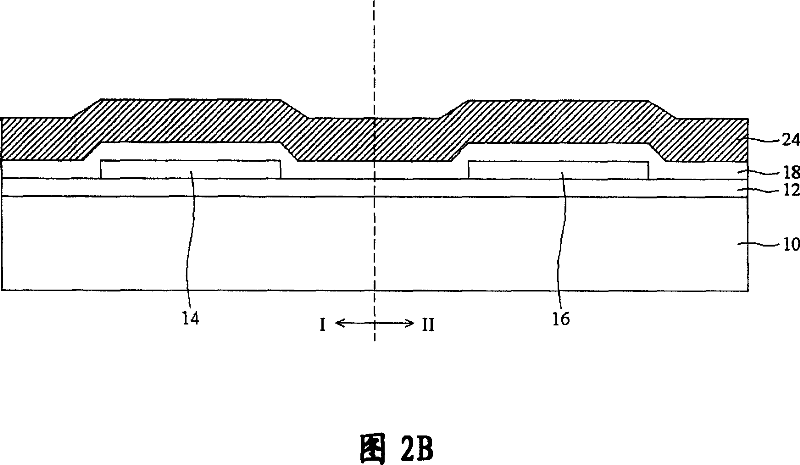

[0048] Please refer to FIG. 1 , which shows a schematic cross-sectional view of a self-aligned LDD structure of a TFT device according to a first embodiment of the present invention.

[0049] A substrate 10 includes a fi...

no. 2 example

[0081] Please refer to FIG. 3 , which shows a schematic cross-sectional view of the self-aligned LDD structure of the TFT device according to the second embodiment of the present invention.

[0082] The TFT components and structural features of the second embodiment are substantially the same as those described in the first embodiment, and the similarities will not be described again.

[0083] In the first TFT region I, the first gate insulating layer 20 further includes a first extension region 20c 1 and a second extension region 20c 2 . first extension area 20c 1 is located in the first shielded area 20b 1 left side, and covering the first heavily doped region 14c 1 ; second extension region 20c 2 is located in the second shielded area 20b 2 Right side, and covering the second heavily doped region 14c 2 . In particular, the first extension region 20c 1 Thickness T 1 smaller than the first shielding area 20b 1 Thickness T 2 , it is also possible to make the first ...

no. 3 example

[0087] Please refer to FIG. 4 , which shows a schematic cross-sectional view of a self-aligned LDD structure of a TFT device according to a third embodiment of the present invention.

[0088] The TFT components and structural features of the third embodiment are substantially the same as those described in the second embodiment, and the similarities will not be described again.

[0089] In the first TFT region I, the first gate insulating layer 20 is formed by stacking a first insulating layer 20I and a second insulating layer 20II. The preferred one of the first insulating layer 20I is a silicon oxide layer, a silicon nitride layer, a silicon oxynitride layer or a combination thereof, and the preferred one of the second insulating layer 20II is a silicon oxide layer, a silicon nitride layer , a silicon oxynitride layer or a combination thereof. Located in the central region 20a, the double-layer structure of the first insulating layer 20I and the second insulating layer 20II...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Doping concentration | aaaaa | aaaaa |

| Doping concentration | aaaaa | aaaaa |

| Horizontal length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More