3D polysilicon read only memory and preparation method

A technology of read-only memory and manufacturing method, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve problems such as the influence of the correct position of the memory cell and the influence of the product qualification rate.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

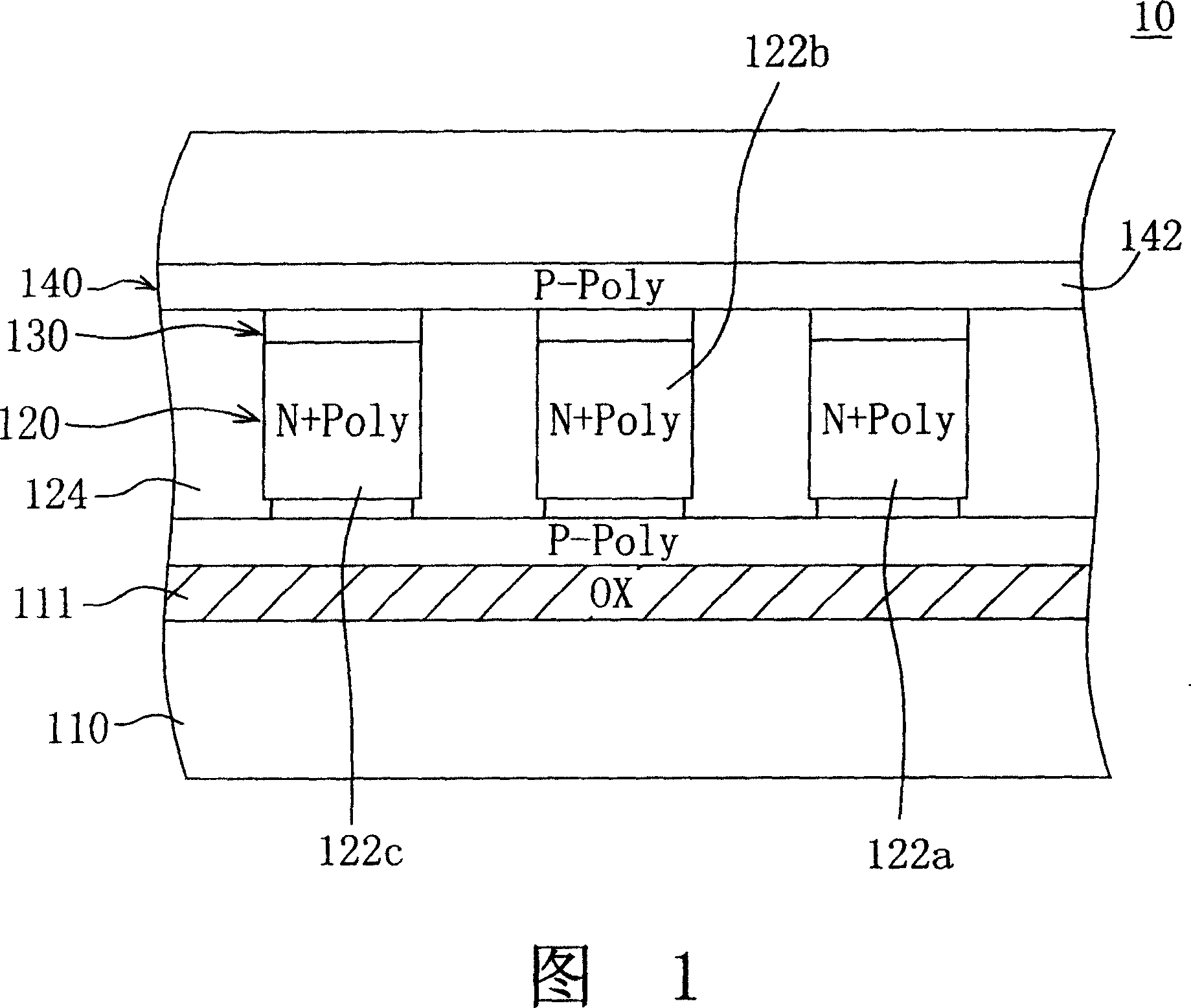

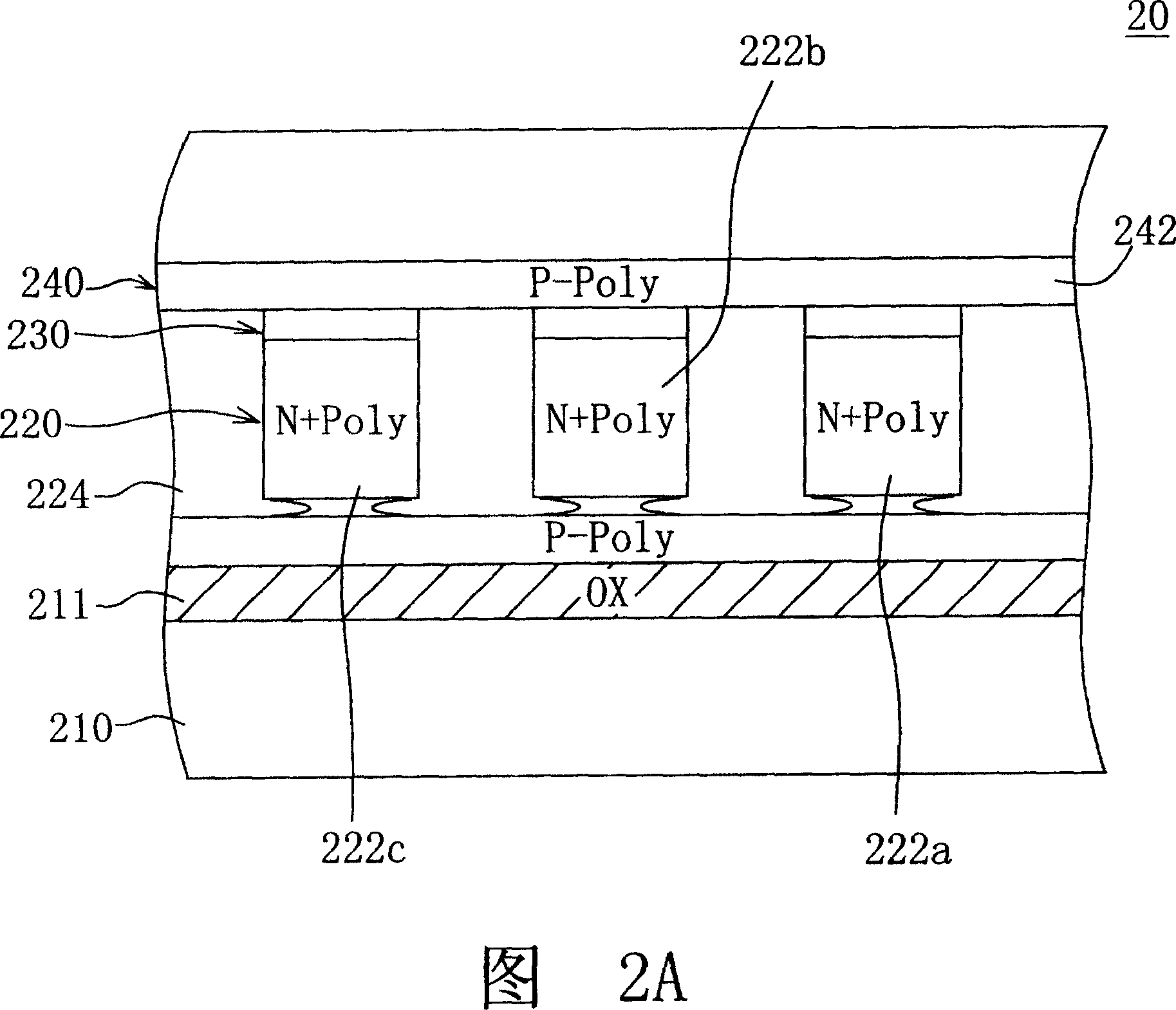

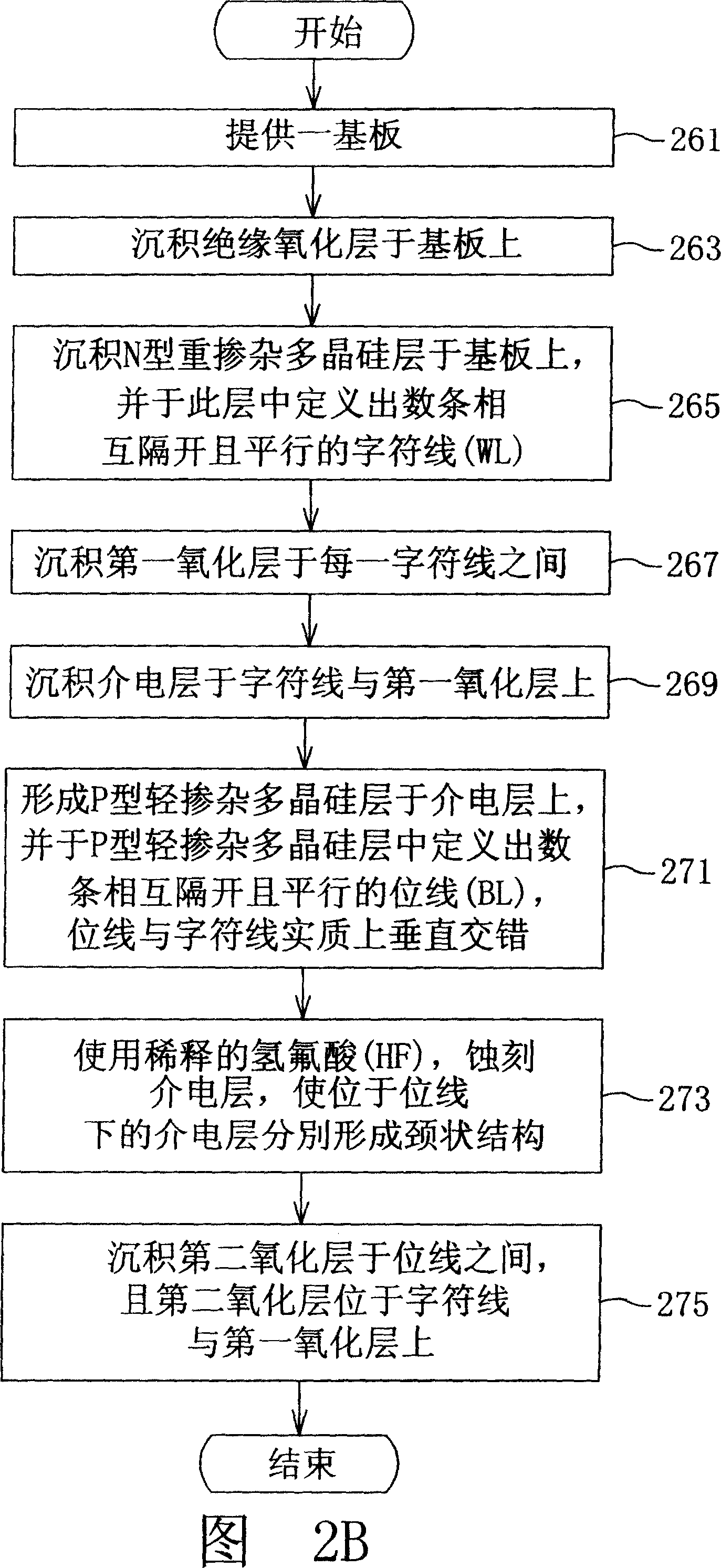

[0018] Please refer to FIG. 2A . FIG. 2A is a cross-sectional view of a three-dimensional polysilicon read-only memory according to a first embodiment of the present invention. The three-dimensional polysilicon ROM 20 includes: a silicon substrate 210 , an insulating oxide layer 211 , an N-type heavily doped polysilicon layer 220 , a P-type lightly doped polysilicon layer 240 , a dielectric layer 230 , and oxide layers 224 and 244 .

[0019] The insulating oxide layer 211 is located on the silicon substrate 210 , and the N-type heavily doped polysilicon layer 220 is located on the insulating oxide layer 211 . The N-type heavily doped polysilicon layer 220 is located on the silicon substrate 210, and the N-type heavily doped polysilicon layer 220 includes several mutually spaced and parallel word lines (Word Line, WL), for the convenience of description, in FIG. 2A , represented by three word lines, which are respectively word lines 222a, 222b, and 222c. The oxide layer 224 is...

no. 2 example

[0027] Please refer to FIG. 3A and FIGS. 3B-3F at the same time. FIG. 3A shows a flow chart of a method for manufacturing a three-dimensional polysilicon read-only memory according to the second embodiment of the present invention, and FIGS. 3B-3F show a flow chart according to the first embodiment of the present invention. A cross-sectional view of the process of the manufacturing method of the three-dimensional polysilicon read-only memory in the second embodiment. As shown in FIG. 3F, the three-dimensional polysilicon read-only memory 30 includes a silicon substrate 310, an insulating oxide layer 311, an N-type heavily doped polysilicon layer 320, a dielectric layer 330, a P-type lightly doped polysilicon layer 340, 350, and an oxide layer 344. , 354.

[0028] The manufacturing method of the 3D polysilicon ROM according to the second embodiment of the present invention is as follows: First, in step 361 , a silicon substrate 310 is provided. Next, in step 363 , an insulatin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com