Split-groove grid flash memory and preparation method thereof

A memory and split slot technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problems of NROM flash memory unit area reduction, poor CHEI programming injection efficiency, and limit NROM flash memory, etc., to reduce programming Effects of power consumption, increased scaling capability, and reduced programming power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] The split trench gate flash memory provided by the present invention and its manufacturing method will be described in detail below with reference to the accompanying drawings, but this does not constitute a limitation of the present invention.

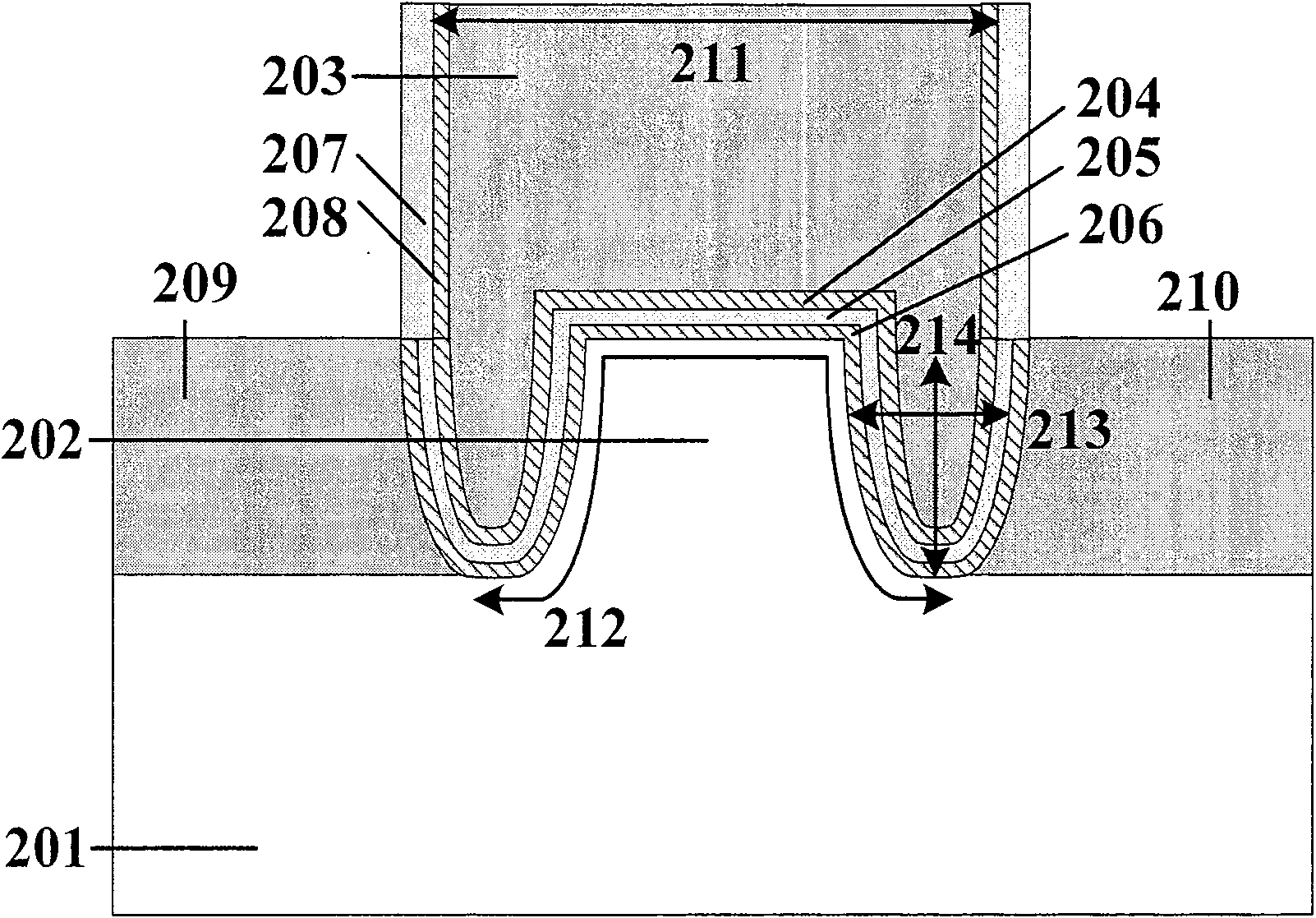

[0056] Such as figure 2 Shown is the split trench gate flash memory of this embodiment. The flash memory is based on a planar structure. In this flash memory, between the two ends of the channel 202 and the n+ source 209 and the n+ drain 210, there is a completely identical trench, the width 213 of the trench is 30nm-40nm, and the depth 214 is 30nm-40nm. 60nm, the trench directly below includes a part of the channel and a part of the n+ source or drain; the channel 202 is divided into three parts, and each of the two ends of the channel has a non-planar channel corresponding to the trench, and the channel In the middle is a planar channel, and a split-recess-channel structure (Split-Recess-Channel) is formed in the channel r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More