InGaAs low table face linear array or face array infrared detector chip

A technology of infrared detectors and mesa wires, applied in the field of infrared detectors, can solve the problems of device reliability reduction, bad side passivation, limit device detection rate, etc., and achieve the effect of improving device reliability and preventing external diffusion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] Below in conjunction with accompanying drawing and embodiment the specific embodiment of the present invention is described in further detail:

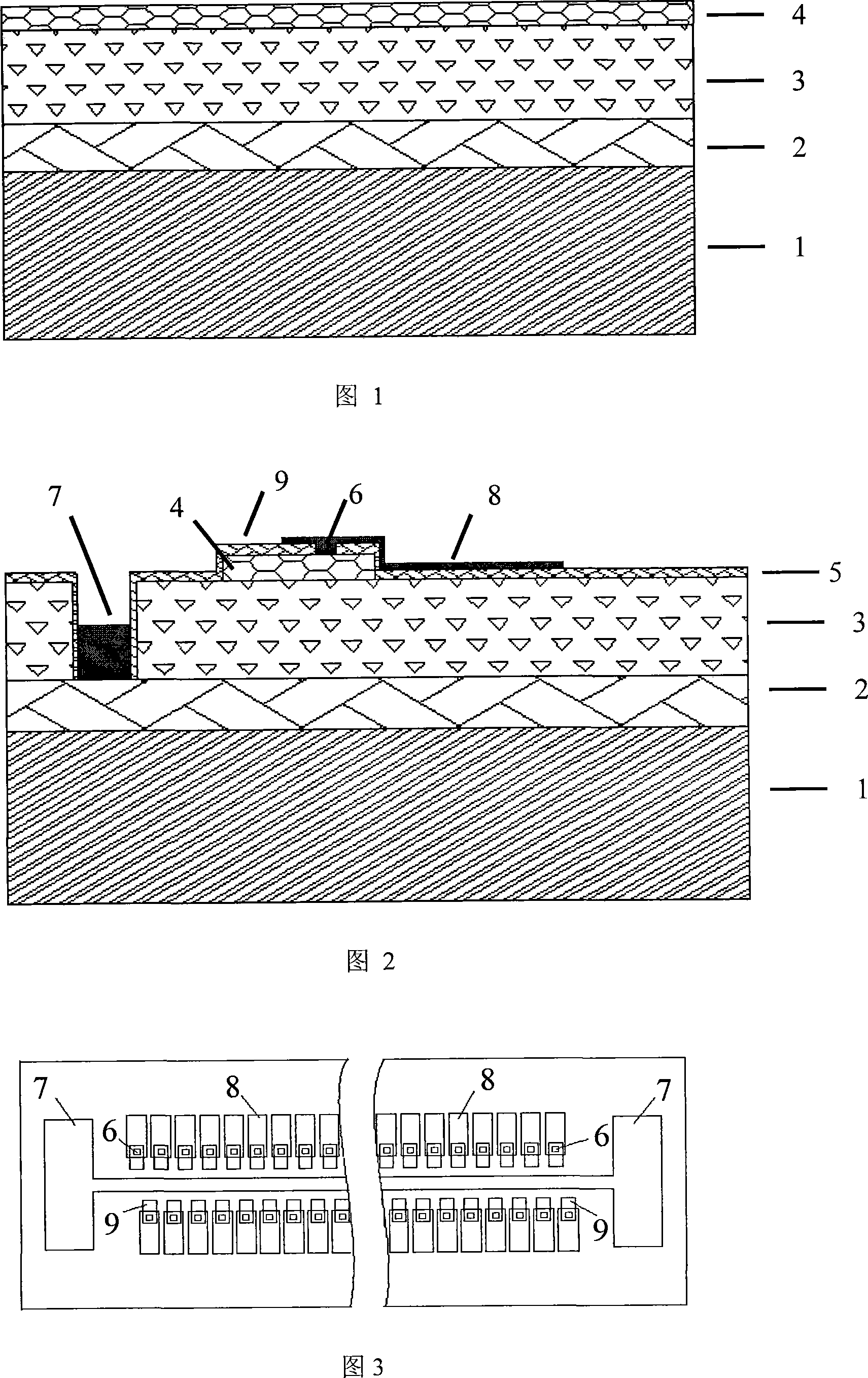

[0014] As shown in Fig. 1, the epitaxial wafer used in this embodiment is an n-type InP layer 2 with a thickness of 1 μm grown sequentially on a semi-insulating InP substrate 1 with a thickness of 350 μm by MBE technology, and the carrier concentration is greater than 2×10 18 cm -3 ; In with a thickness of 2.5 μm 0.53 Ga 0.47 As intrinsic absorption layer 3; p-type InP cap layer 4 with a thickness of 0.5 μm, and a carrier concentration greater than 2×10 18 cm -3 .

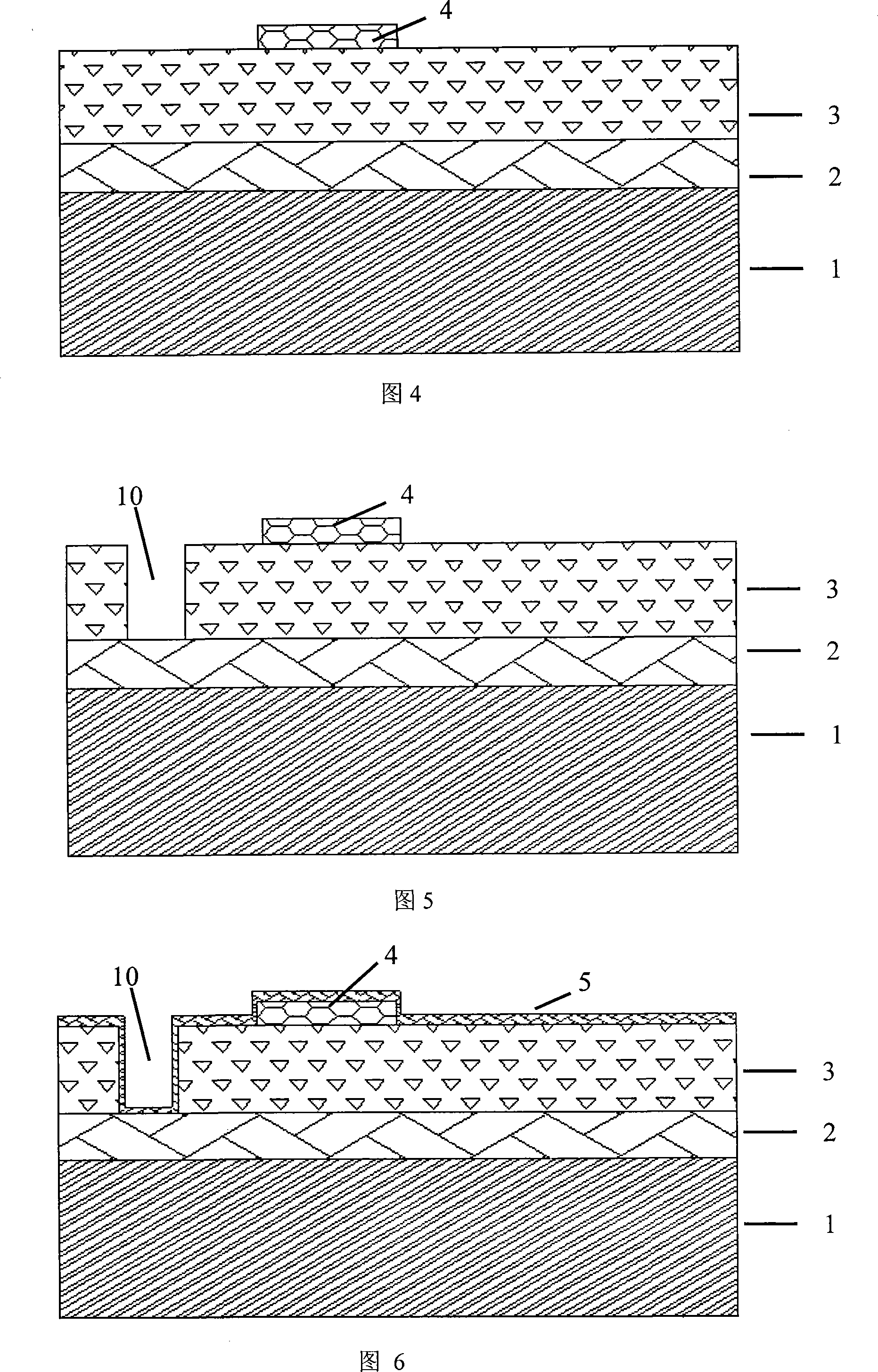

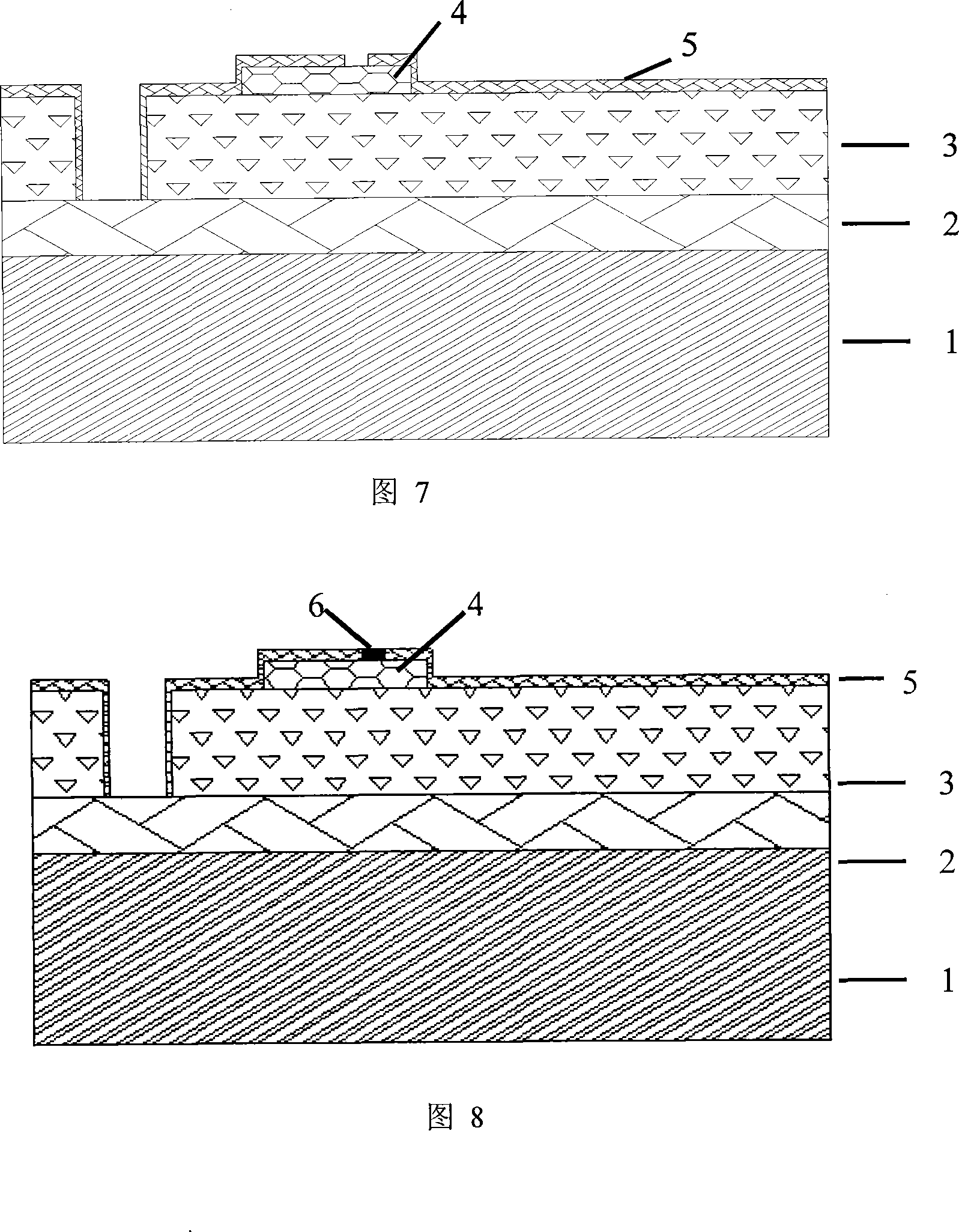

[0015] FIG. 2 is a schematic cross-sectional structure diagram of the present embodiment, in which linear p-InP micro-mesas 4 are formed on the epitaxial wafer by etching. Au / Zn / Pt / Au / P electrode region 6 in ohmic contact with p-InP is placed on the local area of the p-InP micro-mesas, and there is an etching to the n-InP layer on the edge of the line-column ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More