Patents

Literature

56results about How to "Reduce surface state" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

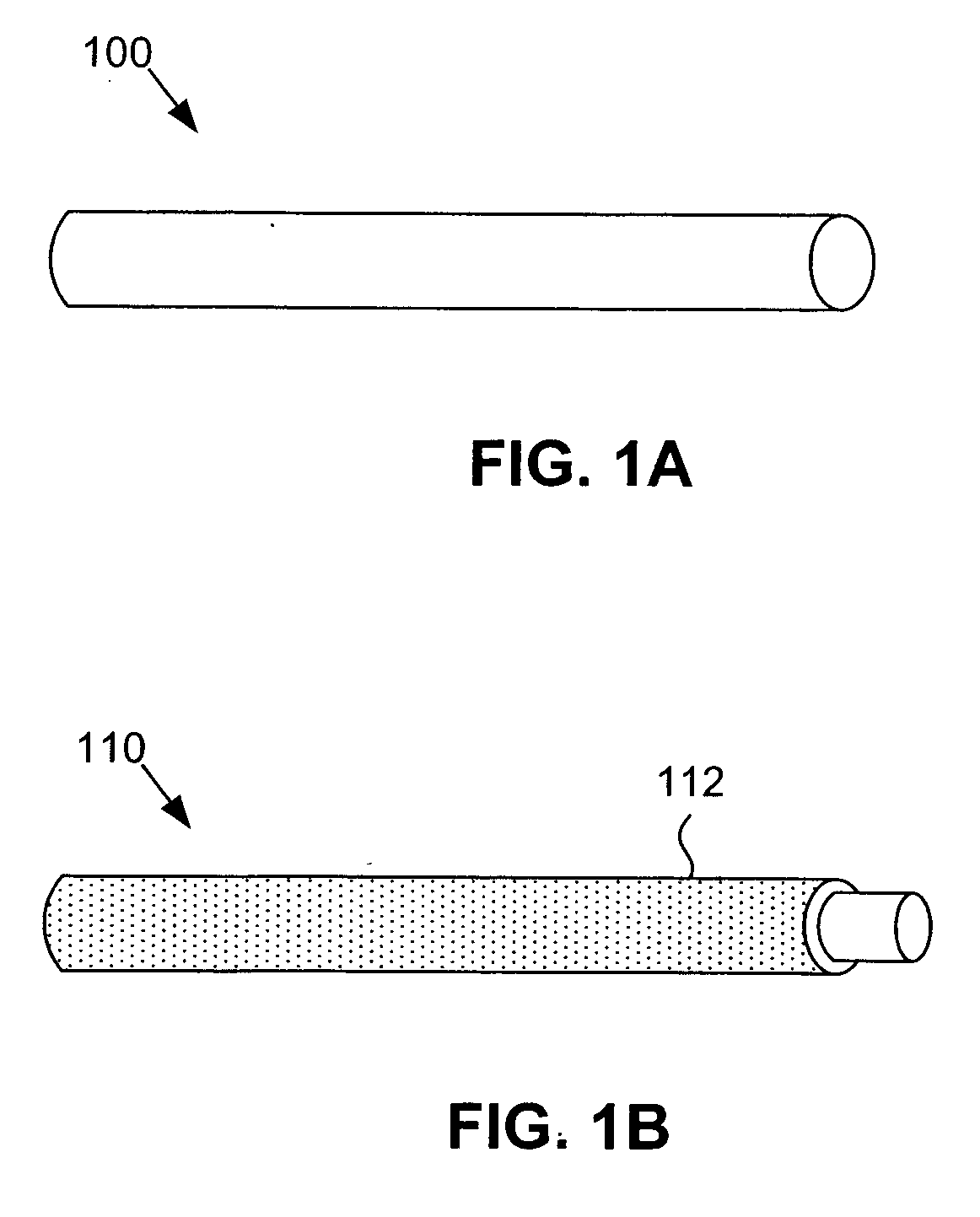

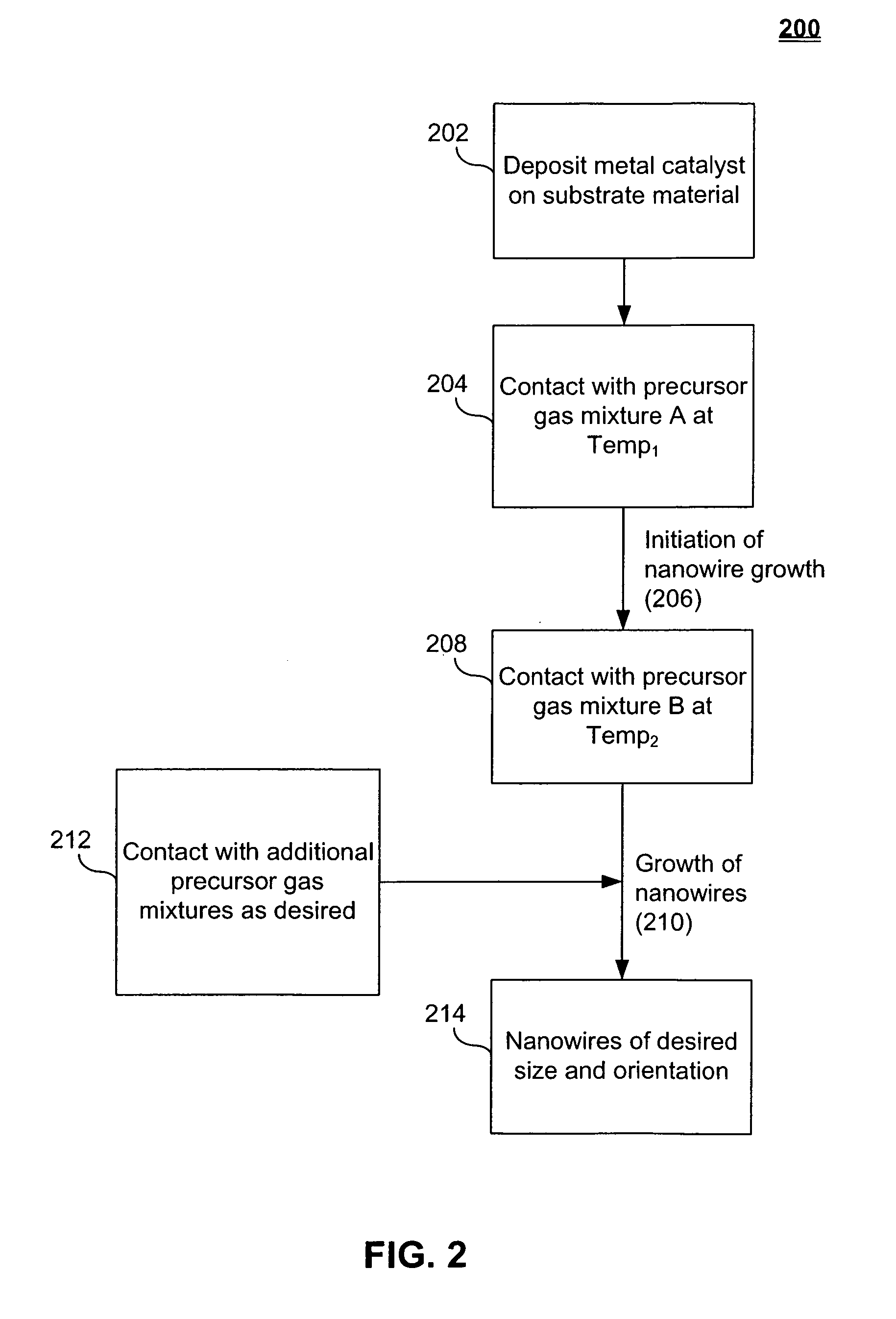

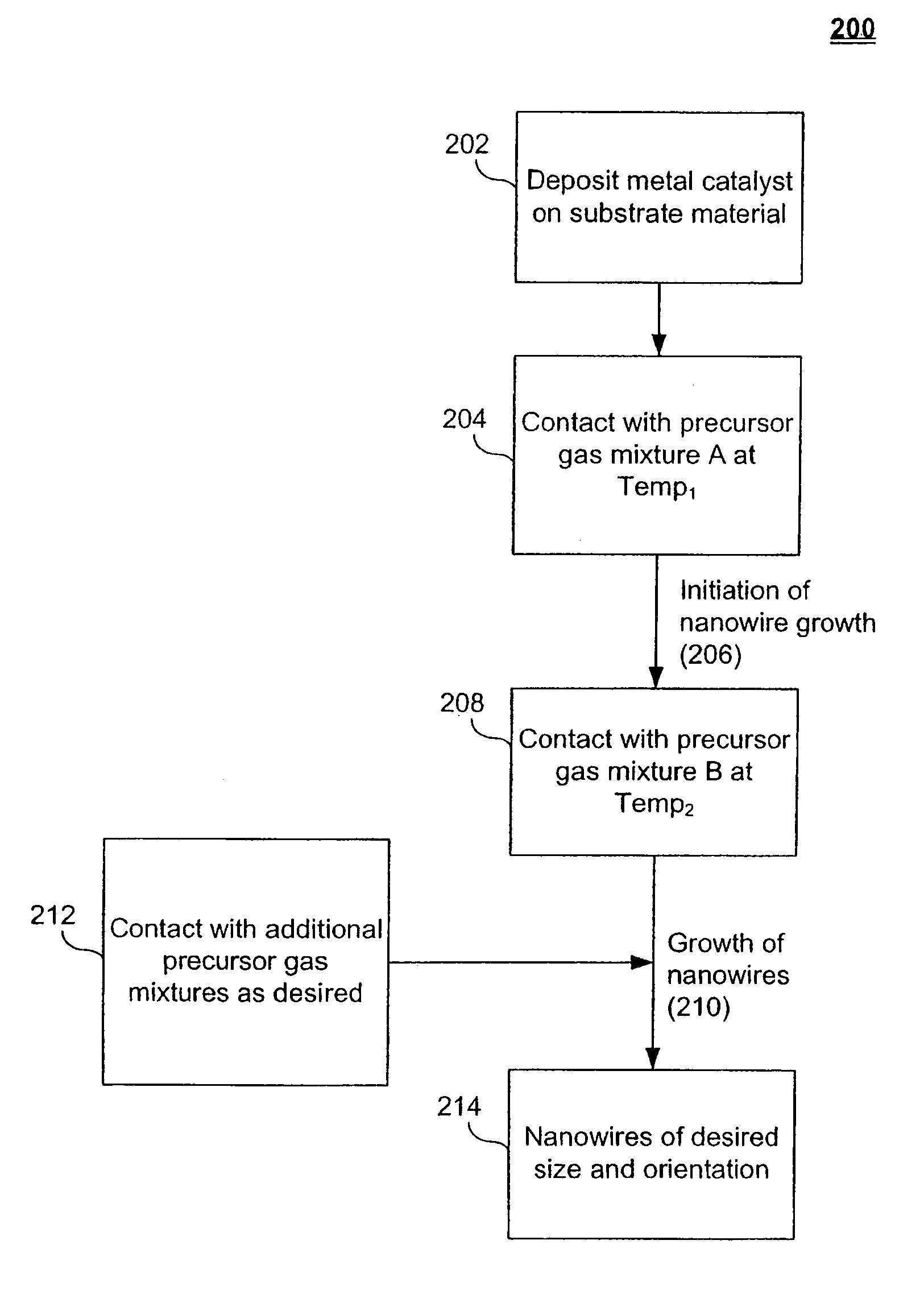

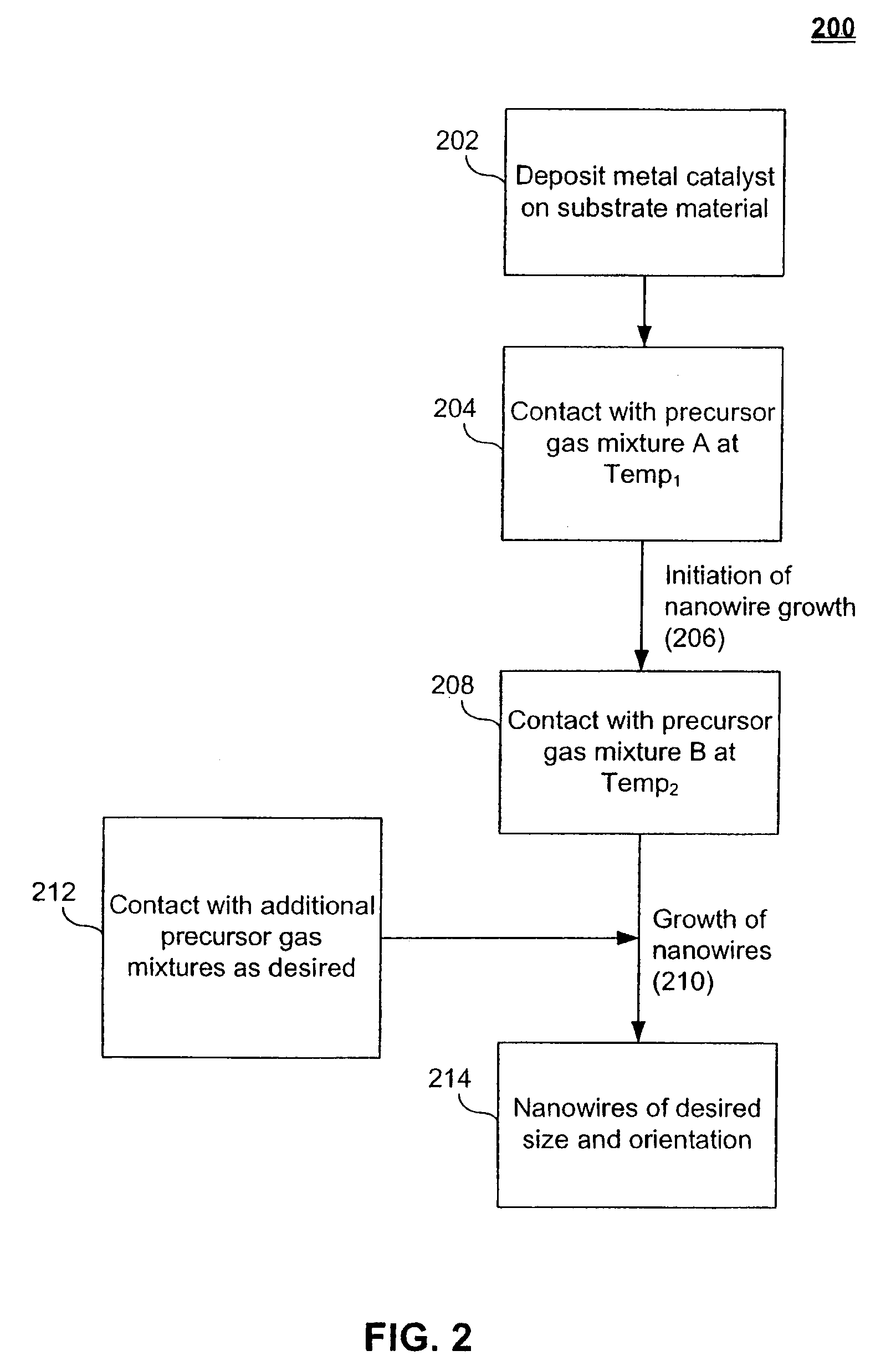

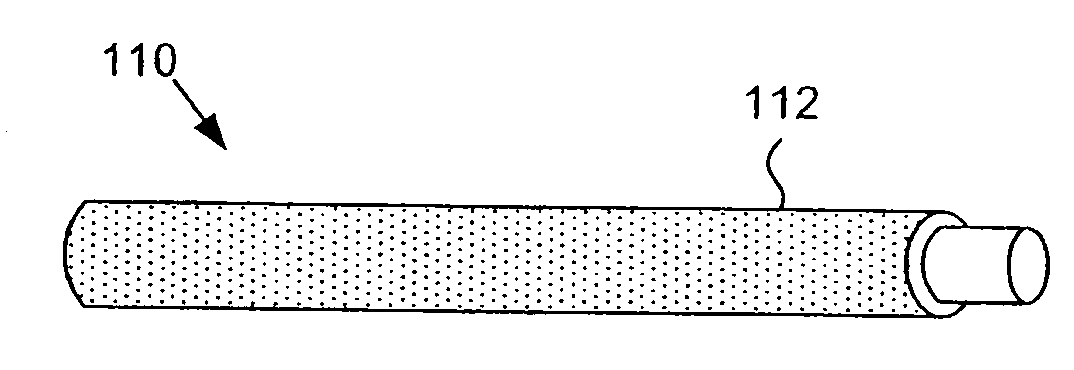

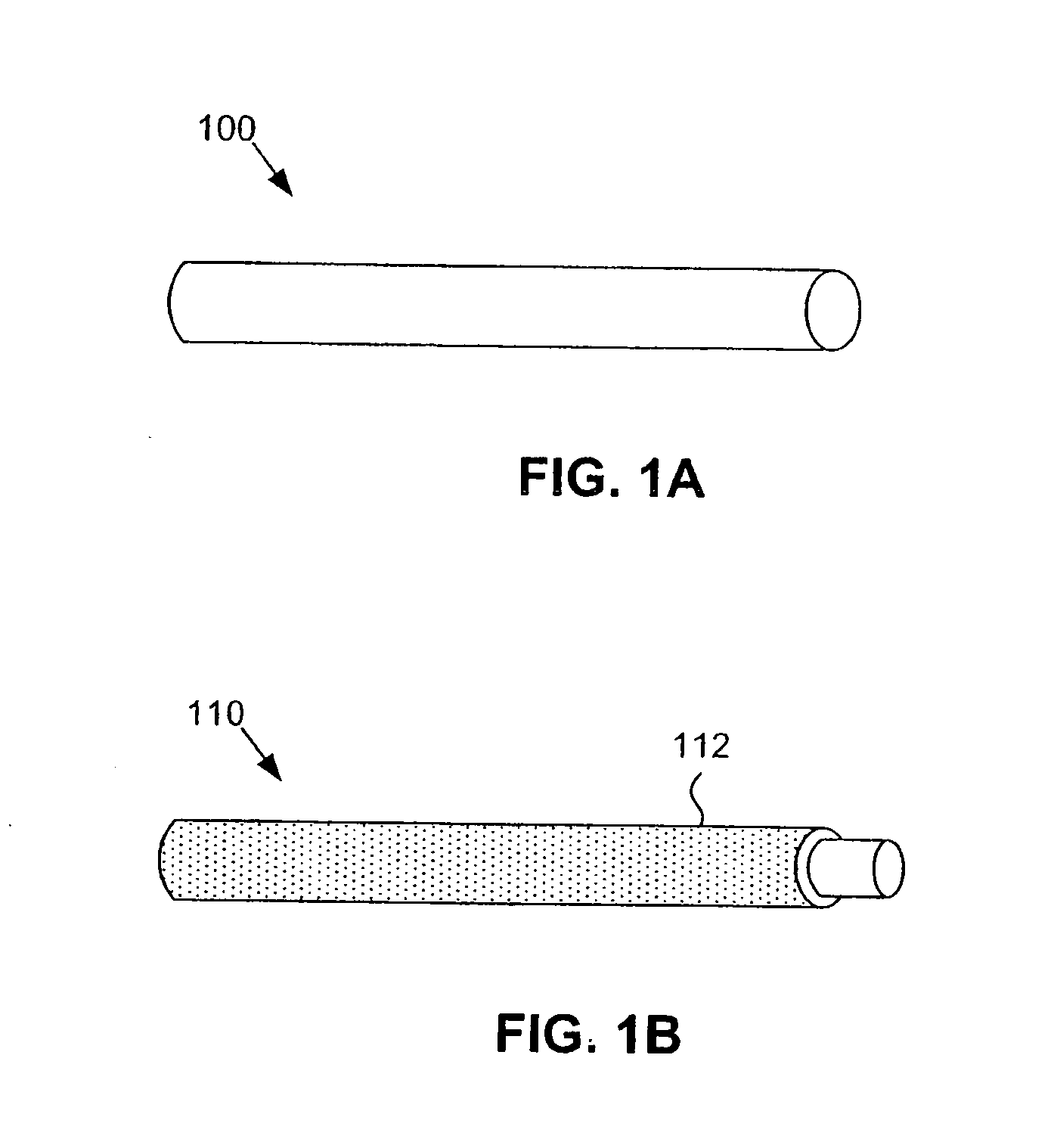

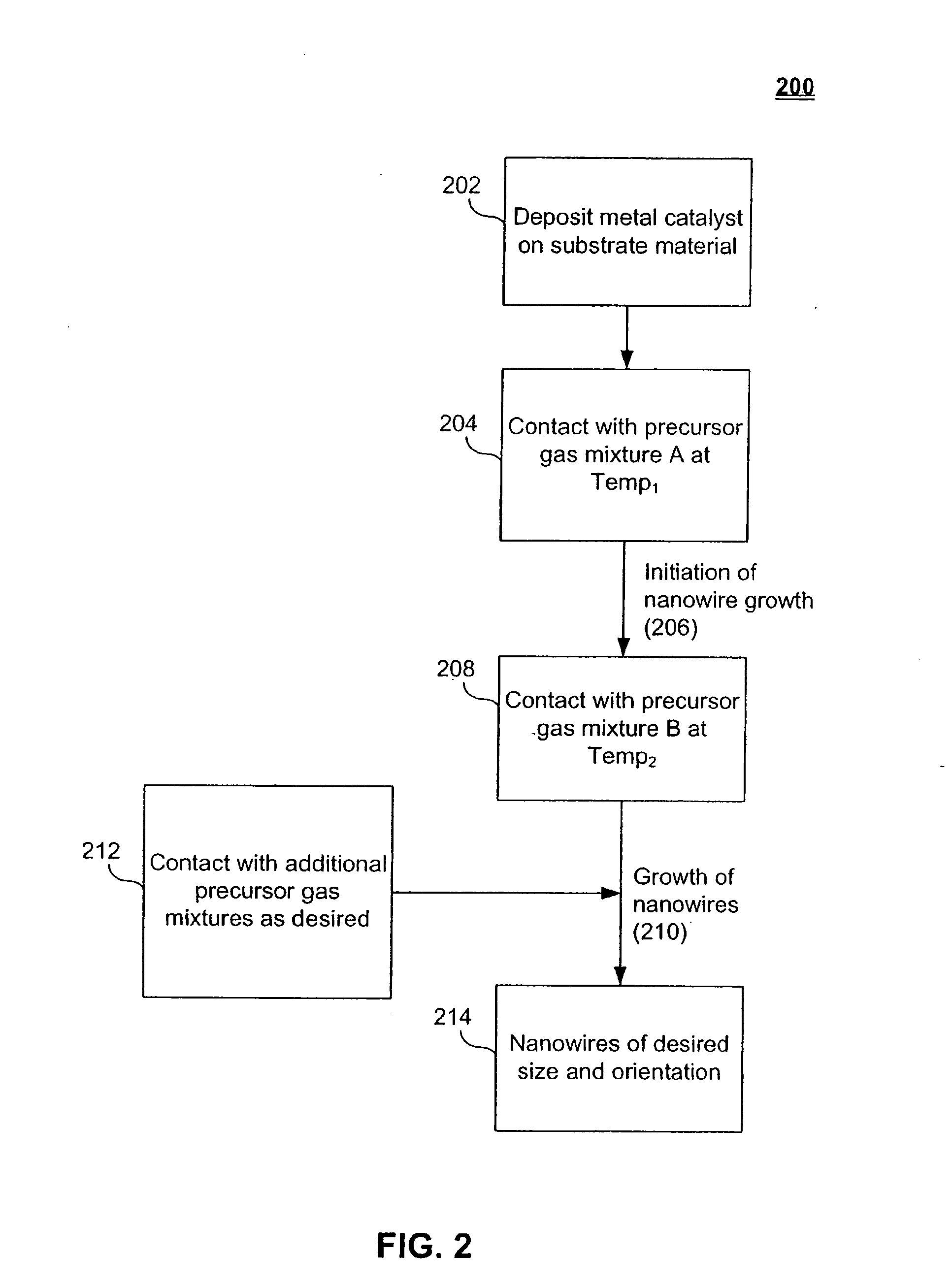

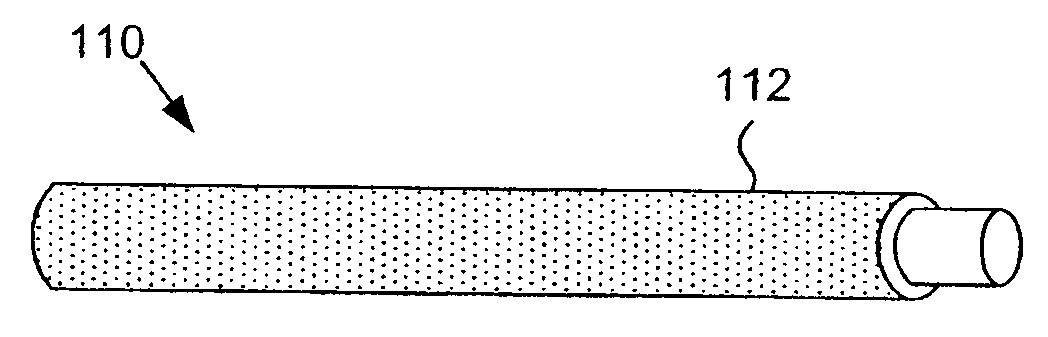

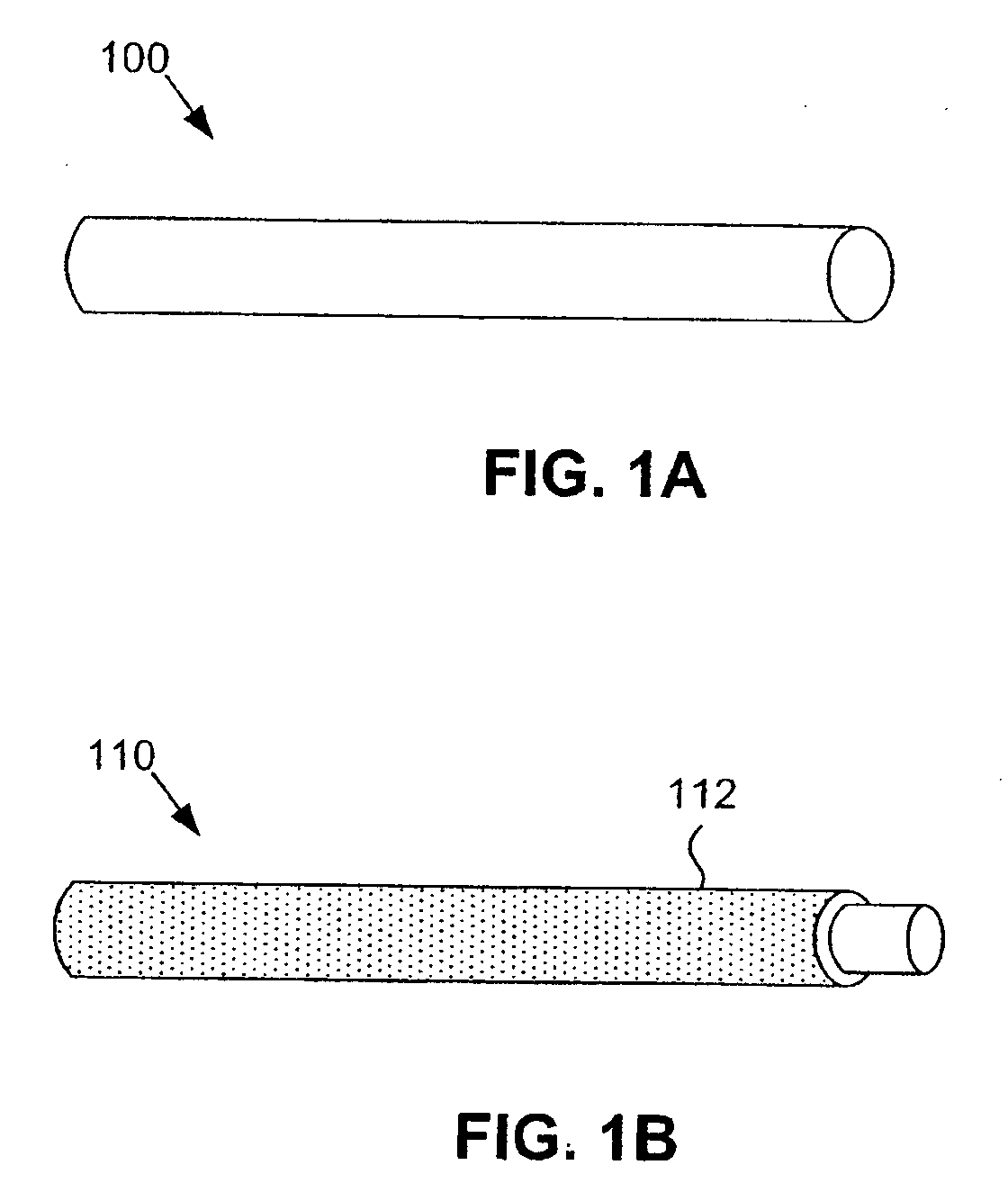

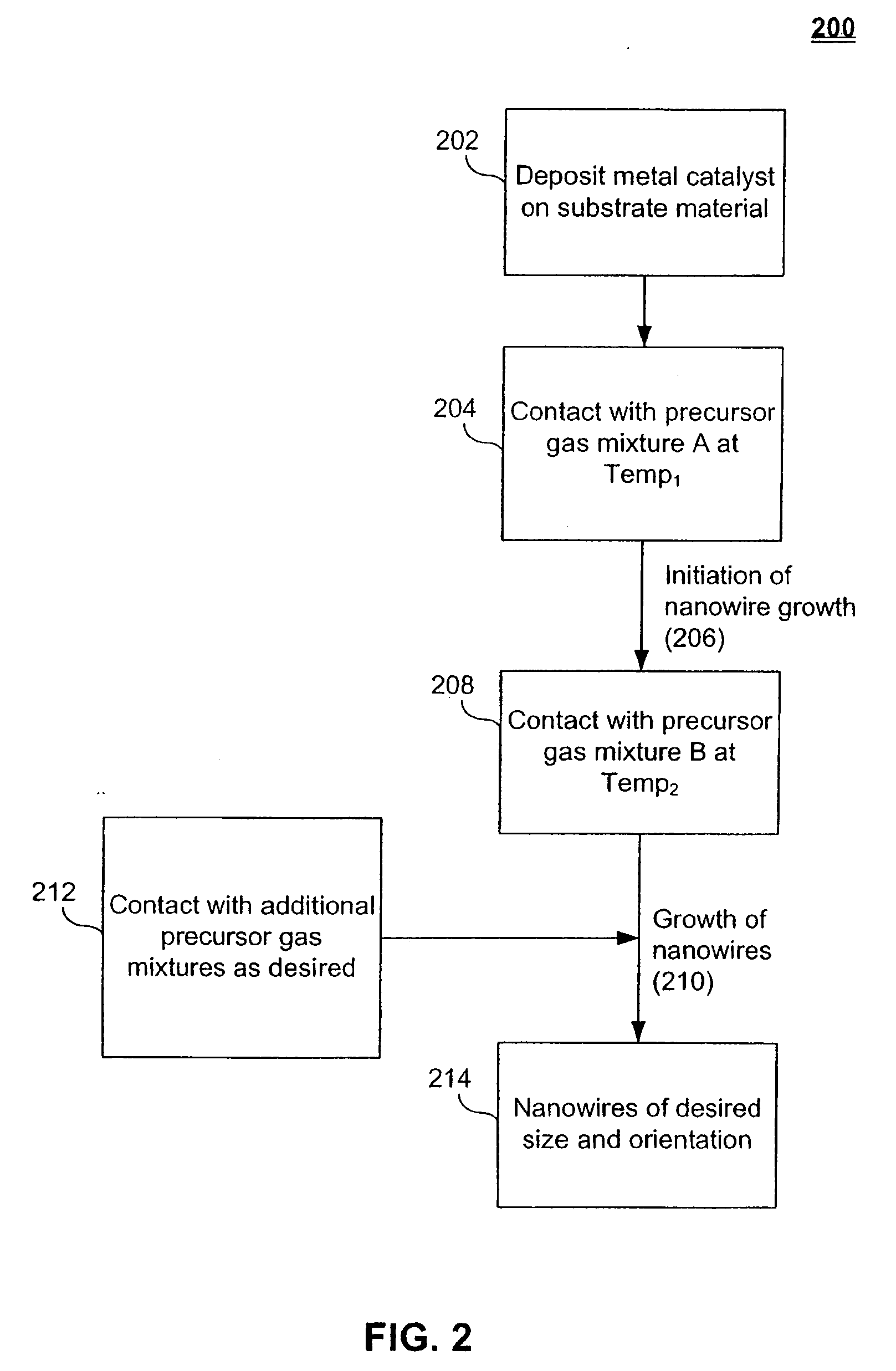

Systems and methods for nanowire growth and harvesting

ActiveUS7105428B2Minimize diffusionIncrease depositionMaterial nanotechnologyNanostructure manufactureNanowireSilicon

Owner:ONED MATERIAL INC

Systems and methods for nanowire growth and harvesting

ActiveUS20060019472A1Minimize diffusionIncrease depositionMaterial nanotechnologyPolycrystalline material growthNanowireSilicon

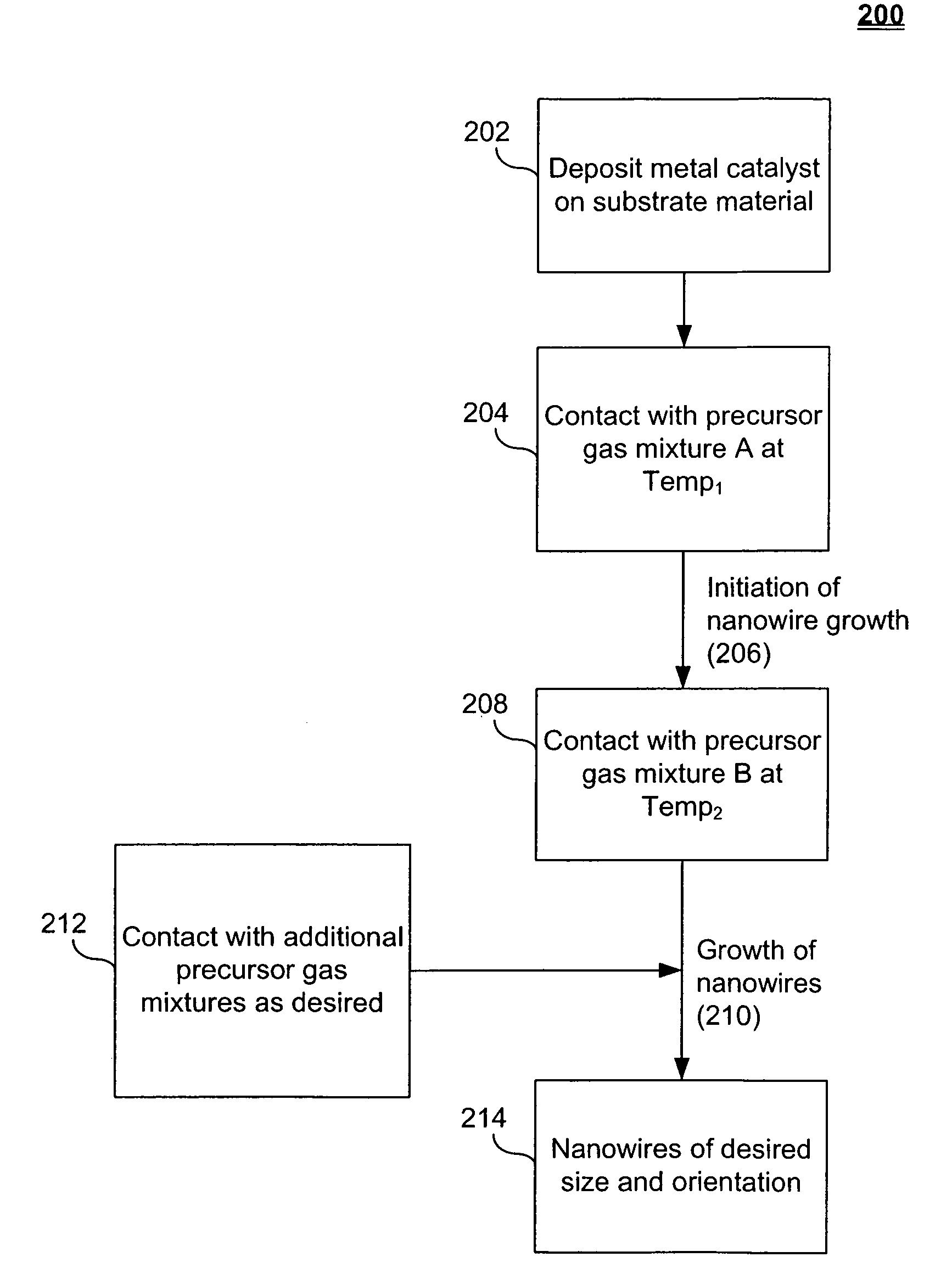

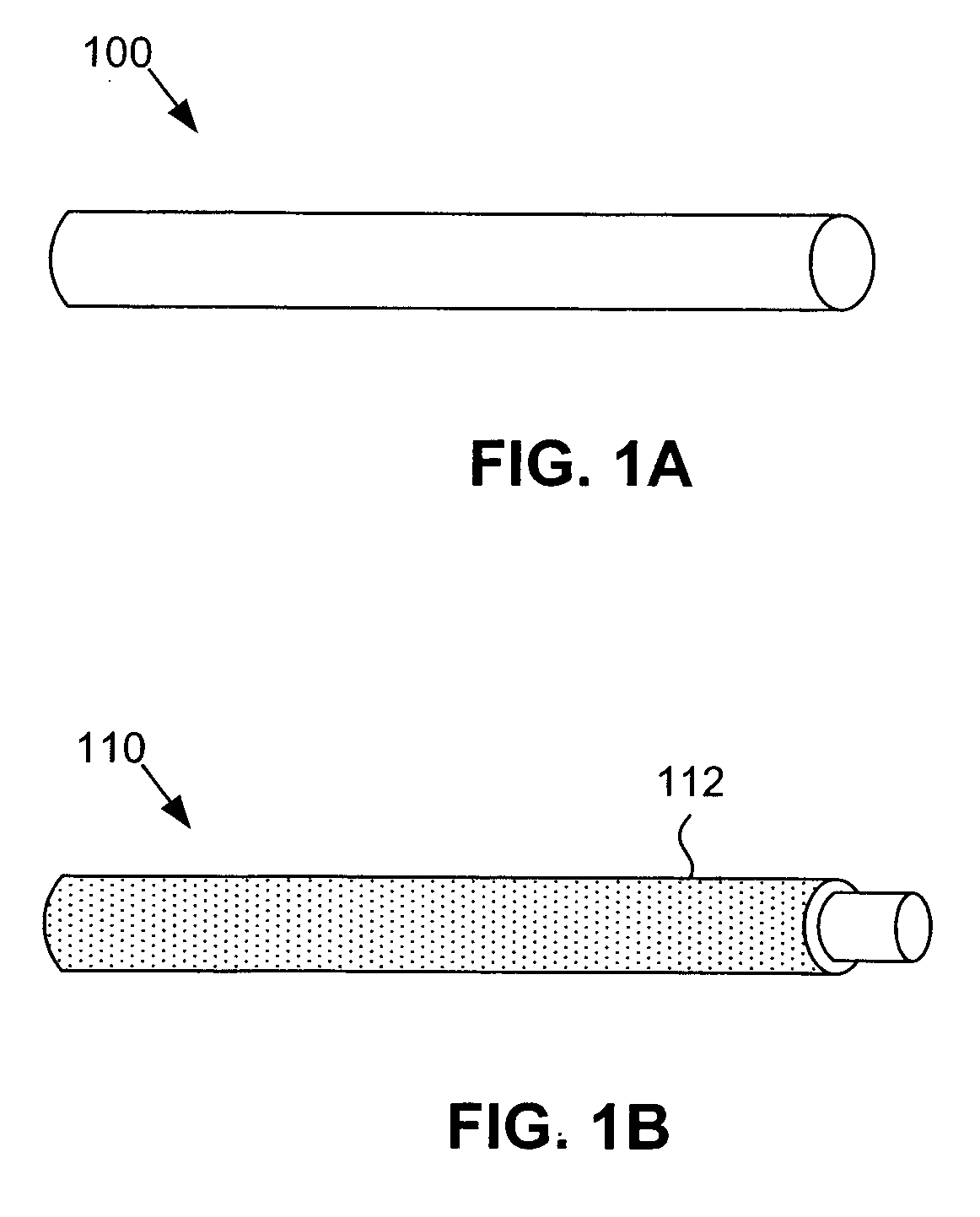

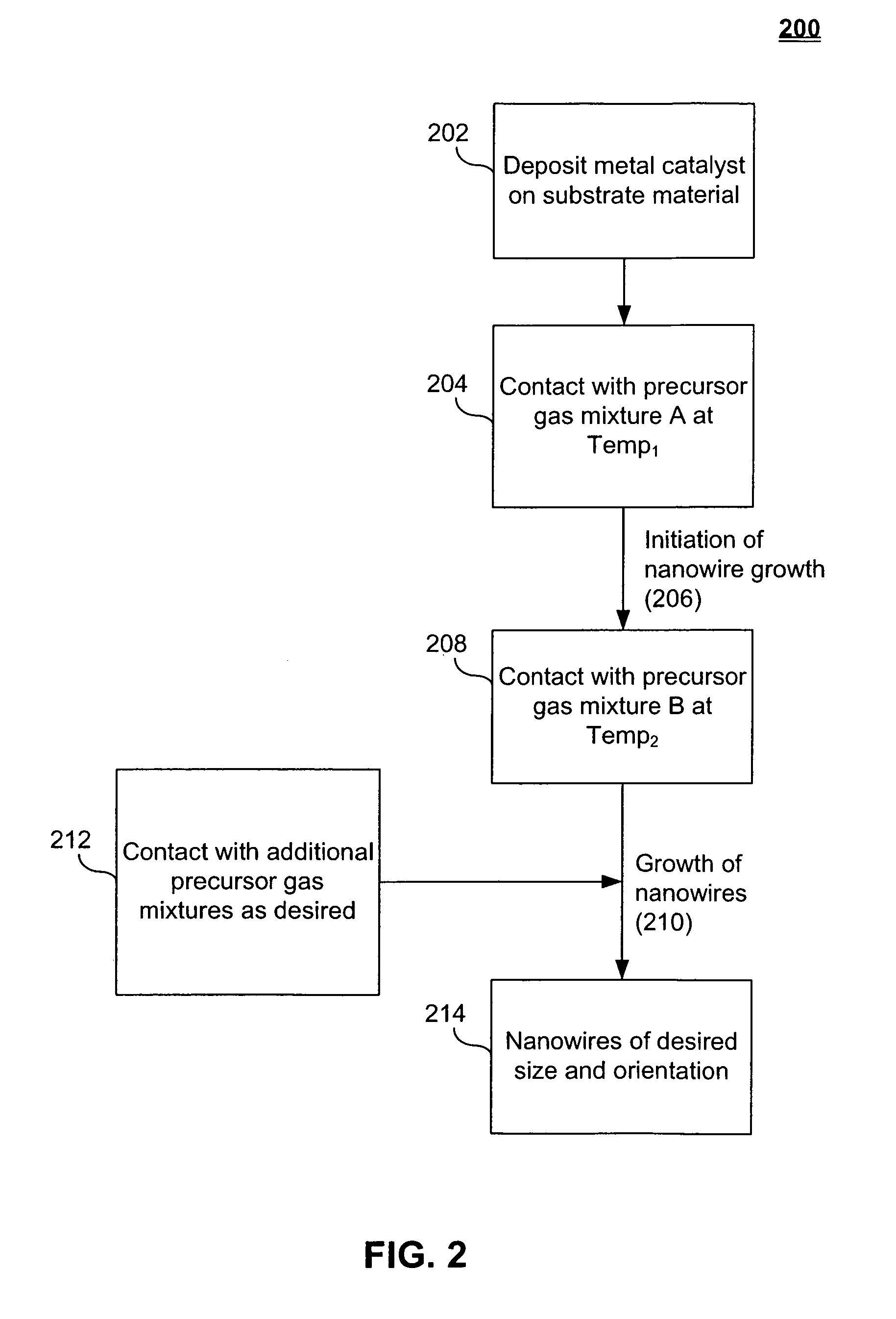

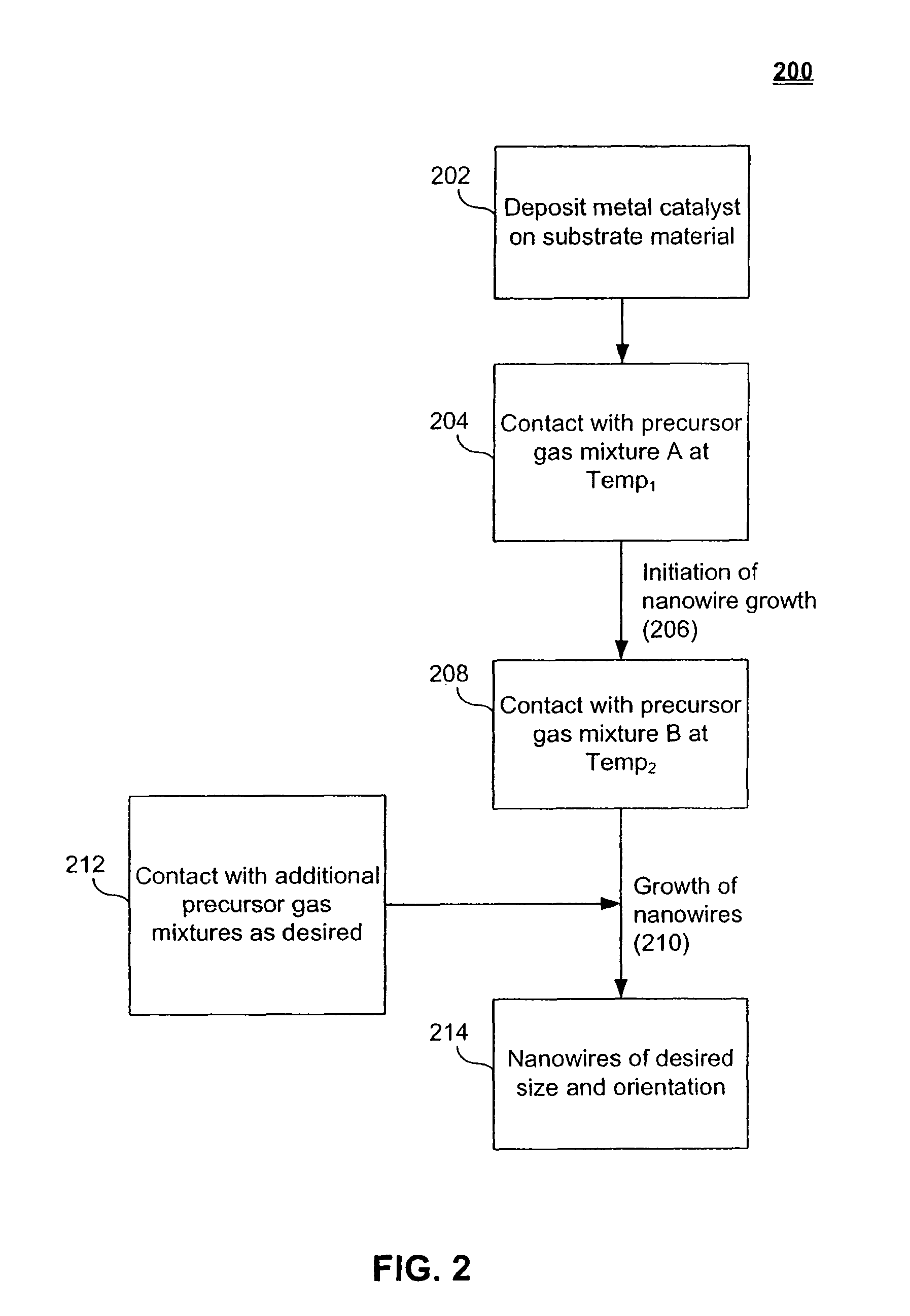

The present invention is directed to systems and methods for nanowire growth and harvesting. In an embodiment, methods for nanowire growth and doping are provided, including methods for epitaxial oriented nanowire growth using a combination of silicon precursors. In a further aspect of the invention, methods to improve nanowire quality through the use of sacrifical growth layers are provided. In another aspect of the invention, methods for transferring nanowires from one substrate to another substrate are provided.

Owner:ONED MATERIAL INC

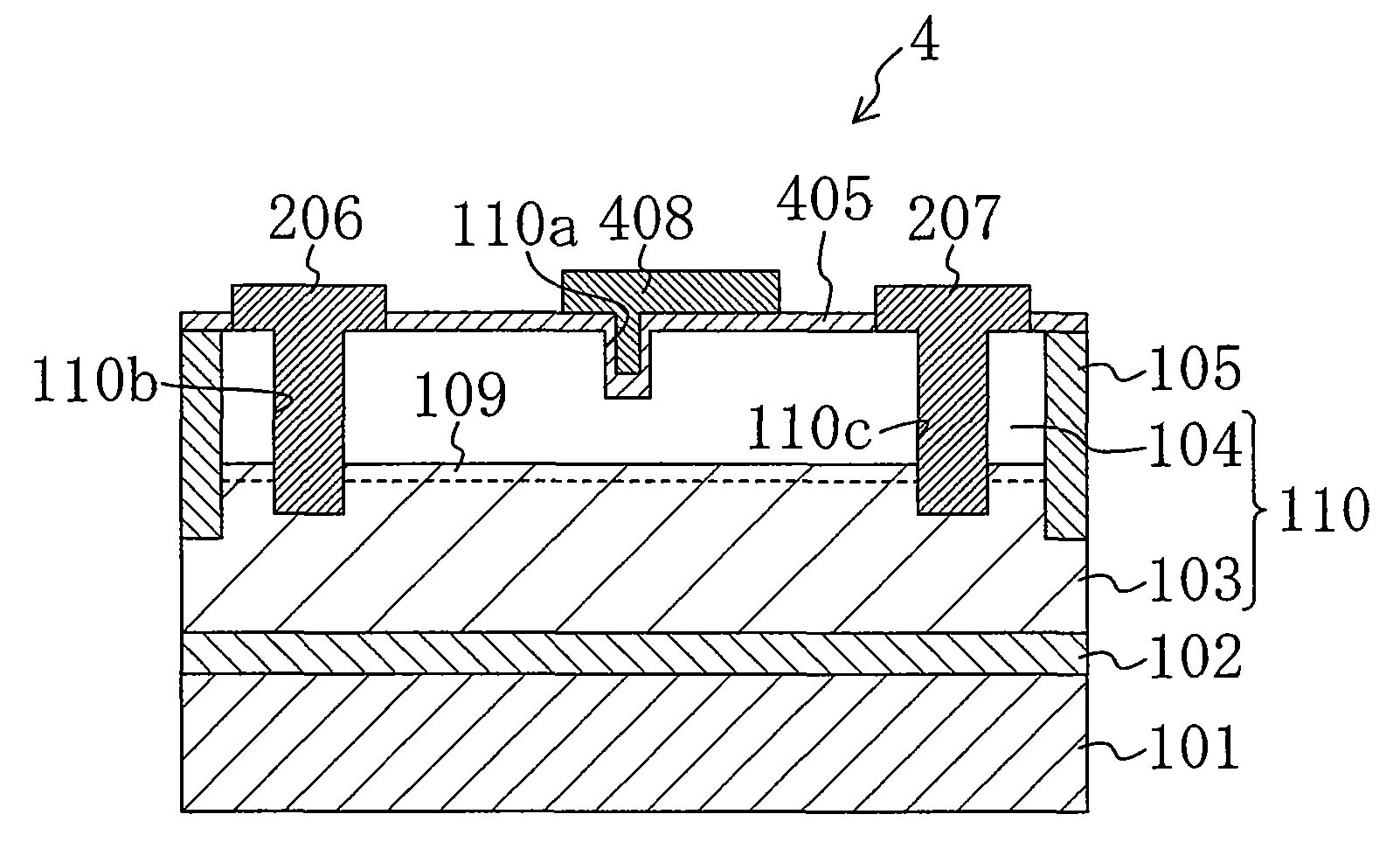

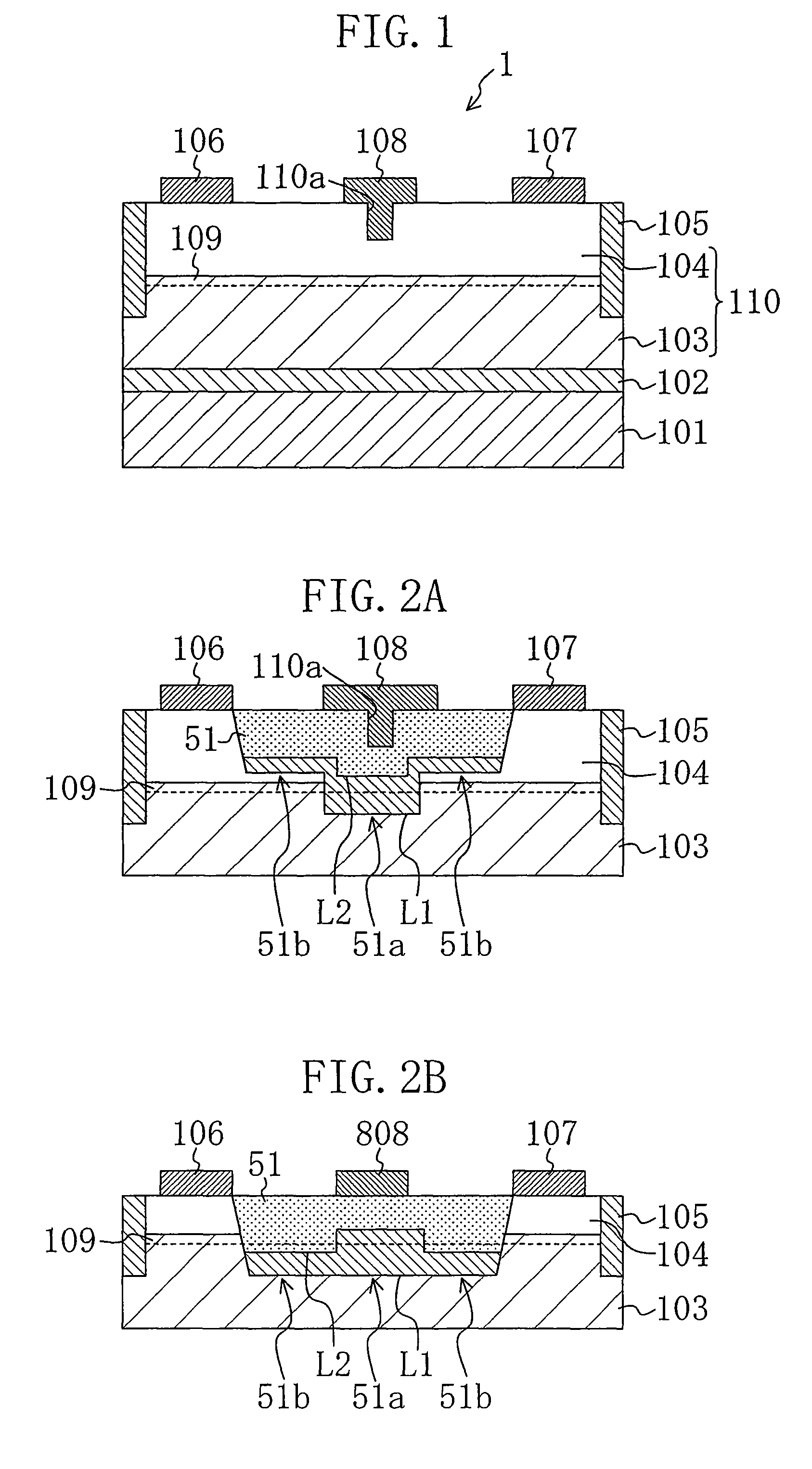

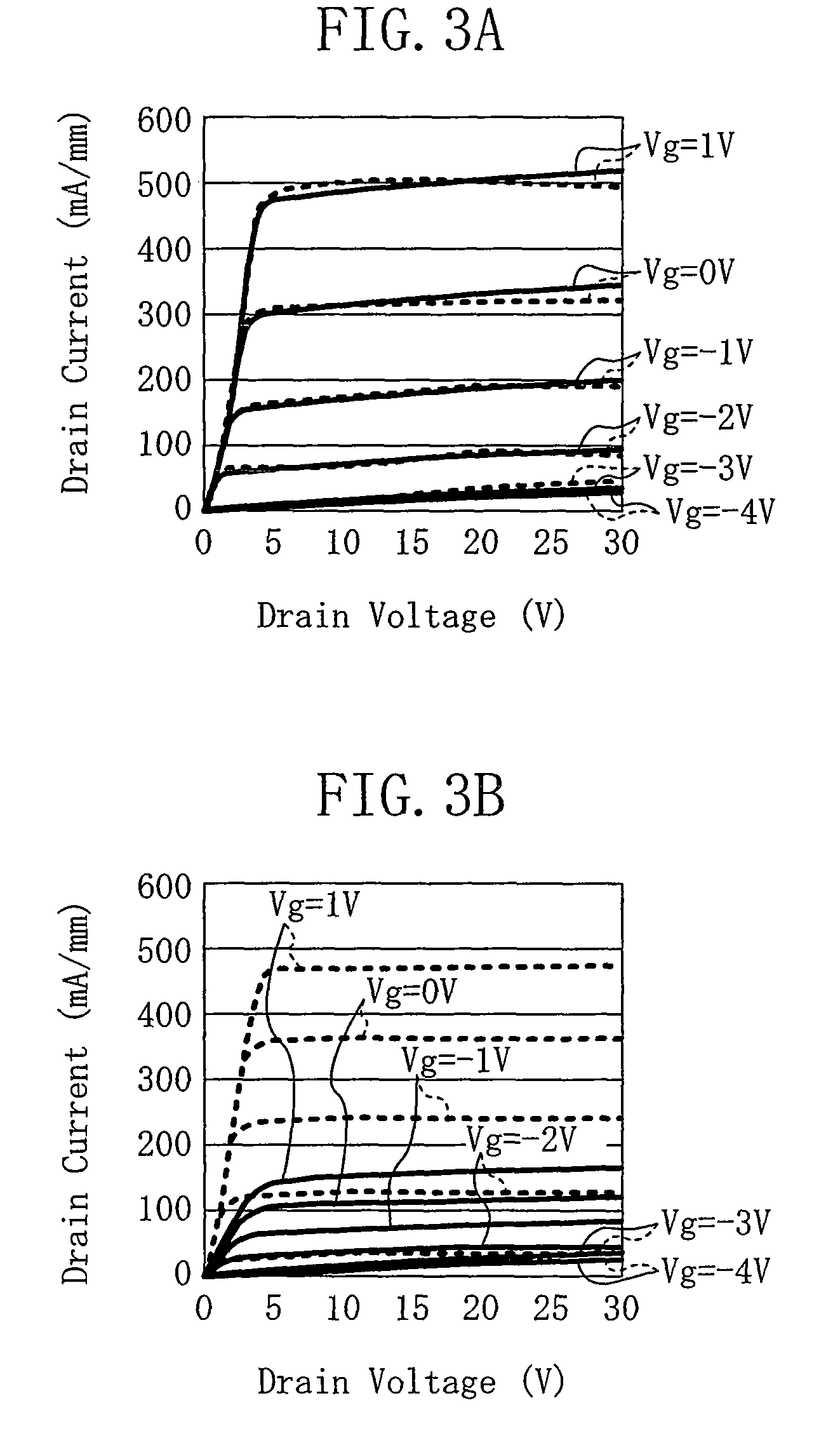

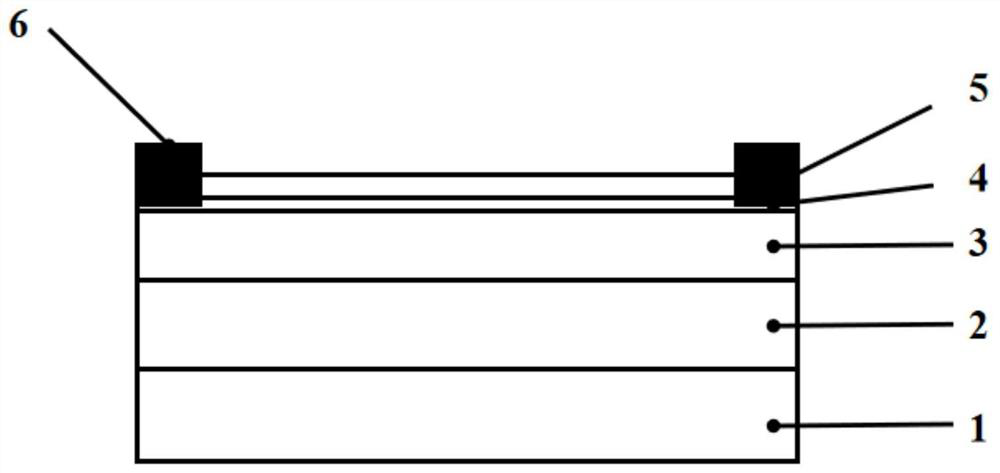

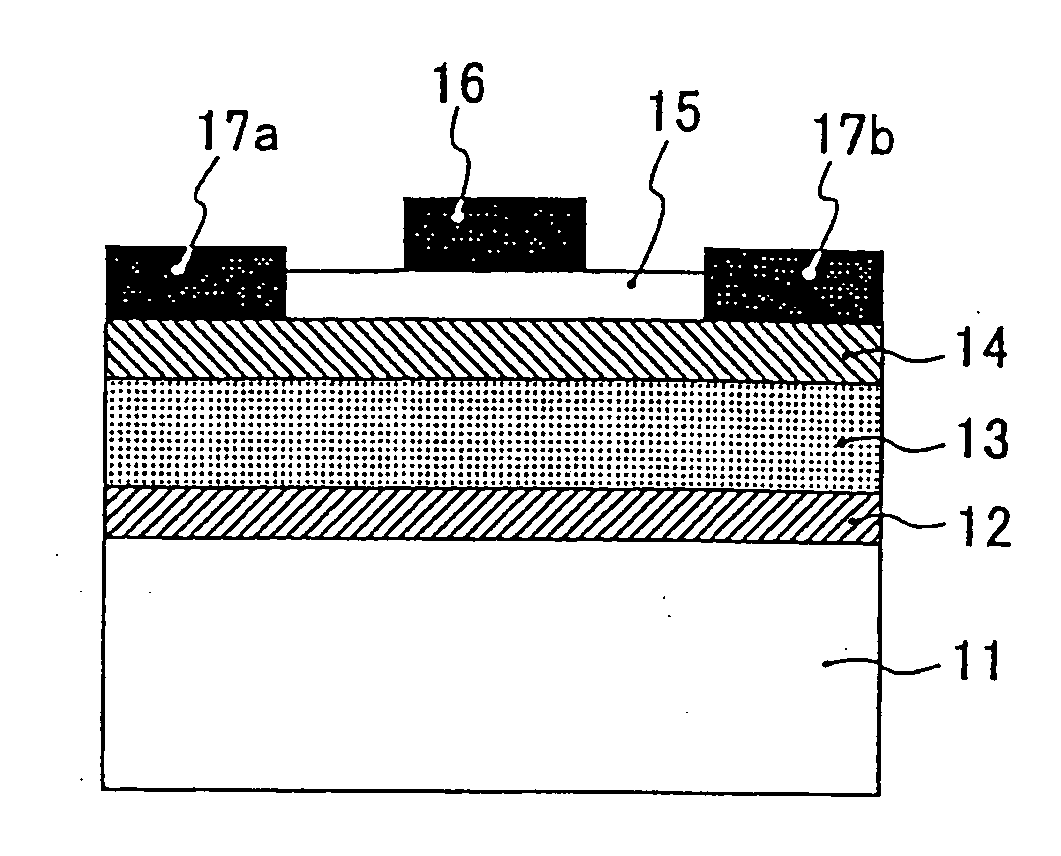

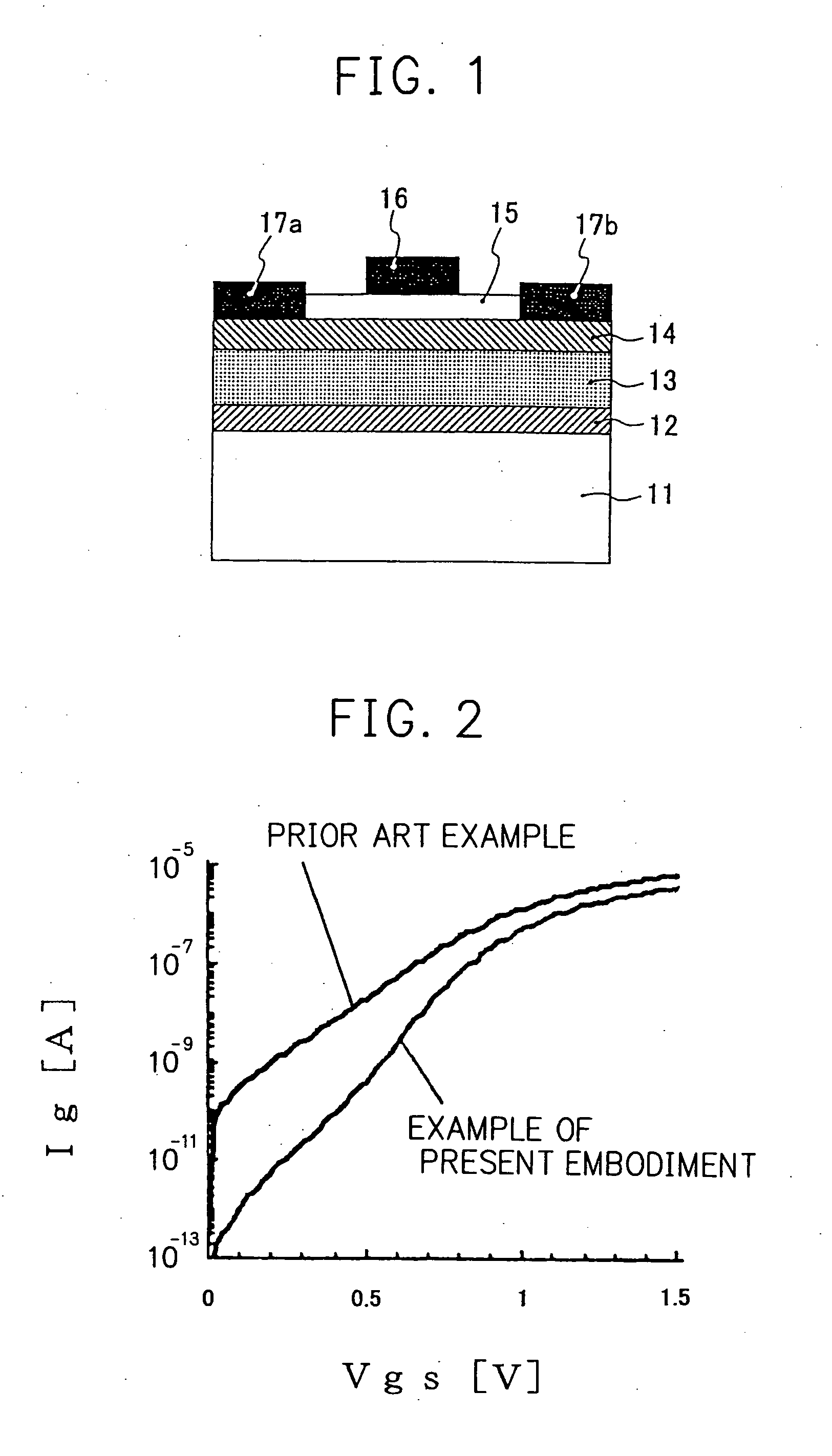

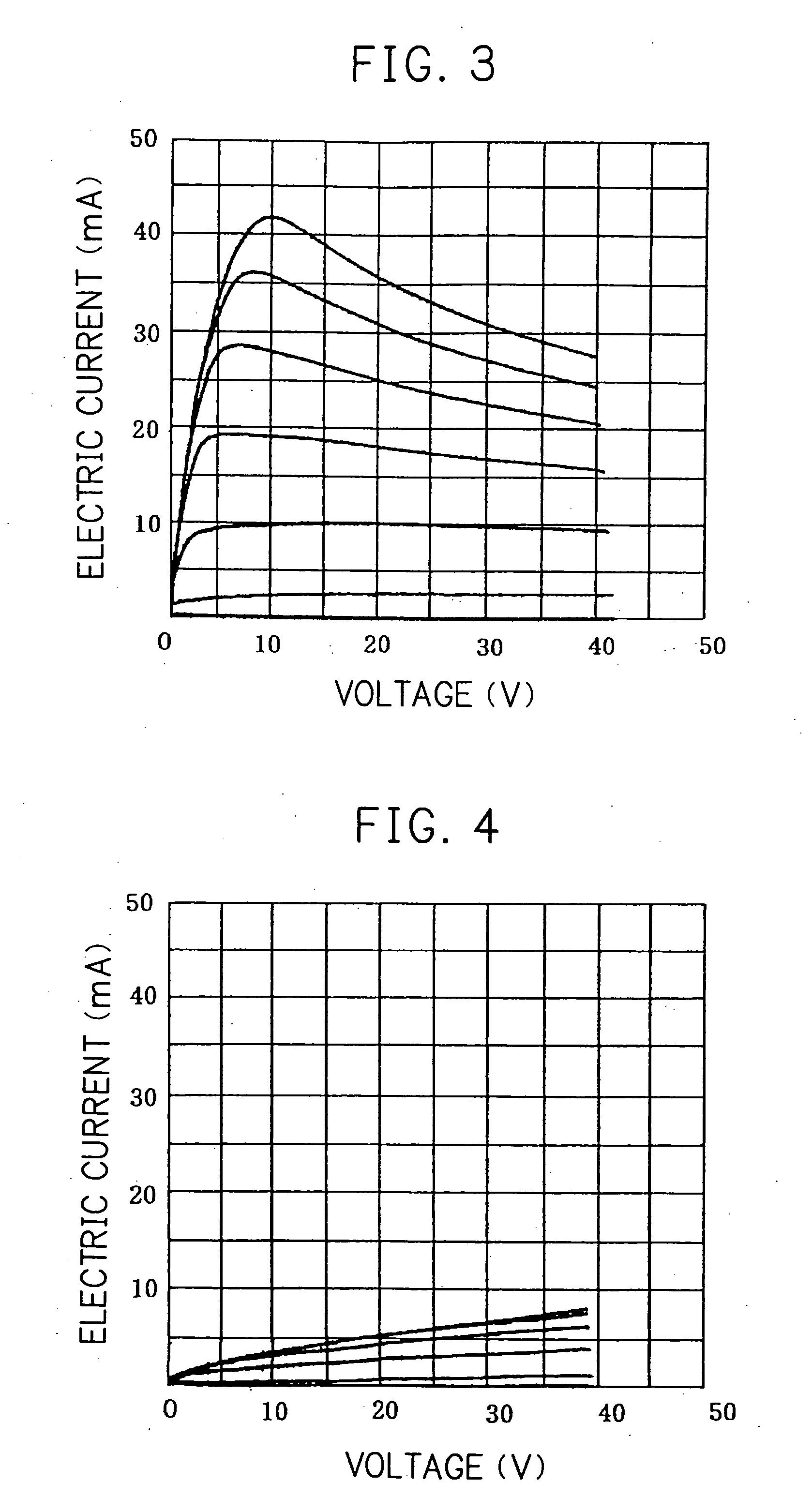

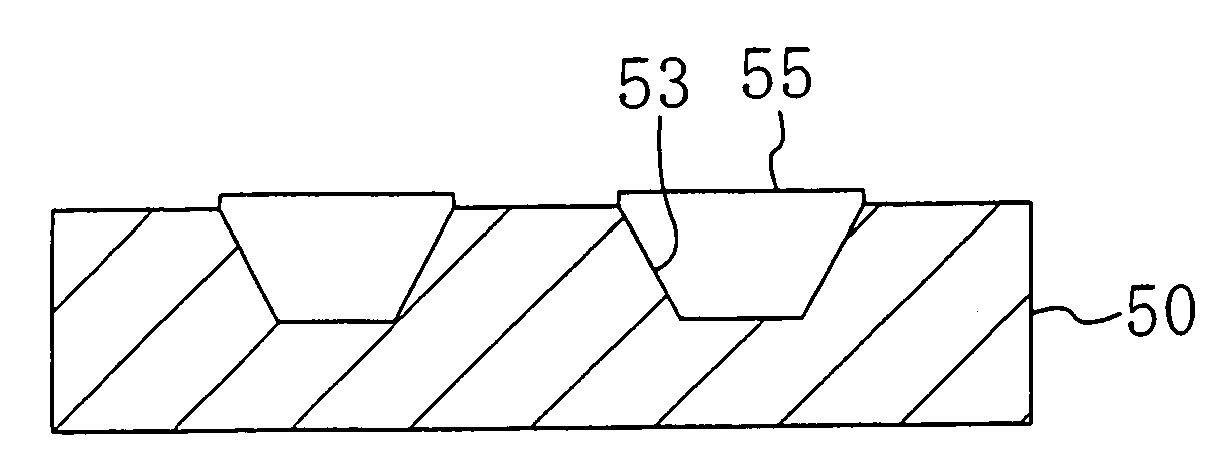

Nitride based semiconductor device with concave gate region

ActiveUS7838904B2Good reproducibilityReduce surface stateTransistorNitride semiconductorsSemiconductor device

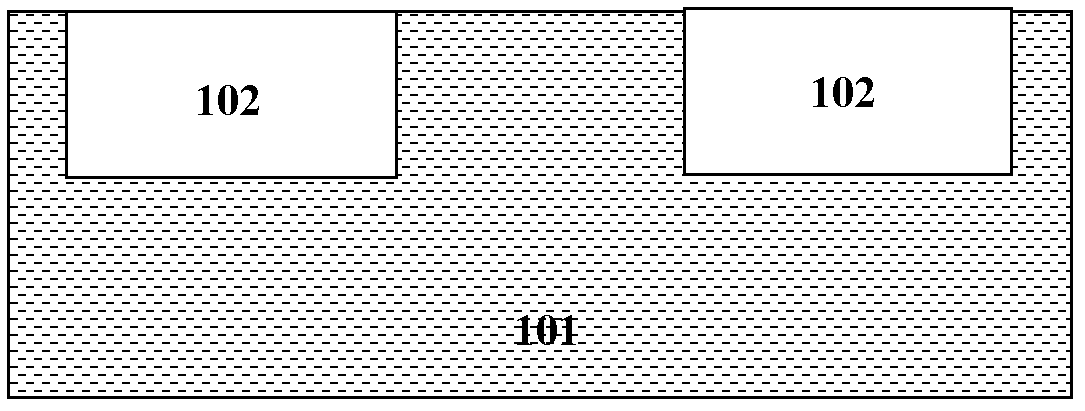

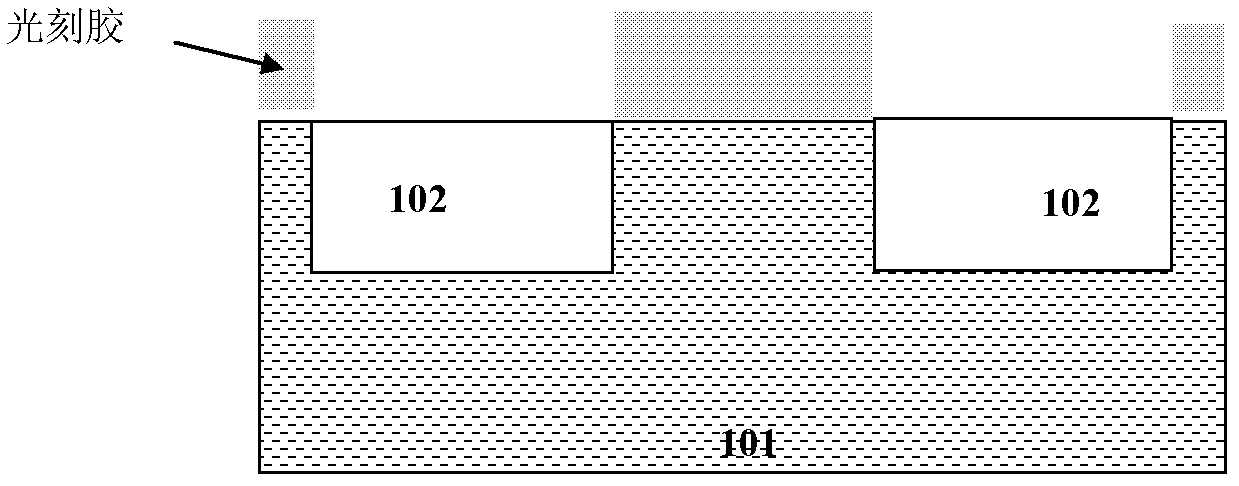

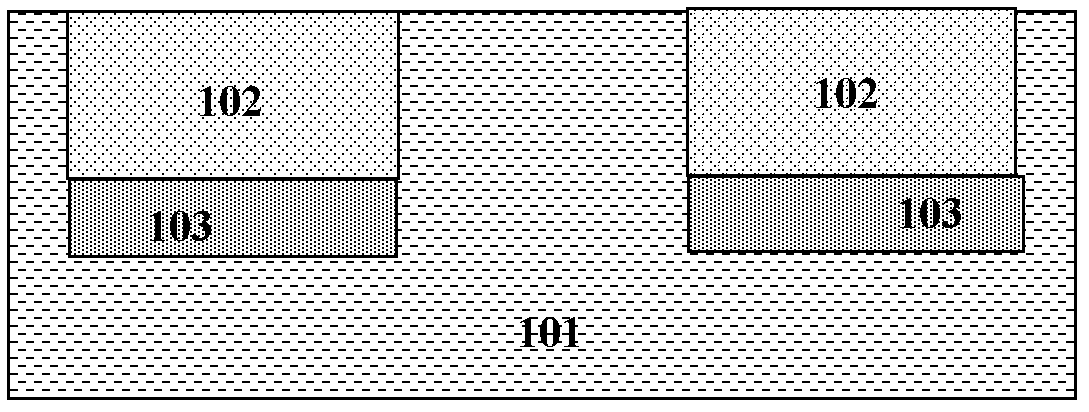

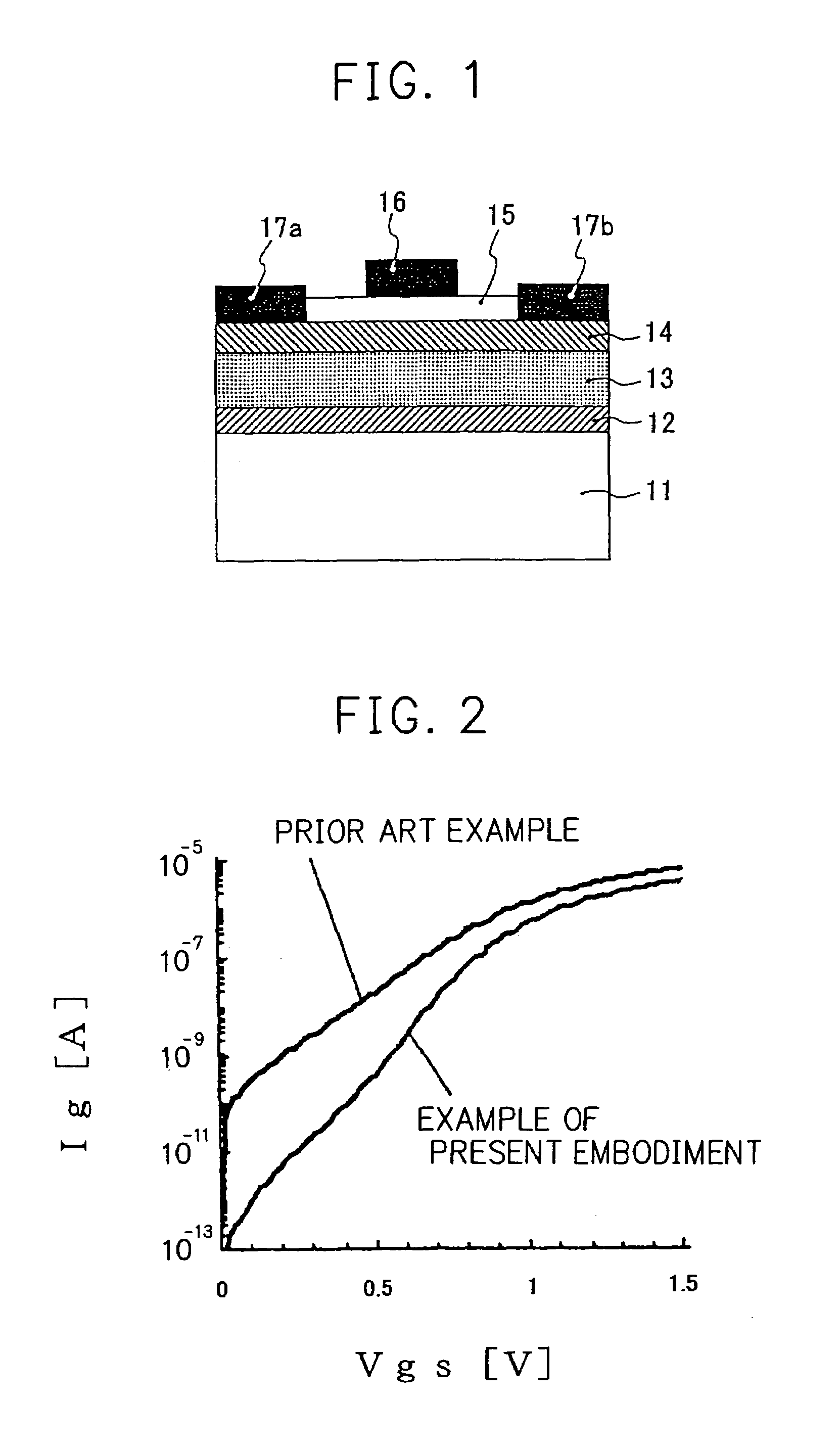

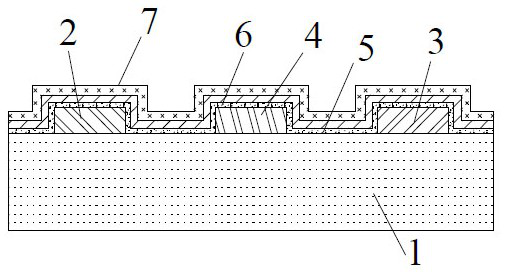

In FET, a second nitride semiconductor layer is provided on a first nitride semiconductor layer, and a source electrode and a drain electrode are each provided to have at least a portion thereof in contact with the second nitride semiconductor layer. A concave portion is formed in the upper surface of the second nitride semiconductor layer to be located between the source electrode and the drain electrode. A gate electrode is provided over the concave portion to cover the opening of the concave portion.

Owner:PANASONIC CORP

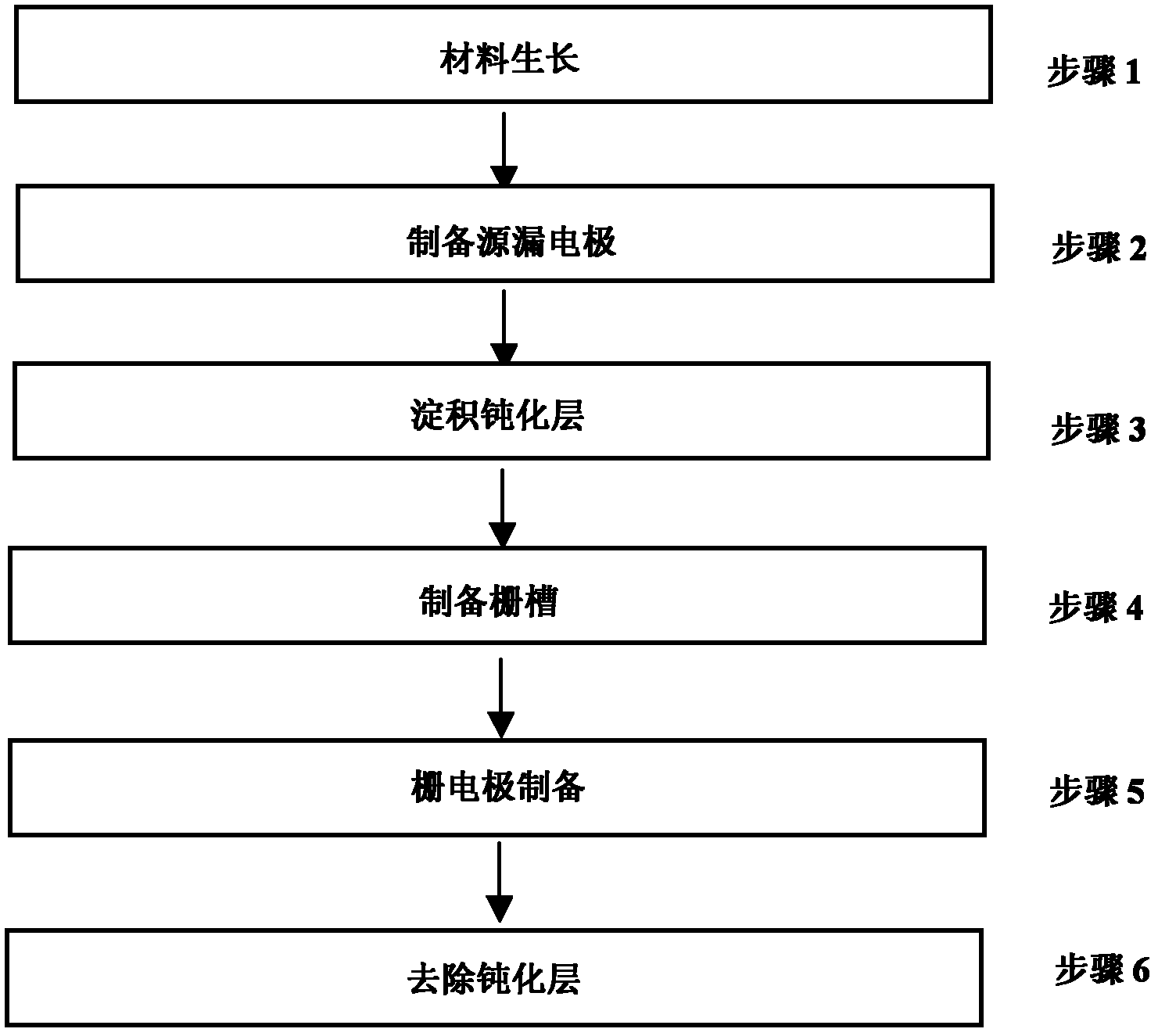

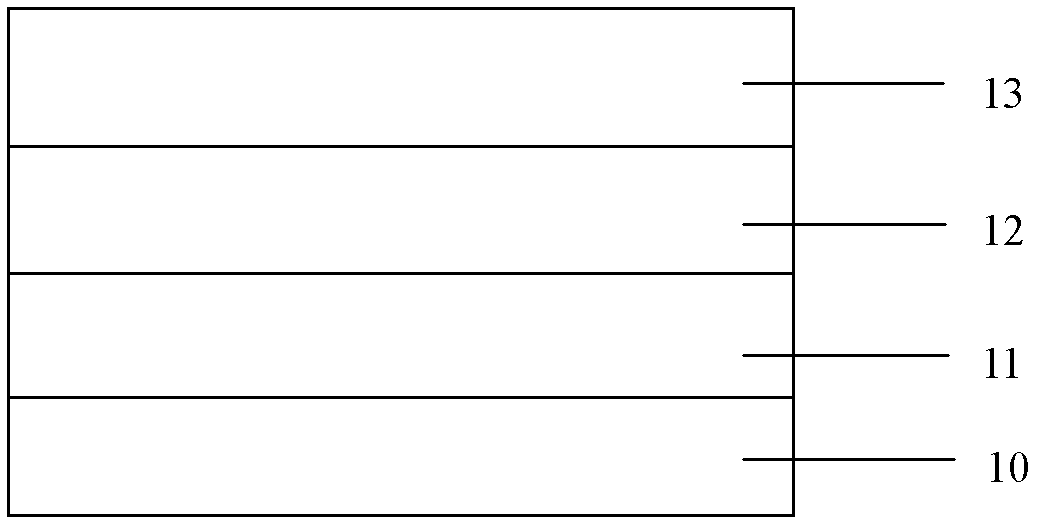

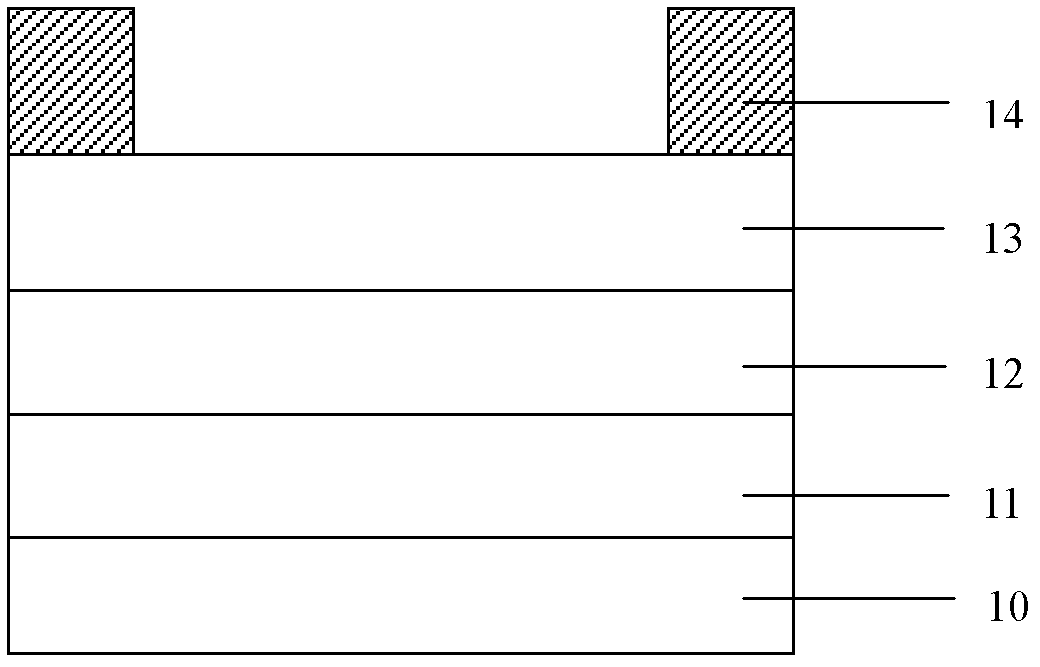

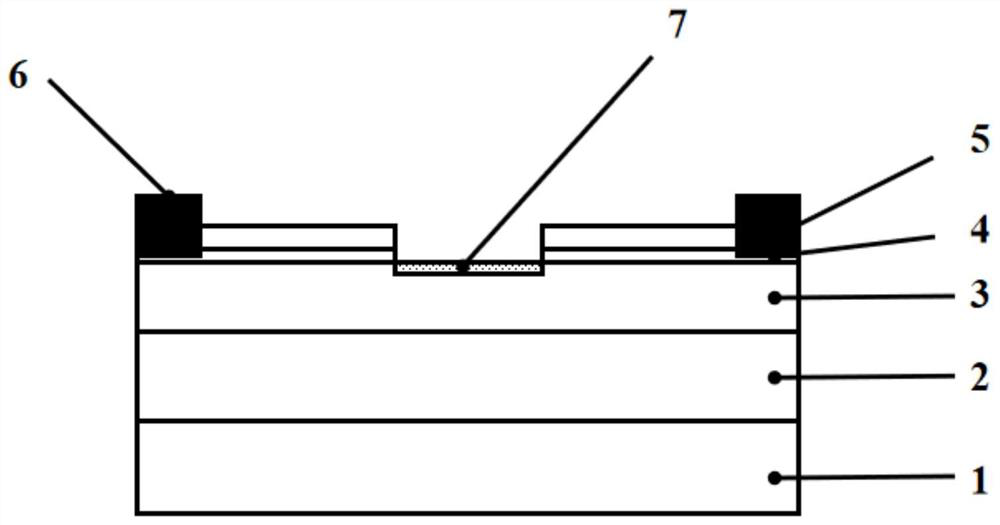

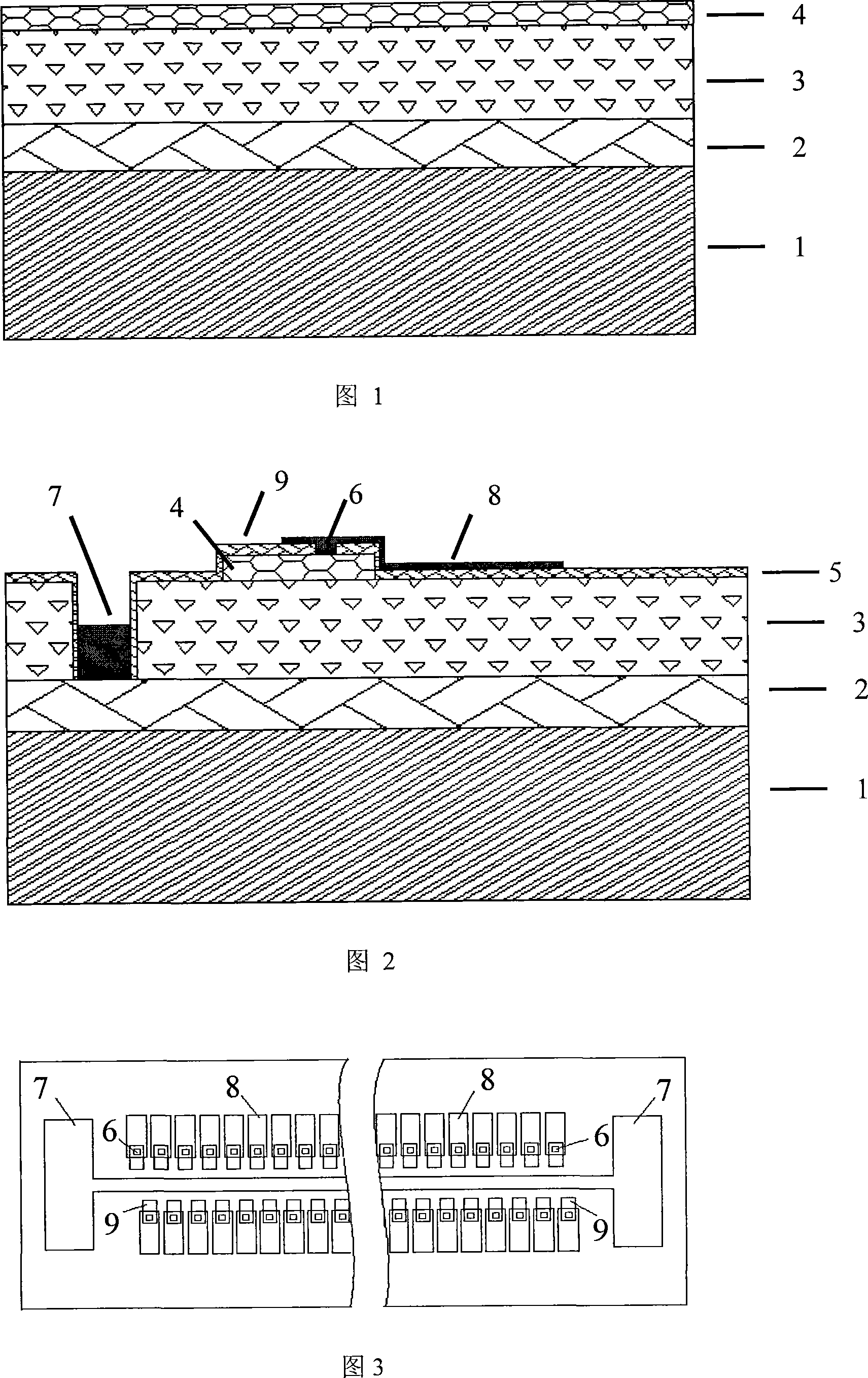

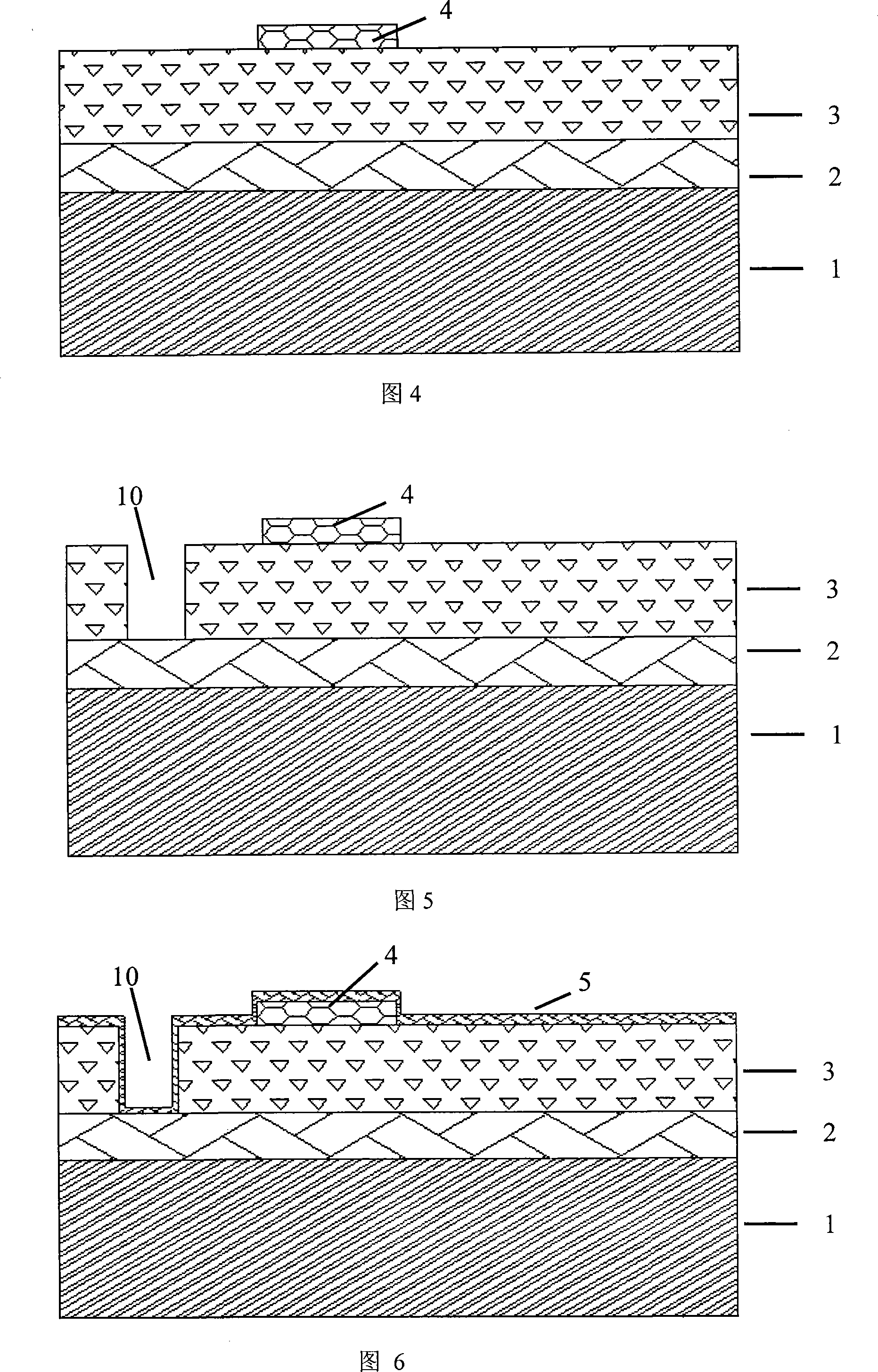

SiO2/SiN double layer passivation layer T-typed grid AlGaN/GaN HEMT and manufacturing method thereof

InactiveCN102437182AIncrease current cutoff frequencyReduce gate parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsPhysics

The invention provides an SiO2 / SiN double layer passivation layer T-typed grid AlGaN / GaN HEMT which comprises: a substrate which is grown with a GaN buffer layer, a GaN intrinsic layer and an AlGaN barrier layer in order; source and drain electrodes which are provided on the barrier layer at two sides; a lower passivation layer which is provided between the source and drain electrodes and is on the barrier layer; an upper passivation layer which is provided between the source and drain electrodes and is on the passivation layer, wherein, a bar shaped grid groove is provided between the lower passivation layer and the upper passivation layer; a gate electrode whose section is a T shape, wherein, the gate electrode is provided in the bar shaped grid groove, and an upper part of the gate electrode is higher than a surface of the upper passivation layer.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

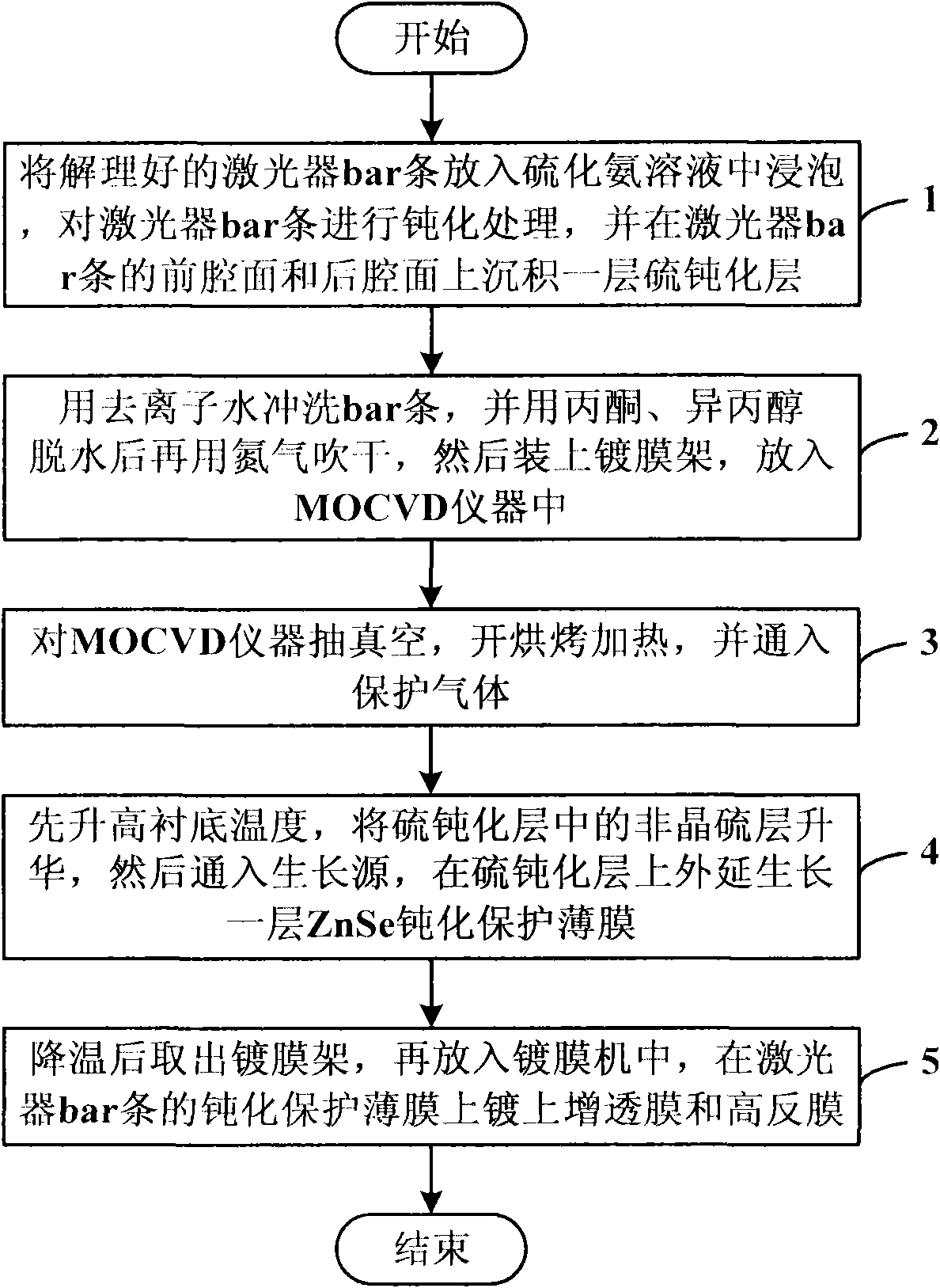

Method for passivating cavity surface of GaAs-based semiconductor laser

InactiveCN101820134AImprove reliabilityEfficient removalLaser detailsSemiconductor lasersShielding gasNitrogen

The invention discloses a method for passivating a cavity surface of a GaAs-based semiconductor laser, and the method comprises the following steps of putting a cleaved laser bar into solution of sulphuret of ammonia to be immersed, carrying out passivation on the laser bar and depositing a sulfur passivation layer on a front cavity surface and a back cavity surface of the laser bar; washing the bar by deionized water, dehydrating by acetone and isopropanol and blow-drying by nitrogen, installing a film plating frame and putting into an MOCVD instrument; vacuumizing the MOCVD instrument, baking to heat and introducing protective gas; increasing the temperature of a substrate, sublimating an amorphous sulfur layer in the sulfur passivation layer, introducing a growth source, and epitaxial-growing a layer of ZnSe passivation protective film on the sulfur passivation layer; and after cooling, taking out the film plating frame and putting into a plating machine, and plating anti-reflection film and high-reflection film on the passivation protective film of the laser bar. The method removes an oxide layer and a surface state on the cavity surface effectively and reduces the damage on the cavity surface.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

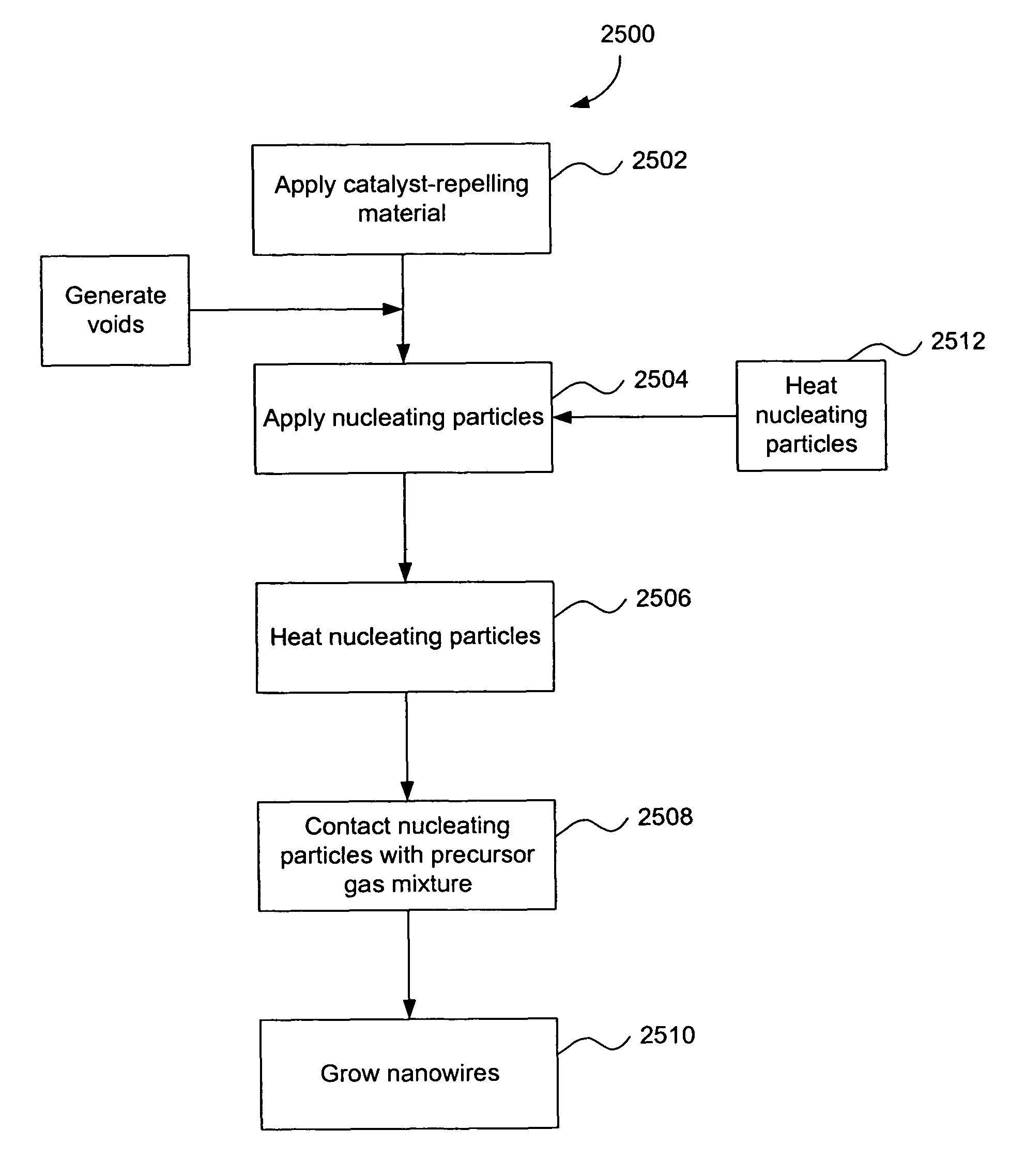

Methods for oriented growth of nanowires on patterned substrates

ActiveUS7951422B2Minimize diffusionIncrease depositionMaterial nanotechnologyPolycrystalline material growthNanowirePatterned substrate

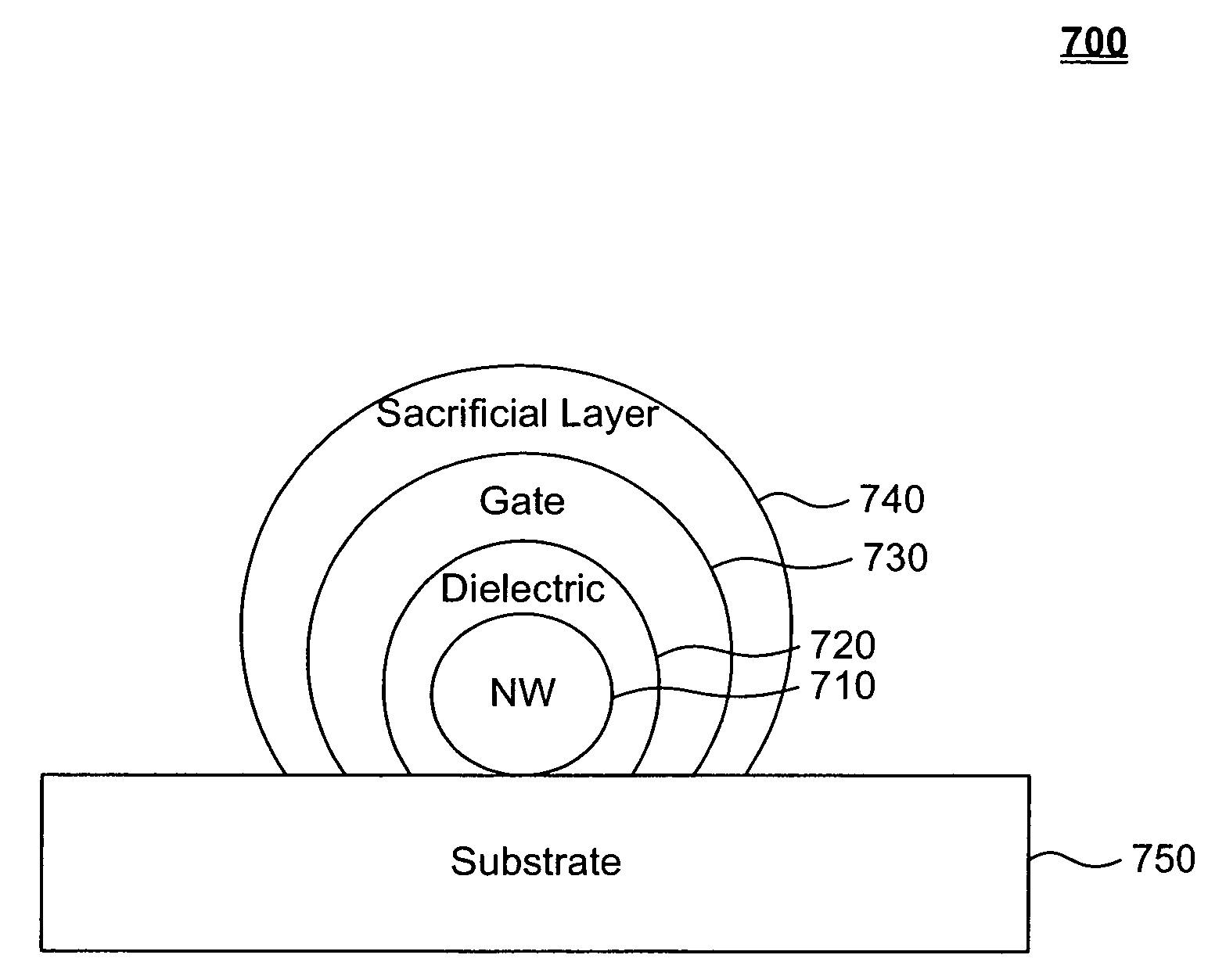

The present invention is directed to systems and methods for nanowire growth and harvesting. In an embodiment, methods for nanowire growth and doping are provided, including methods for epitaxial oriented nanowire growth using a combination of silicon precursors, as well as us of patterned substrates to grow oriented nanowires. In a further aspect of the invention, methods to improve nanowire quality through the use of sacrifical growth layers are provided. In another aspect of the invention, methods for transferring nanowires from one substrate to another substrate are provided.

Owner:ONED MATERIAL INC

Methods for oriented growth of nanowires on patterned substrates

ActiveUS7785922B2Minimize diffusionIncrease depositionPolycrystalline material growthSolid-state devicesNanowirePatterned substrate

The present invention is directed to systems and methods for nanowire growth and harvesting. In an embodiment, methods for nanowire growth and doping are provided, including methods for epitaxial oriented nanowire growth using a combination of silicon precursors, as well as us of patterned substrates to grow oriented nanowires. In a further aspect of the invention, methods to improve nanowire quality through the use of sacrificial growth layers are provided. In another aspect of the invention, methods for transferring nanowires from one substrate to another substrate are provided.

Owner:ONED MATERIAL INC

Passivation Method of Cavity Surface of f-p Cavity Semiconductor Laser

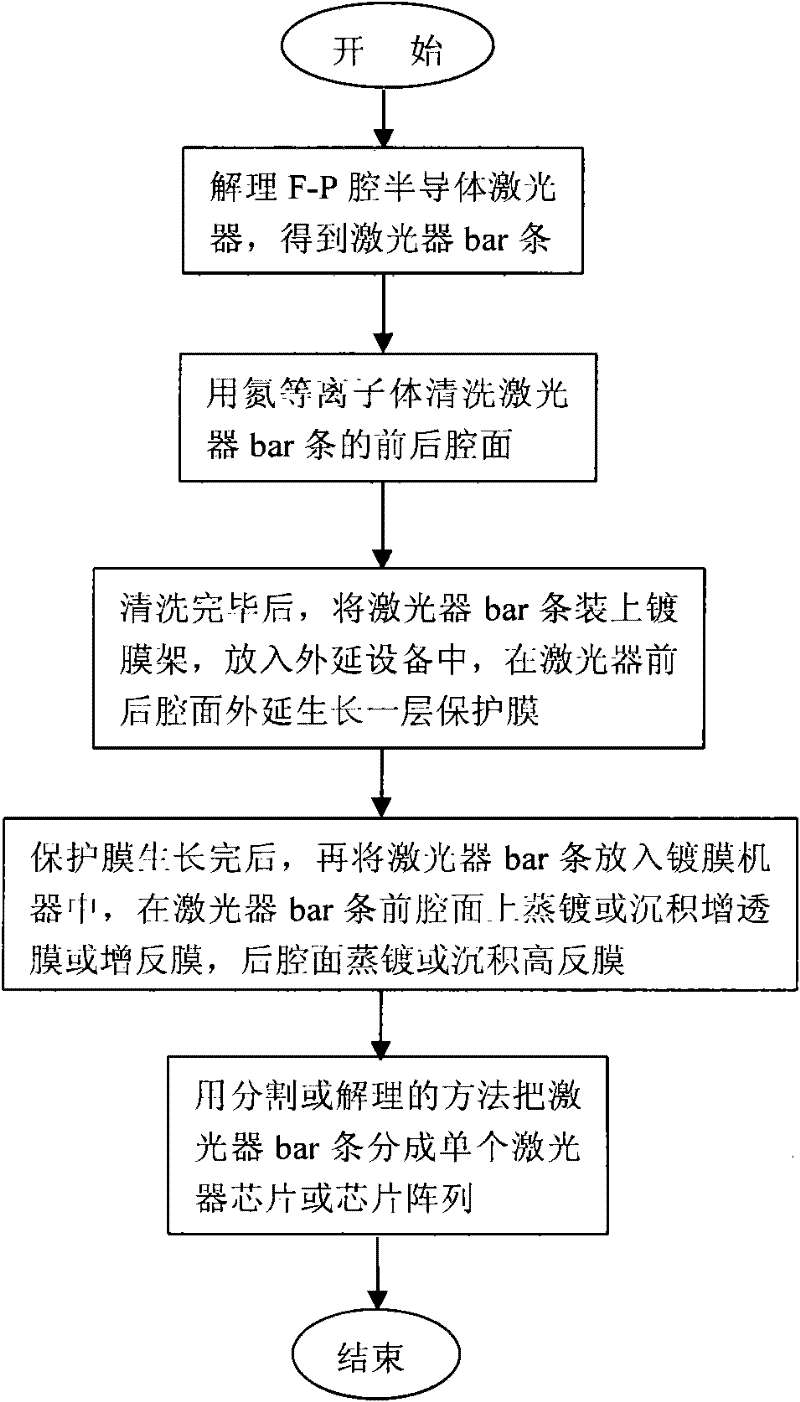

InactiveCN102299479ASuppressed Lasing Threshold Current DensityImproving the Optical Catastrophe Damage Threshold of the Cavity SurfaceLaser optical resonator constructionVacuum evaporation coatingTectorial membraneNitrogen plasma

A method for passivating the cavity surface of an F-P cavity semiconductor laser, comprising the following steps: 1, cleaving the F-P cavity semiconductor laser to obtain a laser bar; 2, cleaning the front and rear cavity surfaces of the laser bar with nitrogen plasma; 3, applying epitaxy Growth technology epitaxially grows a layer of protective film on the front and rear cavity surfaces of the laser; 4. Evaporate or deposit an anti-reflection film on the front cavity surface of the laser bar, and evaporate or deposit a high-reflection film on the rear cavity surface; 5. Use segmentation or solution A reasonable approach divides the laser bar into individual laser chips or chip arrays. The invention can effectively reduce the dangling bonds and surface states at the laser cavity surface, and suppress the light absorption of the laser cavity surface; at the same time, the epitaxially grown thin film is a wide bandgap material, which absorbs very little outgoing light, and can greatly suppress the laser cavity The light absorption at the surface and the resulting temperature rise improve the stability and reliability of the laser.

Owner:苏州纳睿光电有限公司

Light anode for dye sensitization solar battery and preparation method thereof

InactiveCN101354968AReduce lossesInhibition of reverse recombinationLight-sensitive devicesSolid-state devicesElectrical batterySolar battery

The invention relates to a dye sensitization solar cell light anode and a preparation method thereof. The light anode is characterized in that chemical modification for the dye sensitization solar cell light anode improves the sensitization effect of the dye on the light anode, thereby improving the photoelectric conversion efficiency of the cell. The concrete realization method is to carry out the surface modification of light anode nano crystal through nano SiO2, carry out functionalization, and absorb the dye. The modification of a nano SiO2 layer inhibits the surface state of a nano crystalline film and improves the photoelectric conversion performance of the cell; and simultaneously the surface functionalization increases the absorption amount of the dye, thereby effectively improving the photoelectric conversion efficiency of the solar cell.

Owner:IRICO

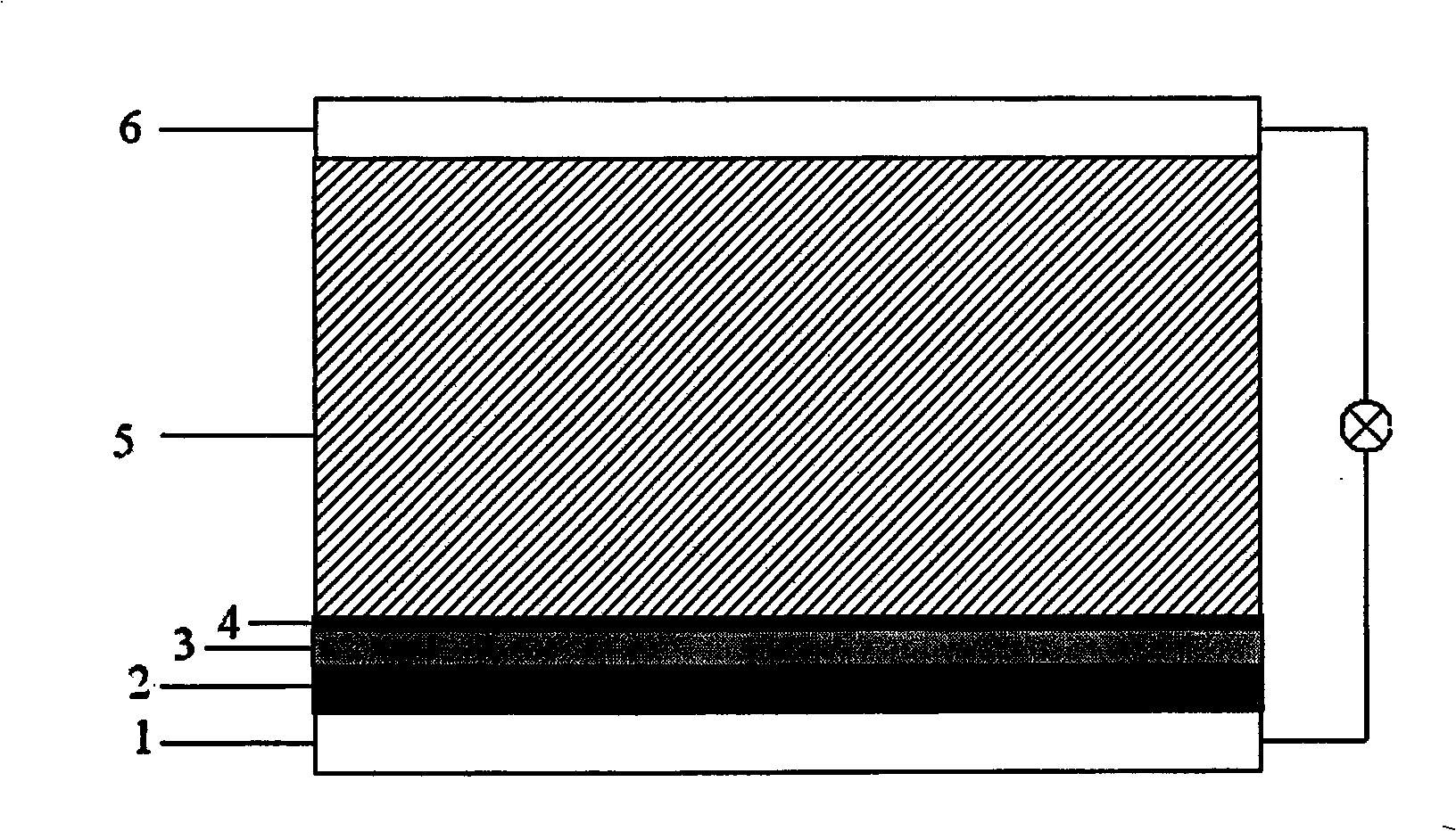

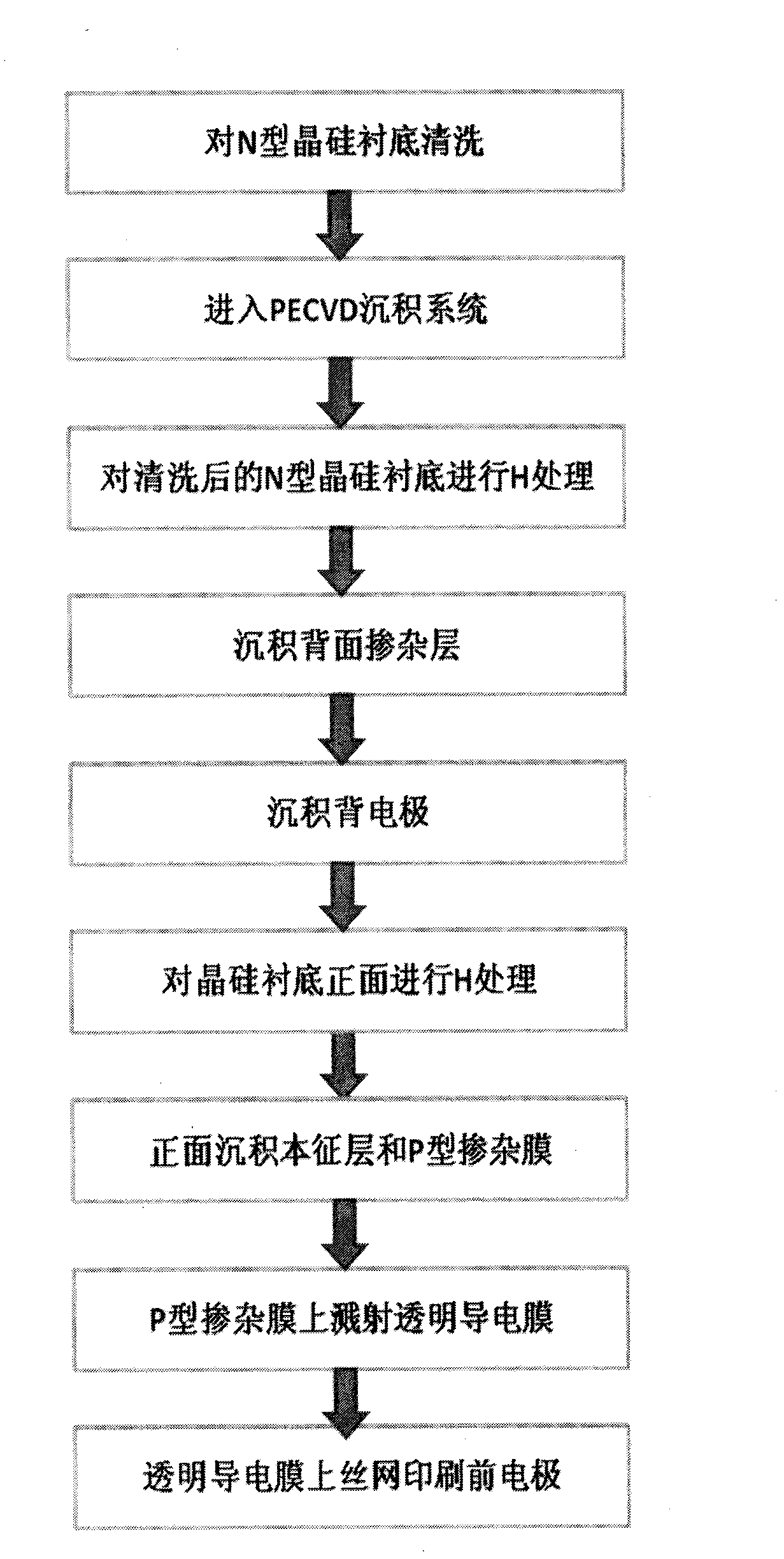

Interface treatment technology for hetero junction solar cell

InactiveCN102386253ANo damagePromote productionFinal product manufactureChemical vapor deposition coatingGas phaseDangling bond

The invention discloses an interface treatment technology for a hetero junction solar cell. The method is characterized in that: the technology can be applied to the manufacturing of a thin film / crystalline silicon hetero junction solar cell, reaction gases can be ionized by utilizing a plasma enhanced chemical vapor deposition (PECVD) system or a hotwire chemical vapor deposition (HWCVD) system to generate H, and the H is transported to a crystalline silicon substrate by a gas phase and reacted with the surface of crystalline silicon to effectively passivate defect states such as unsaturated dangling bonds and the like on the surface of the crystalline silicon, reduce hetero junction interface recombination and facilitate improvement in the overall performance of the hetero junction solar cell.

Owner:CHANGZHOU HETE PHOTOELECTRIC

Methods for oriented growth of nanowires on patterned substrates

ActiveUS20080038521A1Same lengthMinimize diffusionPolycrystalline material growthSolid-state devicesNanowirePatterned substrate

The present invention is directed to systems and methods for nanowire growth and harvesting. In an embodiment, methods for nanowire growth and doping are provided, including methods for epitaxial oriented nanowire growth using a combination of silicon precursors, as well as us of patterned substrates to grow oriented nanowires. In a further aspect of the invention, methods to improve nanowire quality through the use of sacrifical growth layers are provided. In another aspect of the invention, methods for transferring nanowires from one substrate to another substrate are provided.

Owner:ONED MATERIAL INC

Methods for oriented growth of nanowires on patterned substrates

ActiveUS20080038520A1Minimize diffusionIncrease depositionMaterial nanotechnologyPolycrystalline material growthNanowirePatterned substrate

The present invention is directed to systems and methods for nanowire growth and harvesting. In an embodiment, methods for nanowire growth and doping are provided, including methods for epitaxial oriented nanowire growth using a combination of silicon precursors, as well as us of patterned substrates to grow oriented nanowires. In a further aspect of the invention, methods to improve nanowire quality through the use of sacrifical growth layers are provided. In another aspect of the invention, methods for transferring nanowires from one substrate to another substrate are provided.

Owner:ONED MATERIAL INC

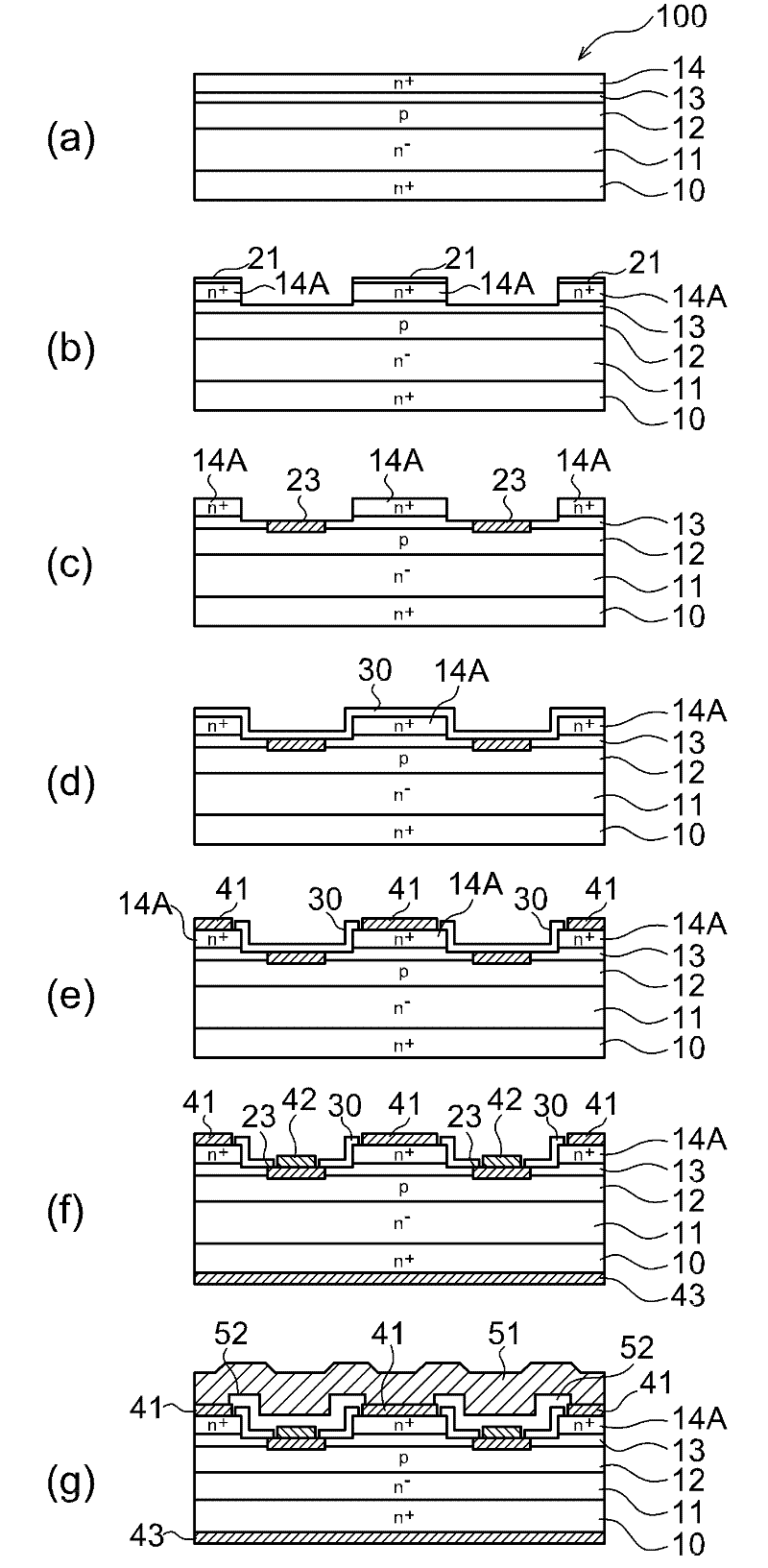

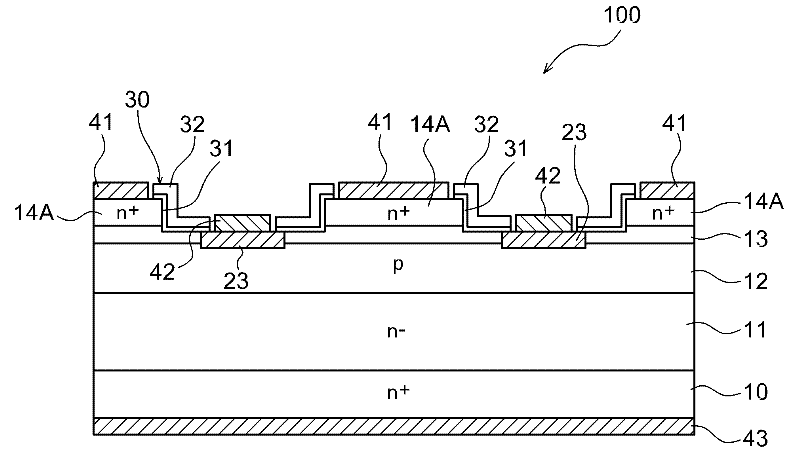

Bipolar semiconductor device and method for manufacturing same

InactiveCN102132388AIncrease the current amplification rateSimple processTransistorSemiconductor/solid-state device detailsSemiconductor componentsNitrogen

Disclosed is a bipolar semiconductor device which is capable of reducing the surface state density of a bipolar transistor and increasing the current gain of the transistor, thereby improving the transistor performance. A bipolar semiconductor device (100) has a surface protective film (30) on the surface of a semiconductor element. The surface protective film is composed of a thermal oxide film (31) formed on the surface of the semiconductor element, and a deposited oxide film (32) formed on the thermal oxide film. The deposited oxide film contains at least one of hydrogen element and nitrogen element in an amount of not less than 1018 cm-3.

Owner:HONDA MOTOR CO LTD +1

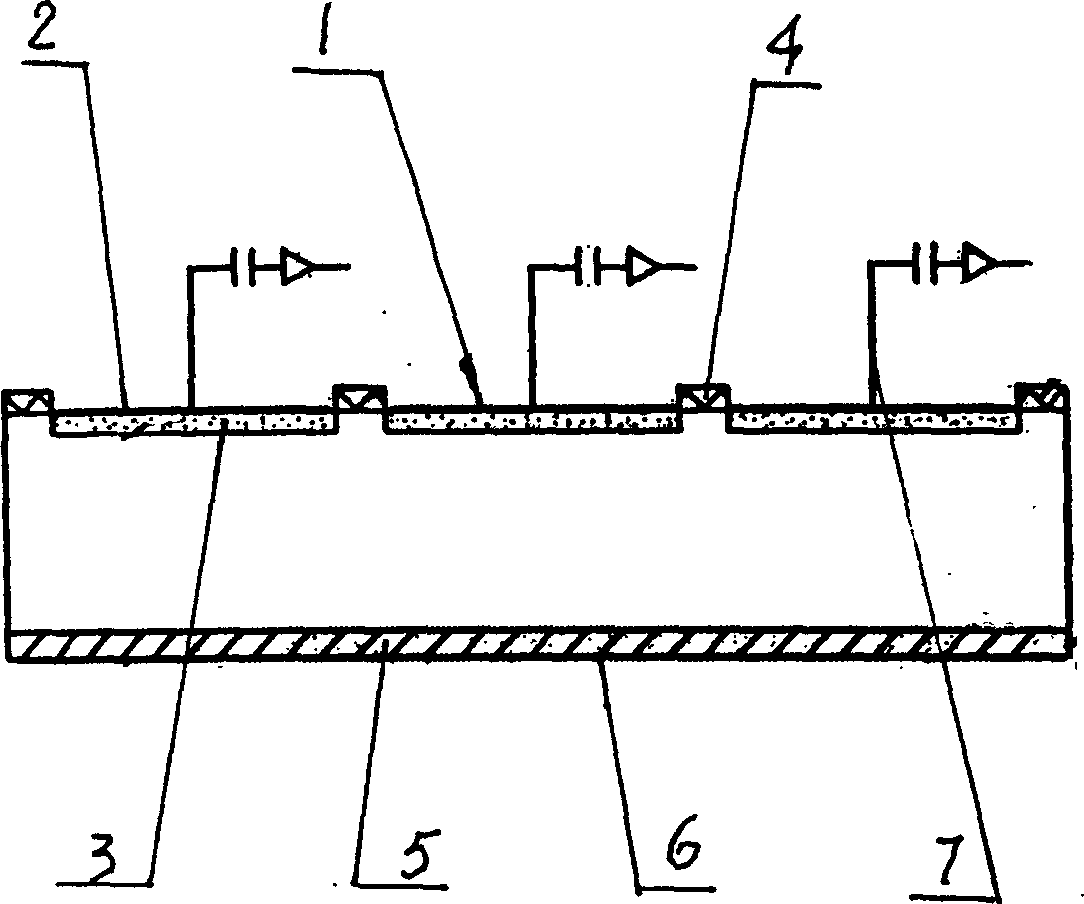

Nuclear radiation detector and producing technology thereof

InactiveCN1773309AReduce dark currentExcellent electrical and detection characteristicsRadiation intensity measurementImage resolutionHigh energy

The present invention mainly relates to a nuclear radiation detector, in particular, it relates to a position sensitive detector used in the high-energy physics and nuclear physics and its production process. Said detector includes silicon substrate, N-type, it is mainly characterized by that it also includes detection window, it is formed from mutually-parallelized detection windows, it has B+ doped region, forming PN Gunction, on it an Al-layer is set, and is equipped with a lead; between two windows an insulated separating zone is set; back surface of silicon substrate has P- doped region, forming N+ ohmic contact, on it an Al-layer is coated to form back electrode. Said invention also provides the concrete steps of its production method.

Owner:INST OF MODERN PHYSICS CHINESE ACADEMY OF SCI

Gallium nitride enhanced HEMT device and preparation method thereof

PendingCN112086362AImprove stabilityImprove reliabilityMaterial nanotechnologySemiconductor/solid-state device manufacturingHigh concentrationSemiconductor materials

The invention belongs to the technical field of semiconductor materials and particularly relates to a gallium nitride enhanced HEMT device and a preparation method thereof. According to the method, ICP (Inductively Coupled Plasma) is adopted to optimize a gallium nitride conductive channel, oxygen plasma treatment is performed before an insulating dielectric layer is deposited, then in-situ annealing is performed, and a crystal GaON nano-phase is generated in a gate region to serve as an optimized channel layer. The method can effectively reduce the surface state of high-concentration impurities introduced by the inner wall of the groove due to the etching process and the morphology of the rough inner wall, improves the stability and reliability of the device, improves the breakdown voltage and on / off current ratio of the device, and further improves the working performance of the device.

Owner:深圳市红与蓝企业管理中心(有限合伙)

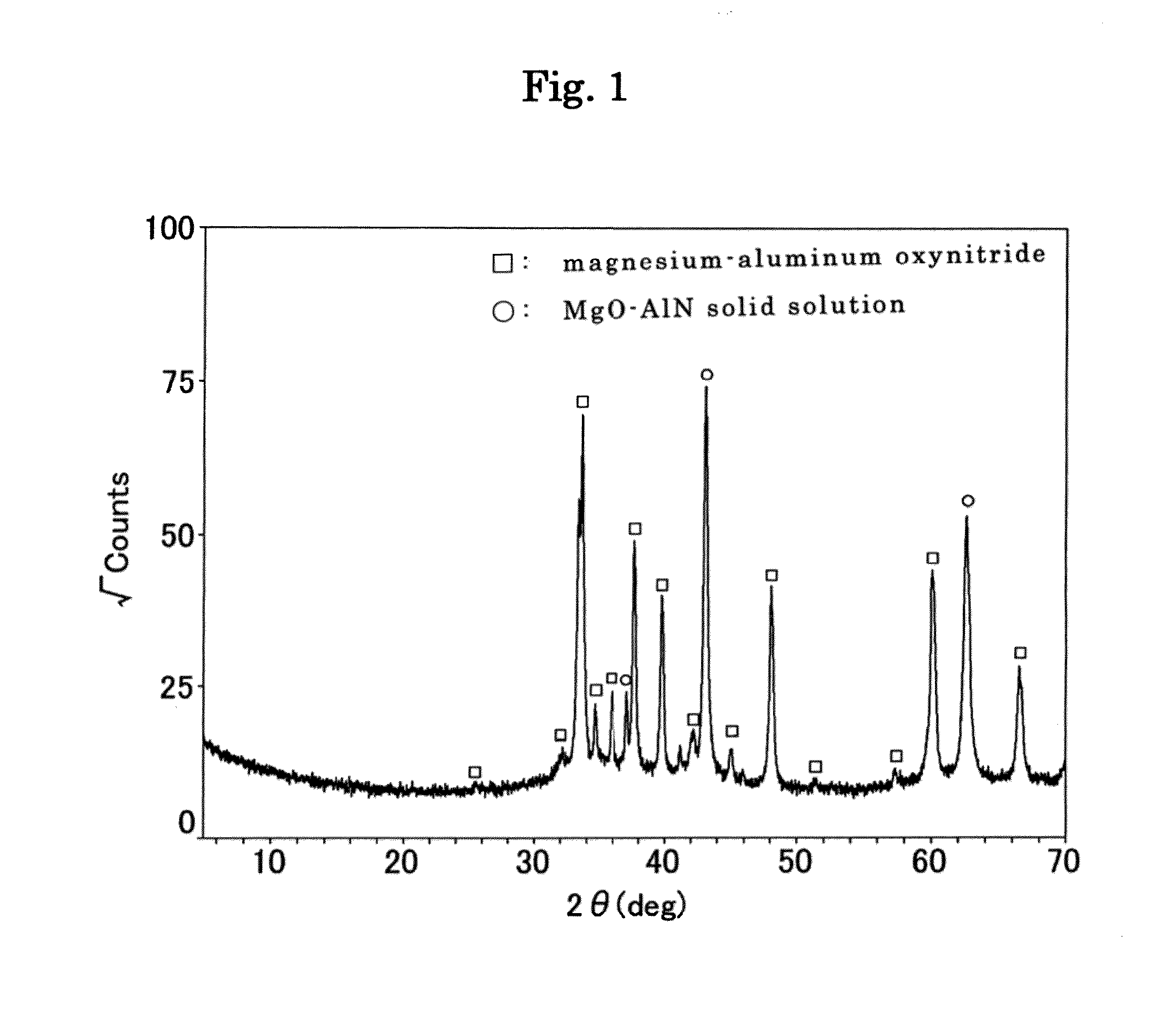

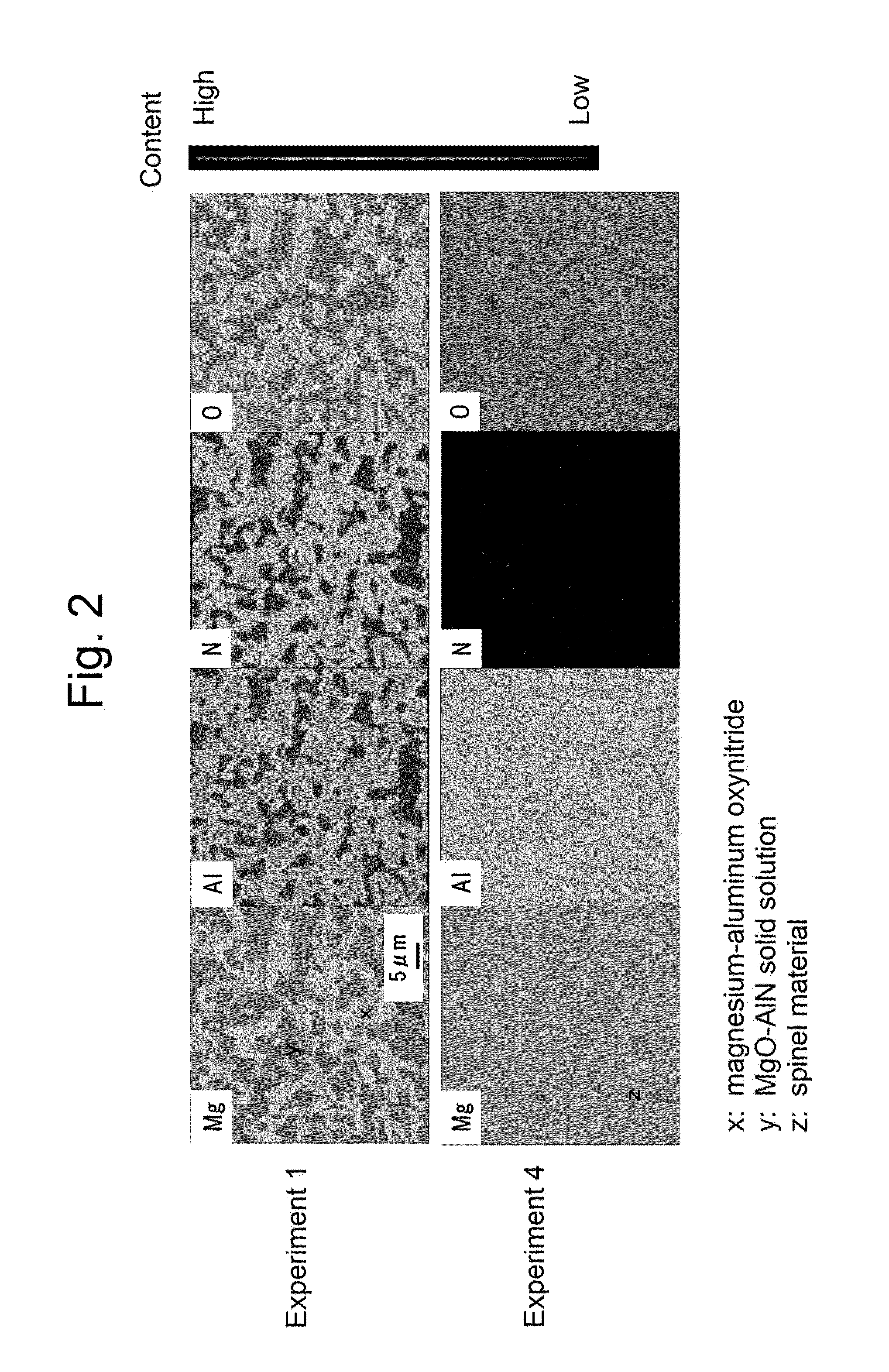

Heating device

ActiveUS20130228565A1Improve uniformityMaintain consistencyVacuum evaporation coatingSemiconductor/solid-state device manufacturingSusceptorNitrogen

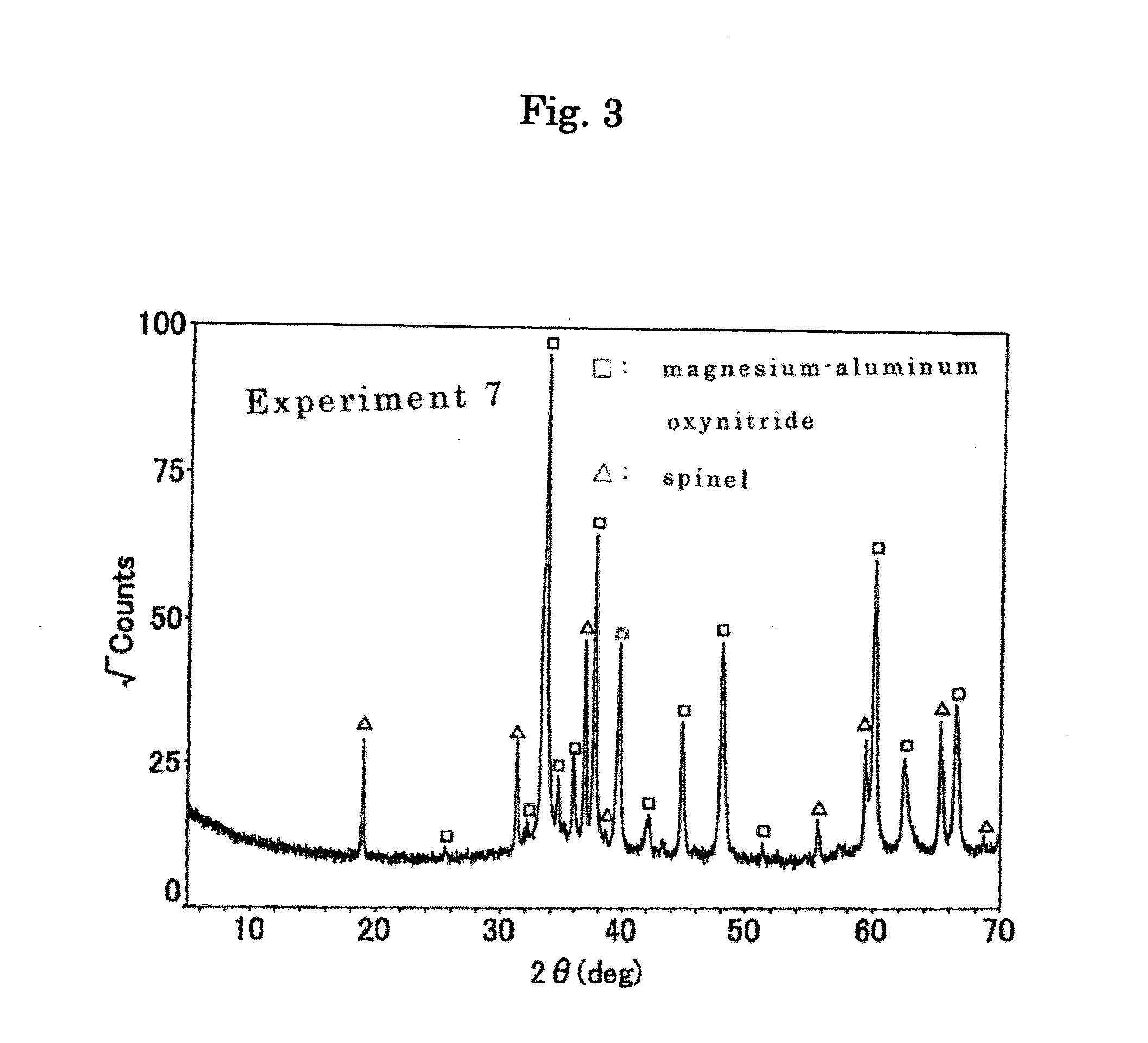

A heating apparatus 1A includes a susceptor part 9A having a heating face 9a of heating a semiconductor W, and a ring shaped part 6A provided in the outside of the heating face 9a. The ring shaped part 6A is composed of a ceramic material comprising magnesium, aluminum, oxygen and nitrogen as main components. The ceramic material comprises a main phase comprising magnesium-aluminum oxynitride phase exhibiting an XRD peak at least in 2θ=47 to 50° taken by using CuKα ray.

Owner:NGK INSULATORS LTD

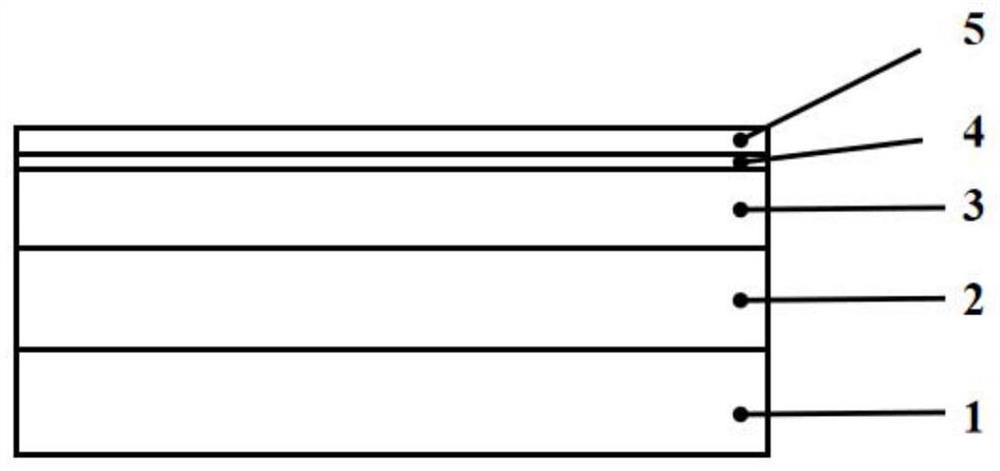

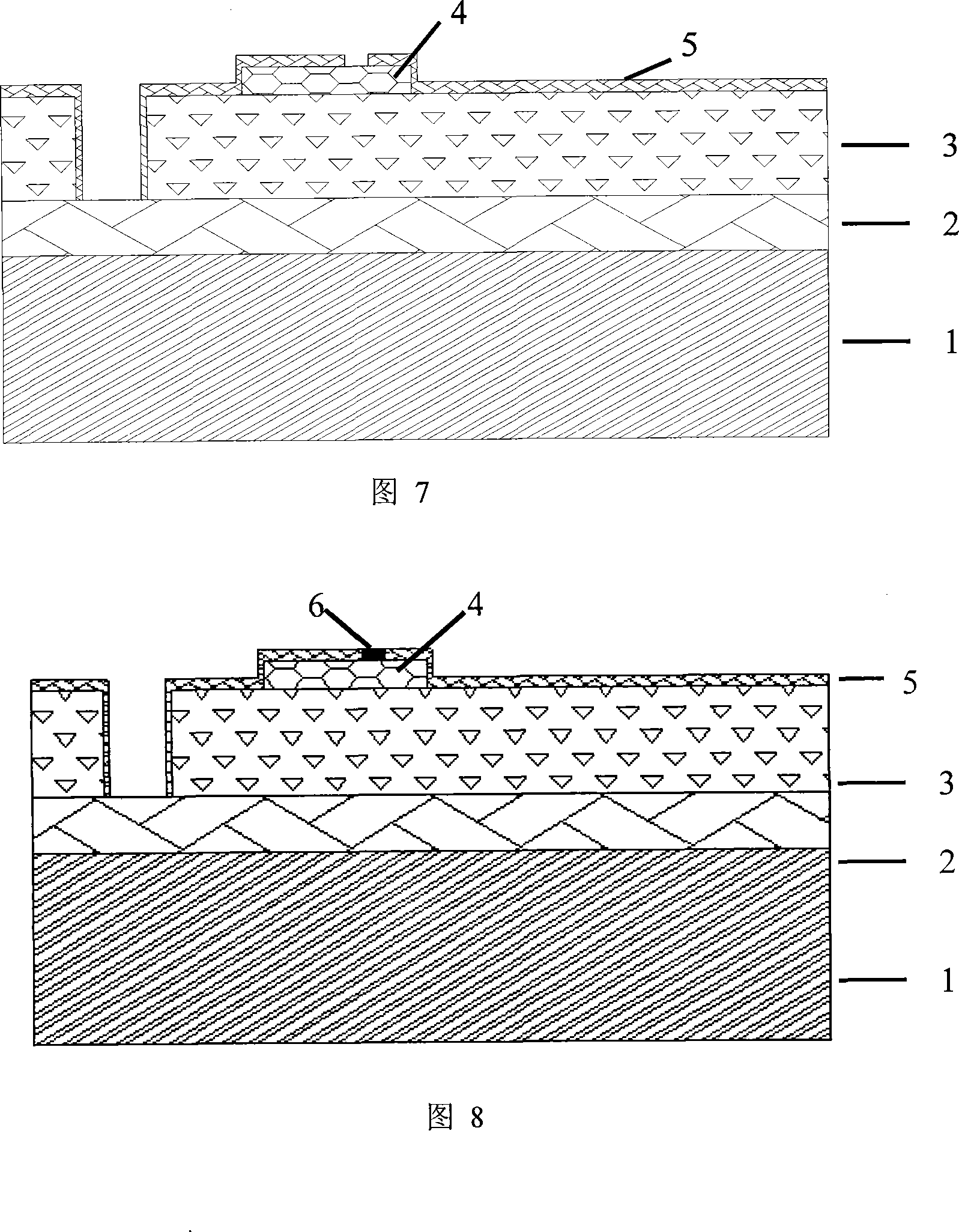

Gallium nitride power device with multi-field plate structure, and preparation method thereof

ActiveCN111370483AImprove pressure resistanceImprove breakdown resistanceEfficient power electronics conversionSemiconductor/solid-state device manufacturingElectrode insertionEngineering

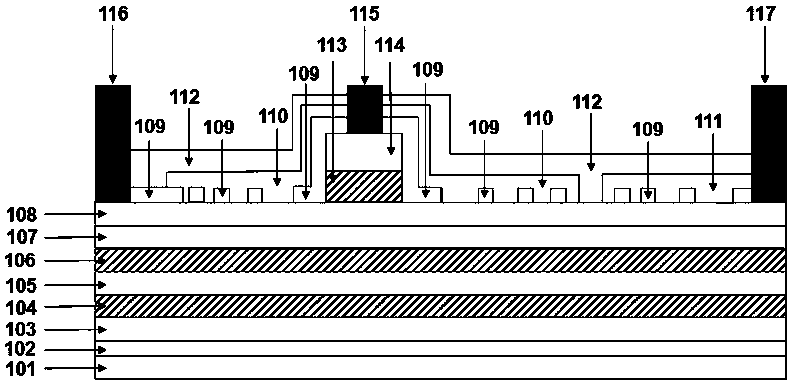

The invention discloses a gallium nitride power device with a multi-field plate structure. The gallium nitride power device is sequentially provided with a substrate, a nucleating layer, a buffer layer, a first insertion layer, a first GaN layer, a second insertion layer, a second GaN layer, an AlGaN barrier layer, a passivation layer, a grid electrode field plate, a drain electrode field plate, aprotective layer, a grid electrode insertion layer, a p-type GaN grid electrode, a grid electrode metal, a source electrode metal and a drain electrode metal from bottom to top, wherein the passivation layer located on the surface of the AlGaN barrier layer is in a strip shape arranged at intervals, the grid electrode field plate and the drain electrode field plate respectively cover part of thepassivation layer, and the surfaces of the grid electrode field plate and the drain electrode field plate and the space between the grid electrode field plate and the drain electrode field plate are covered with the protective layer. According to the invention, the electric field distribution is uniform, the voltage endurance capability of the device is enhanced, the stability of grid electrode turn-on voltage and grid electrode voltage of the device is effectively improved, and the electric leakage of the device under the action of large current is effectively reduced. The preparation methodis completely compatible with a traditional process, and the preparation difficulty is low.

Owner:CHANGSHU INSTITUTE OF TECHNOLOGY

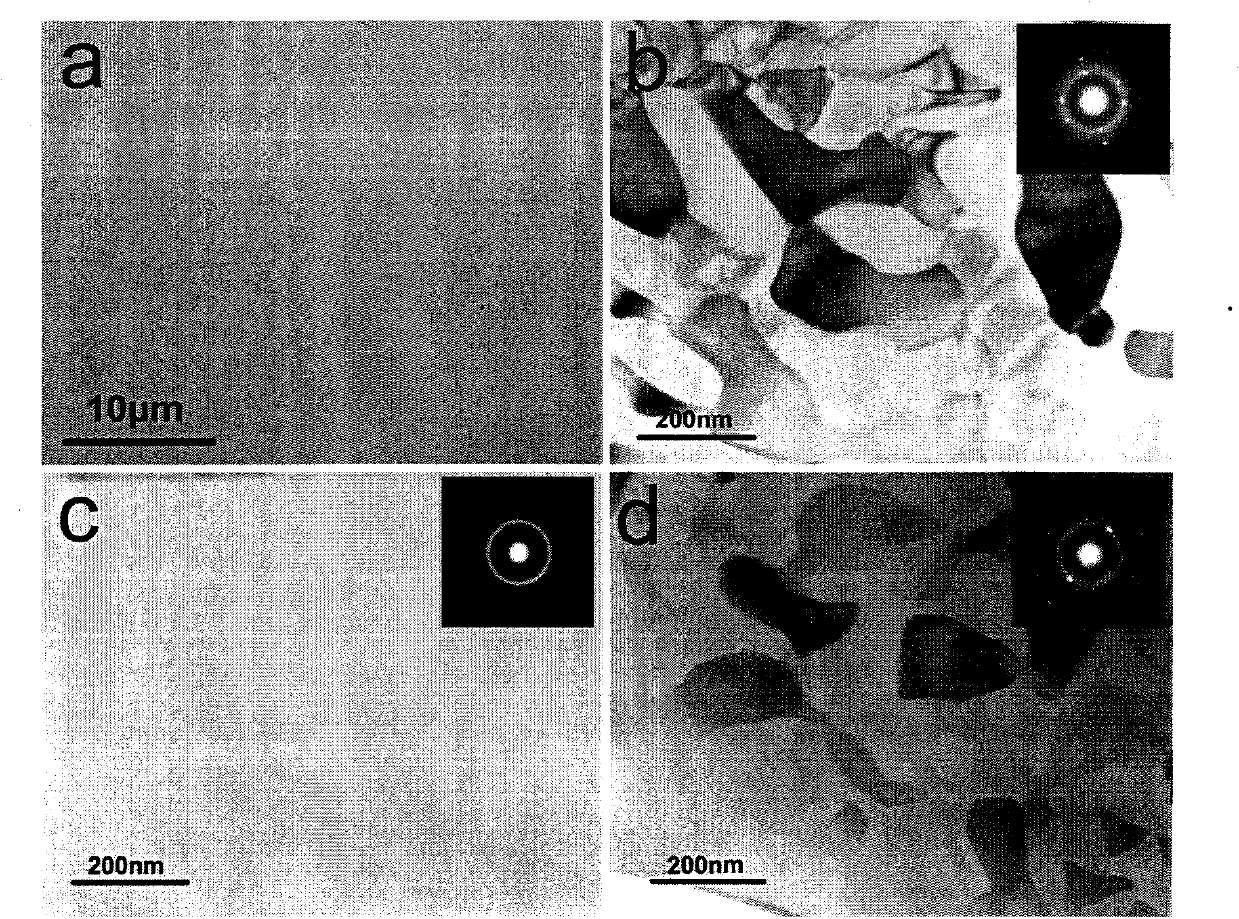

Method for passivating amorphous silicon and polycrystalline silicon film interfaces and manufacturing single junction polycrystalline silicon amorphous silicon (SPA) structure heterojunction with intrinsic thin-layer (HIT) cell

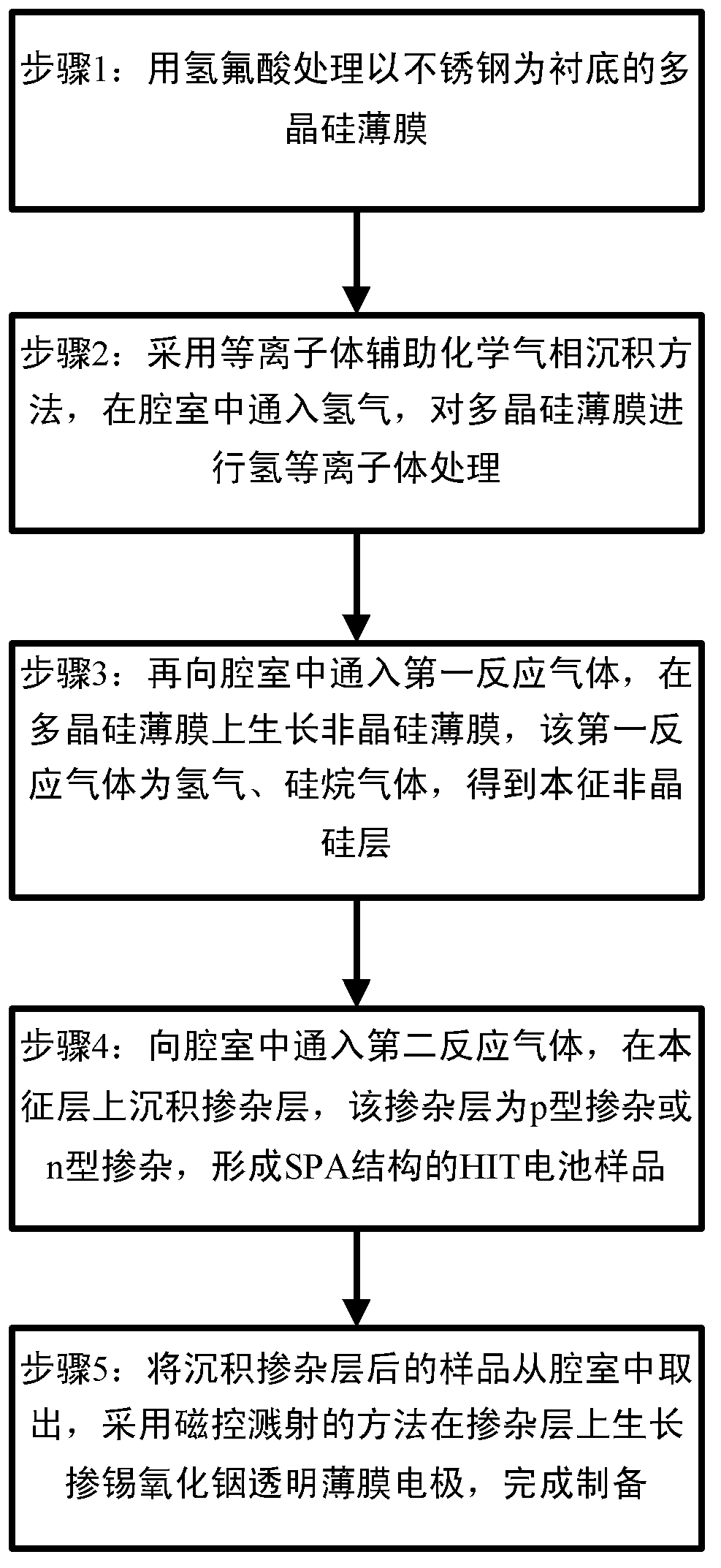

InactiveCN103258919AReduce interface state densityImprove conversion efficiencyFinal product manufactureSemiconductor devicesHeterojunctionGas phase

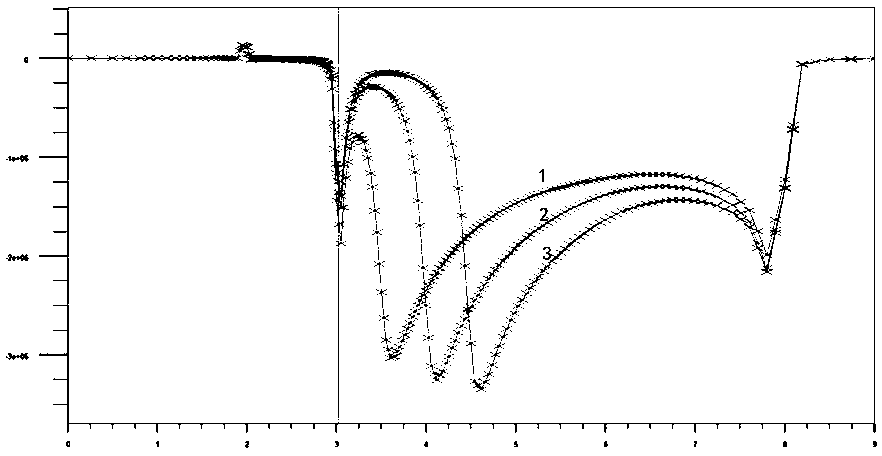

The invention discloses a method for passivating amorphous silicon and polycrystalline silicon film interfaces of a solar cell and a method for manufacturing an n-type polycrystalline silicon film single junction polycrystalline silicon amorphous silicon (SPA) structure heterojunction with intrinsic thin-layer (HIT) cell through the method. The method for passivating the amorphous silicon and polycrystalline silicon film interfaces of the solar cell comprises the steps of strengthening chemical vapor depositions through plasma, and carrying out passivation processing on the amorphous silicon and polycrystalline silicon film interfaces of the solar cell under the condition that ammonia is led into a cavity. A surface state of a polycrystalline silicon film can be reduced through hydrogen plasma interface processing. Therefore, interface states of amorphous silicon and polycrystalline silicon films of the SPA structure HIT cell are reduced, synthesis of photon-generated carriers generated under illumination at the positions of the interfaces is reduced, collection of the photo-generated carriers is increased, and conversion efficiency of the cell is improved.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Manufacturing method for thin film crystal silicon perovskite heterojunction solar cell

InactiveCN105428535AHighlight substantive featuresImprove efficiencyFinal product manufactureSolid-state devicesHeterojunctionLight energy

The invention relates to semiconductor devices specially suitable for converting light energy into electric energy, in particular to a manufacturing method for a thin film crystal silicon perovskite heterojunction solar cell which has an electron hole recombination inhibition structure layer and adopts a high-temperature-resistant and non-transparent conductive substrate. The method comprises the steps of: preparing a P-type crystal silicon thin film layer on the high-temperature-resistant and non-transparent conductive substrate; preparing the electron hole recombination inhibition structure layer on the P-type crystal silicon thin film layer; spin-coating the electron hole recombination inhibition structure layer with a perovskite light absorption layer; making an electron transmission layer composed of dense titanium dioxide on the perovskite light absorption layer; and preparing a top electrode on the electron transmission layer composed of dense titanium dioxide. According to the method, the defects of current leakage, internal short circuit and limitation of a glass substrate to a high-temperature link of a subsequent preparation process possibly existent in a thin film crystal silicon perovskite heterojunction solar cell in the prior art are overcome.

Owner:HEBEI UNIV OF TECH

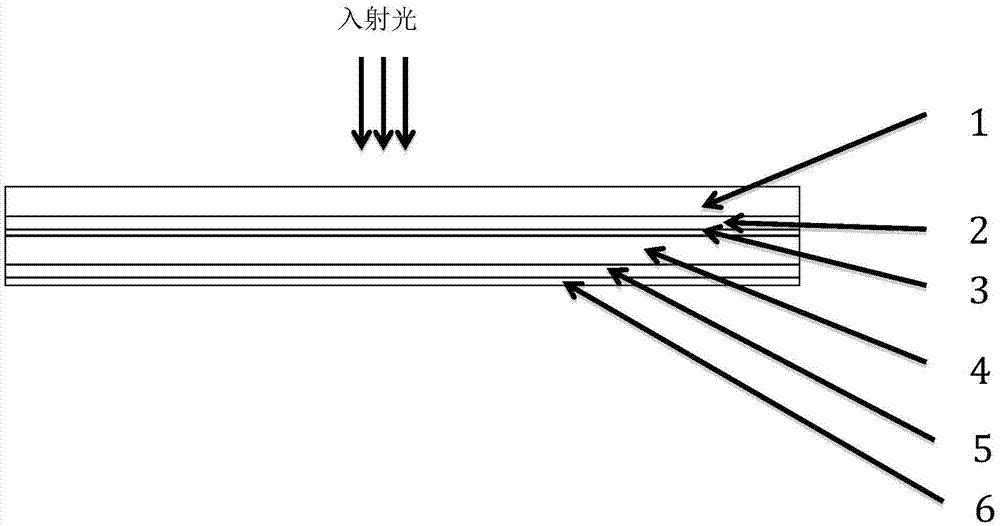

InGaAs low table face linear array or face array infrared detector chip

ActiveCN101170144AEffective protectionReduce surface stateSemiconductor devicesQuantum efficiencyOhmic contact

The invention discloses an InGaAs low mesa line series or area array infrared detector chip, which includes a line series or area array p-InP micro-mesa formed by etching on p-InP / InGaAs / n-InP epitaxial wafer. The p-InP micro-mesa is provided with an Au / Zn / Pt / Au / P electrode area in ohmic contact. A public N electrode area is etched to the n-InP layer on the side of the line series or area array micro-mesa and is positioned on the n-InP layer. Except for the P and N electrode areas, the whole epitaxial wafer and the lateral sides are covered by a silicon nitride passivation layer. The P electrode area is provided with an electrode interconnection area with a reading circuit. The electrode interconnection area covers a part of the micro-mesa and extends from the micro-mesa to a plane. The invention has the advantages of mesa decrease by retained InGaAs layer and effective protection on the InGaAs layer lateral sides. The silicon nitride passivation layer has effective function of reflection resistance and InP and InGaAs layer surface state reduction and can increase the detector quantum efficiency and decrease dark current. The P electrode adopts AuZnPtAu, forms good ohmic contact with p-InP and P can effectively prevent Zn from out diffusion and improve the device reliability.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

Thin film crystalline silicon perovskite heterojunction solar cell and preparation method thereof

ActiveCN105449103AHighlight substantive featuresImprove efficiencyFinal product manufactureSolid-state devicesElectronic transmissionHeterojunction

The invention provides a thin film crystalline silicon perovskite heterojunction solar cell and a preparation method thereof, relates to a semiconductor device for converting optical energy to electric energy, and particularly provides a thin film crystalline silicon perovskite heterojunction solar cell having an electronic cavity composite suppression structure layer. The solar cell includes a transparent conductive substrate, a P-type thin film crystalline silicon layer, an electronic cavity composite suppression structure layer, a perovskite light absorption layer, an electronic transmission layer formed by compact titanium dioxide, and a back electrode. The perovskite light absorption layer and the P-type thin film crystalline silicon layer have matched energy levels, and the electronic cavity composite suppression structure layer formed by SiO2 is added between the P-type thin film crystalline silicon layer and the perovskite light absorption layer. The solar cell provided overcomes the defects of current leakage and internal short circuit of a thin film crystalline silicon perovskite heterojunction solar cell in the prior art.

Owner:HEBEI UNIV OF TECH

Production method of low-noise germanium-silicon heterojunction bipolar transistor

ActiveCN102412149AReduce defect density and surface statesImprove noise characteristicsSemiconductor/solid-state device manufacturingRe crystallizationPolycrystalline silicon

The invention discloses a production method of a low-noise germanium-silicon heterojunction bipolar transistor, comprising the following steps of: step 1, applying a polysilicon layer for an emitting electrode of the germanium-silicon heterojunction bipolar transistor, doping the emitting electrode, then, executing quick thermal annealing, and diffusing and redistributing the impurities; step 2, executing pre-amorphization ion implantation with medium and high dosage of large atom impurities on the polysilicon emitting electrode, annealing quickly, realizing re-crystallization of the amorphous emitting electrode, and generating a single crystal layer, thereby forming an emitting area / base area junction by the monocrystal silicon / monocrystal germanium and silicon; step 3, executing quick thermal annealing after the process of pre-amorphization ion implantation, and crystallizing the amorphous emitting electrode. With the method provided by the invention, the noise caused by a polysilicon emitting electrode is reduced, and noise characteristics of devices are improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Nitride semiconductor device

ActiveUS7304330B2Suppressed ionizationImprove leakage currentTransistorSemiconductor/solid-state device manufacturingIndiumNitrogen

Owner:NEW JAPAN RADIO CORP

Surface passivation structure for III-V group nitride device and device thereof

ActiveCN112420813AReduce surface stateReduce the introductionSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringNitride

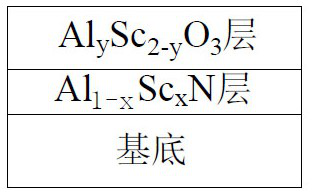

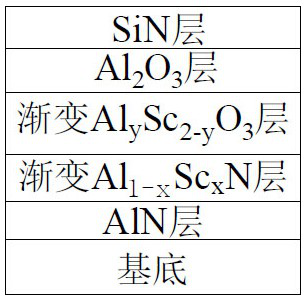

The invention discloses a surface passivation structure for a III-V group nitride device and a device thereof. The surface passivation structure comprises an Al1-xScxN layer and an AlySc2-yO3 layer, the Al1-xScxN layer and the AlySc2-yO3 layer are located on a III-V nitride substrate, the Al1-xScxN layer and the AlySc2-yO3 layer are sequentially stacked from bottom to top, the thickness of the Al1-xScxN layer is 0.5-10 nm, x is larger than 0 and equal to or smaller than 1, the thickness of the AlySc2-yO3 layer is 1-20nm, y is more than or equal to 0 and less than 2, and the thickness of the Al1-xScxN layer is less than or equal to the thickness of the AlySc2-yO3 layer. Generation of an interface state can be further reduced, the risk of current collapse of the device is reduced, and the reliability of the device is improved.

Owner:XIAMEN SANAN INTEGRATED CIRCUIT

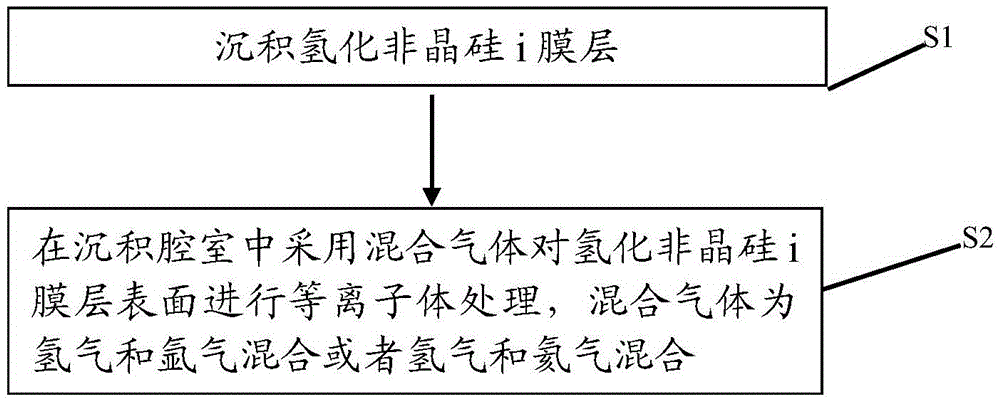

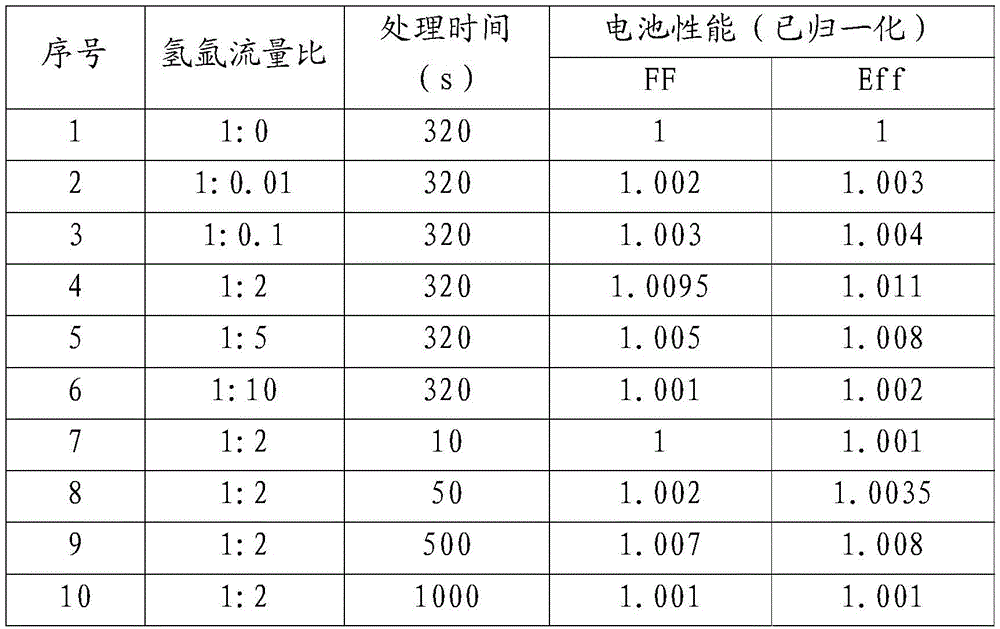

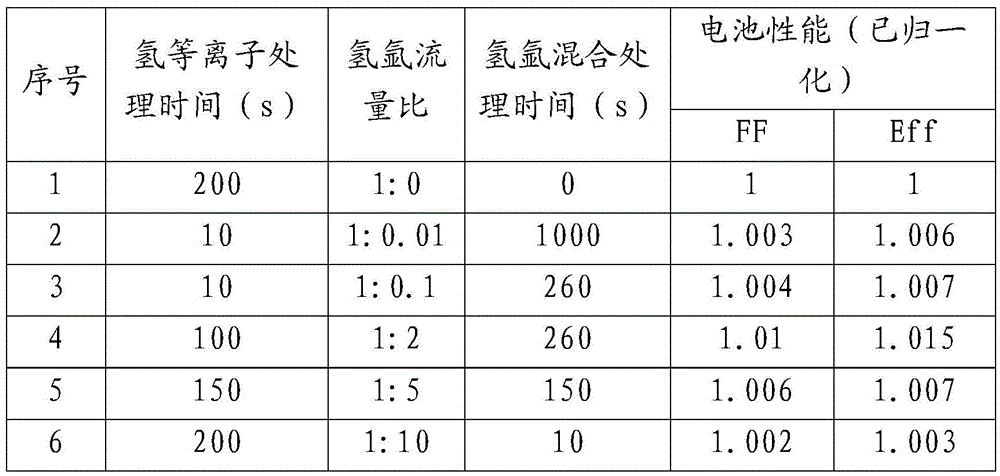

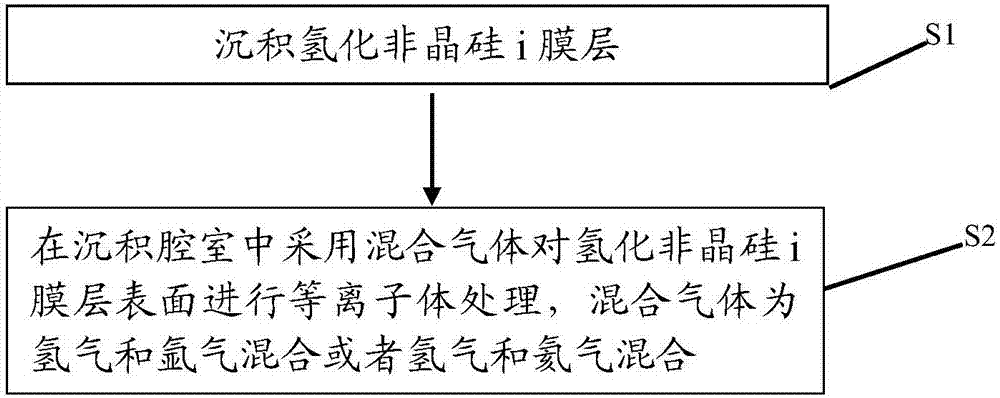

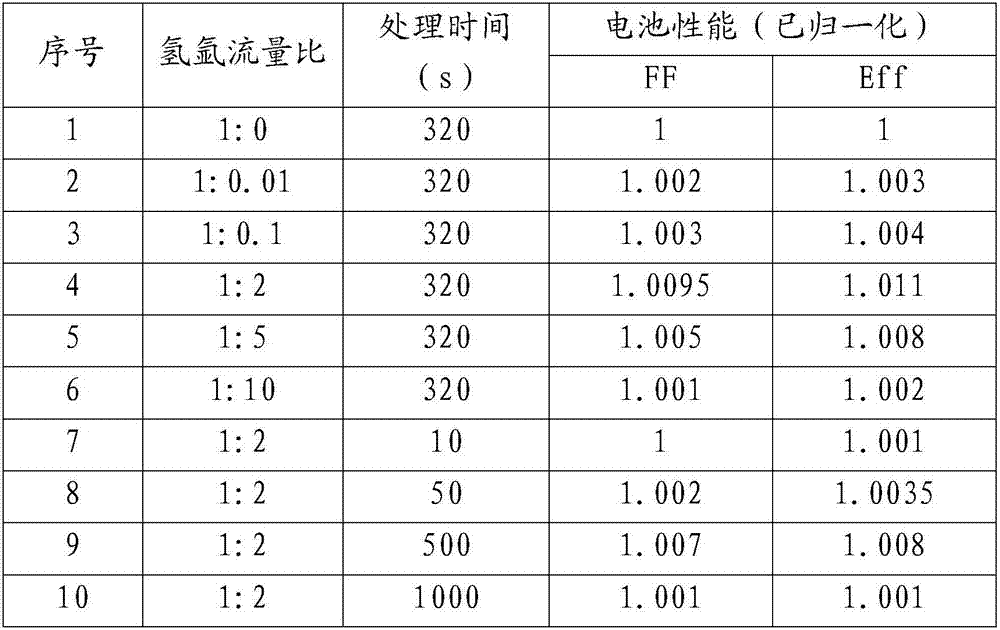

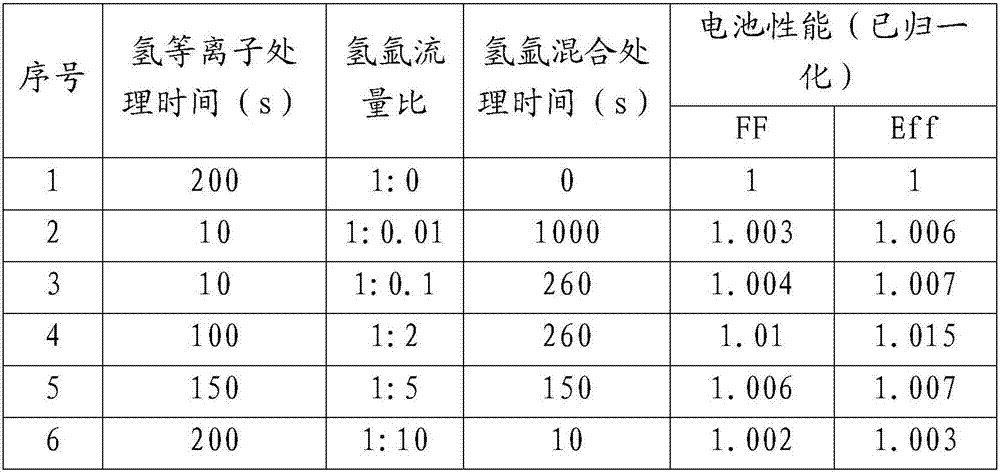

Solar cell and surface treatment method of hydrogenated amorphous silicon i film layer thereof

ActiveCN105489668AImprove performanceEasy to cleanFinal product manufacturePhotovoltaic energy generationHydrogenSolar cell

The invention discloses a silicon heterojunction solar cell and a surface treatment method of a hydrogenated amorphous silicon i film layer thereof. Plasma treatment is carried out on the surface of the hydrogenated amorphous silicon i film layer by adopting a gas mixture of hydrogen and argon or hydrogen and helium, the hydrogenated amorphous silicon i film layer can be preferably cleaned in a physical manner through argon or helium plasmas, and the increase of the amount of the helium plasmas is further promoted, so that the passivating and cleaning effects for the surface of the hydrogenated amorphous silicon i film layer are strengthened; and moreover, slight damage to the surface of the hydrogenated amorphous silicon i film layer can be generated in the physical bombarding process of the argon or helium plasmas, and the hydrogen plasmas can play a passivating role on the surface of the hydrogenated amorphous silicon i film layer and can also repair the slight damage. Through the synergistic effect of the gas mixture of hydrogen and argon or hydrogen and helium, better passivating and cleaning effects can be achieved for the surface of the hydrogenated amorphous silicon i film layer, so that the battery performance is promoted.

Owner:ENN SOLAR ENERGY

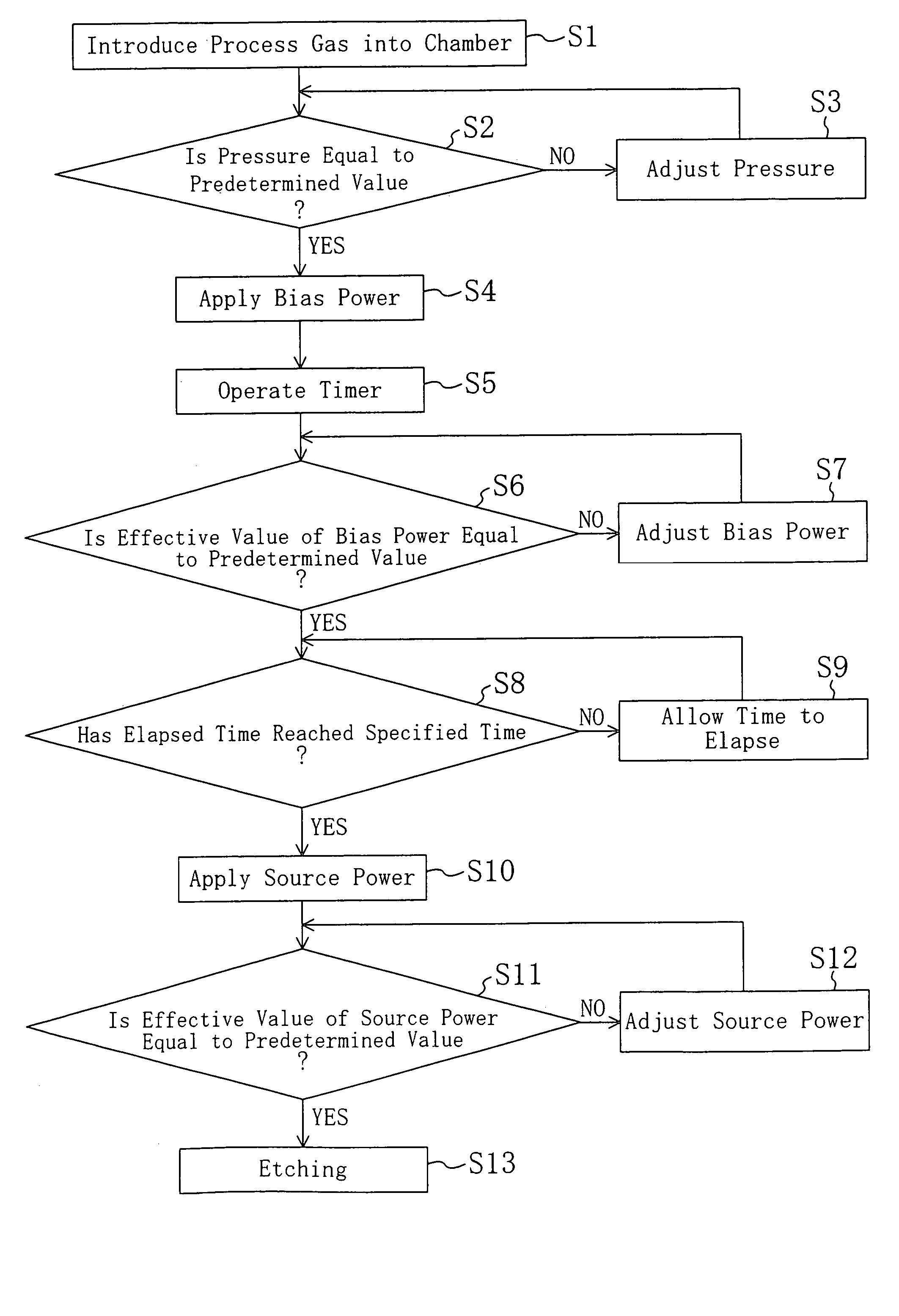

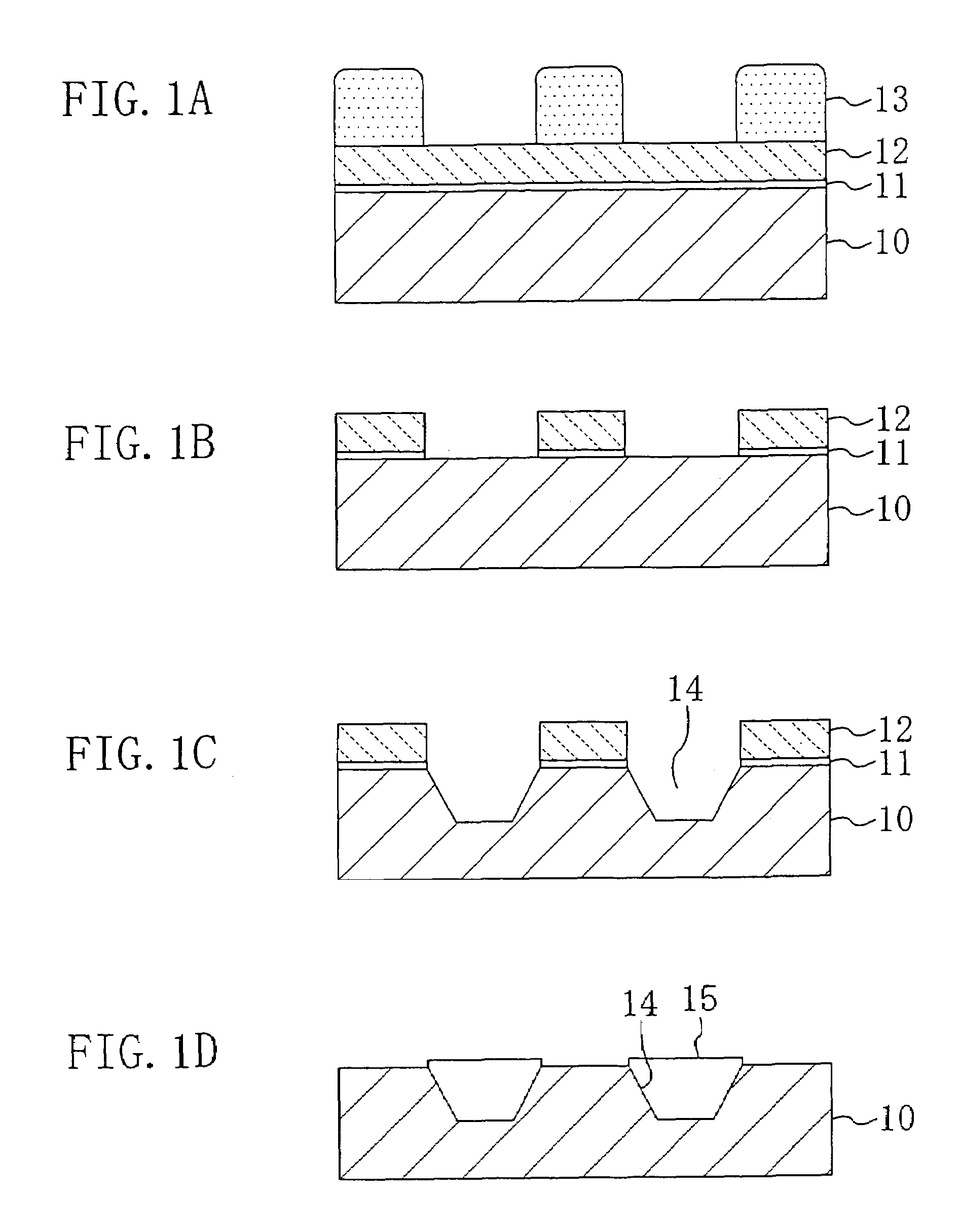

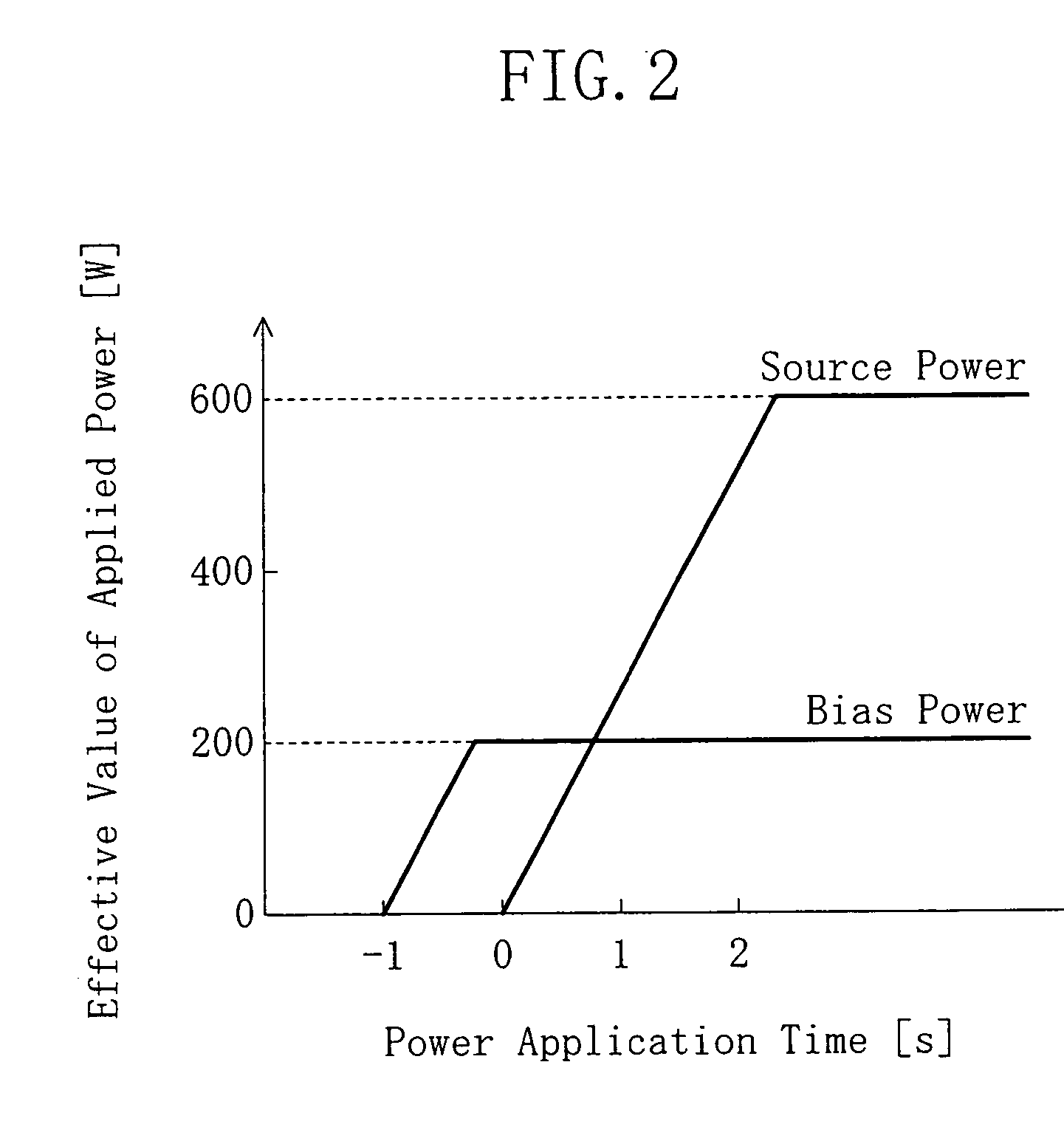

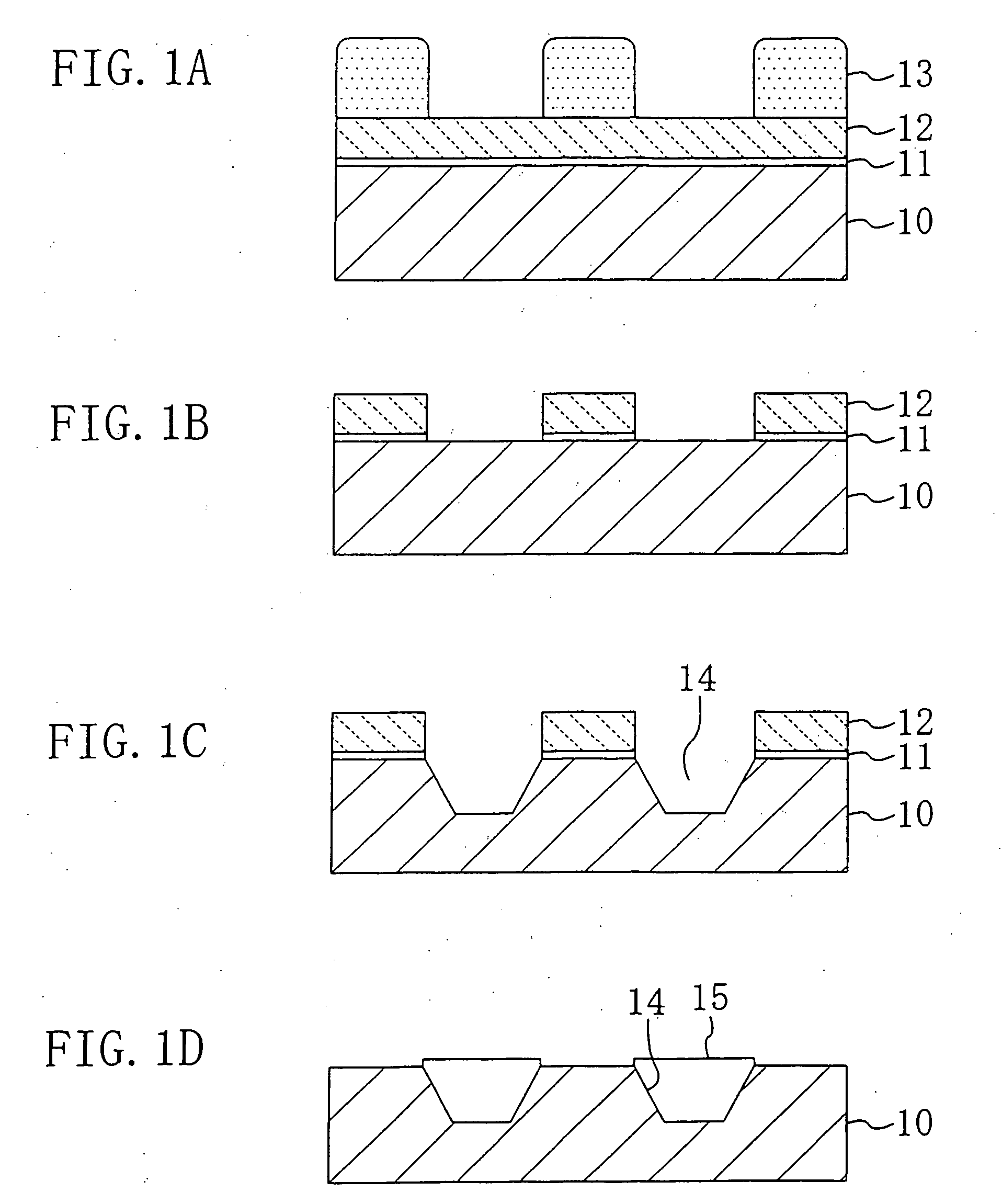

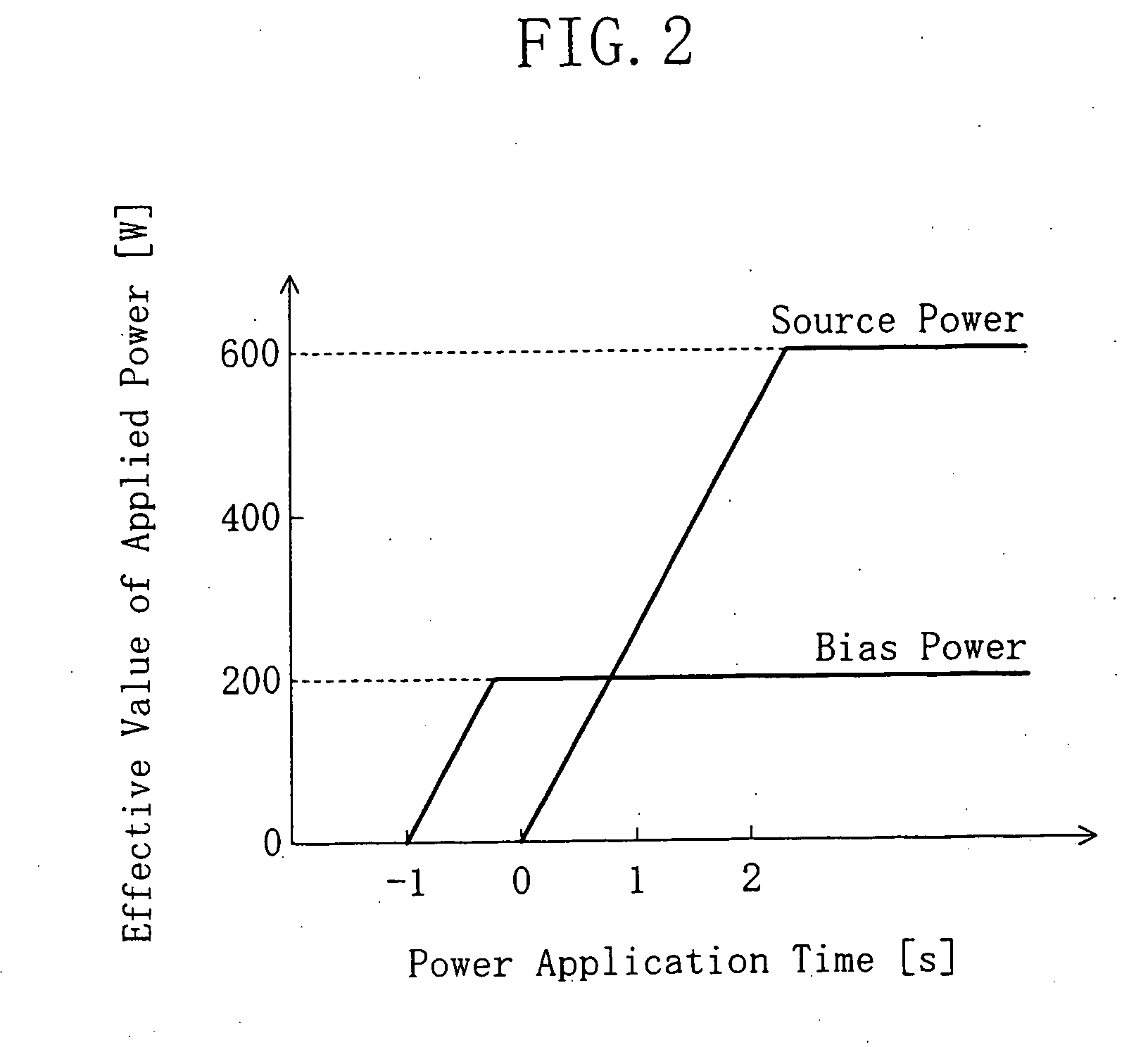

Dry etching method, fabrication method for semiconductor device, and dry etching apparatus

InactiveUS7148151B2Avoid feature degradationReduce surface stateElectric discharge tubesDecorative surface effectsEngineeringSilicon

When etching is performed with respect to a silicon-containing material by using a dry etching apparatus having a dual power source, the application of bias power is initiated before oxidization proceeds at a surface of the silicon-containing material. Specifically, the application of the bias power is initiated before the application of source power is initiated. Alternatively, the source power and the bias power are applied such that the effective value of the source power reaches a second predetermined value after the effective value of the bias power reaches a first predetermined value.

Owner:TAIWAN SEMICON MFG CO LTD

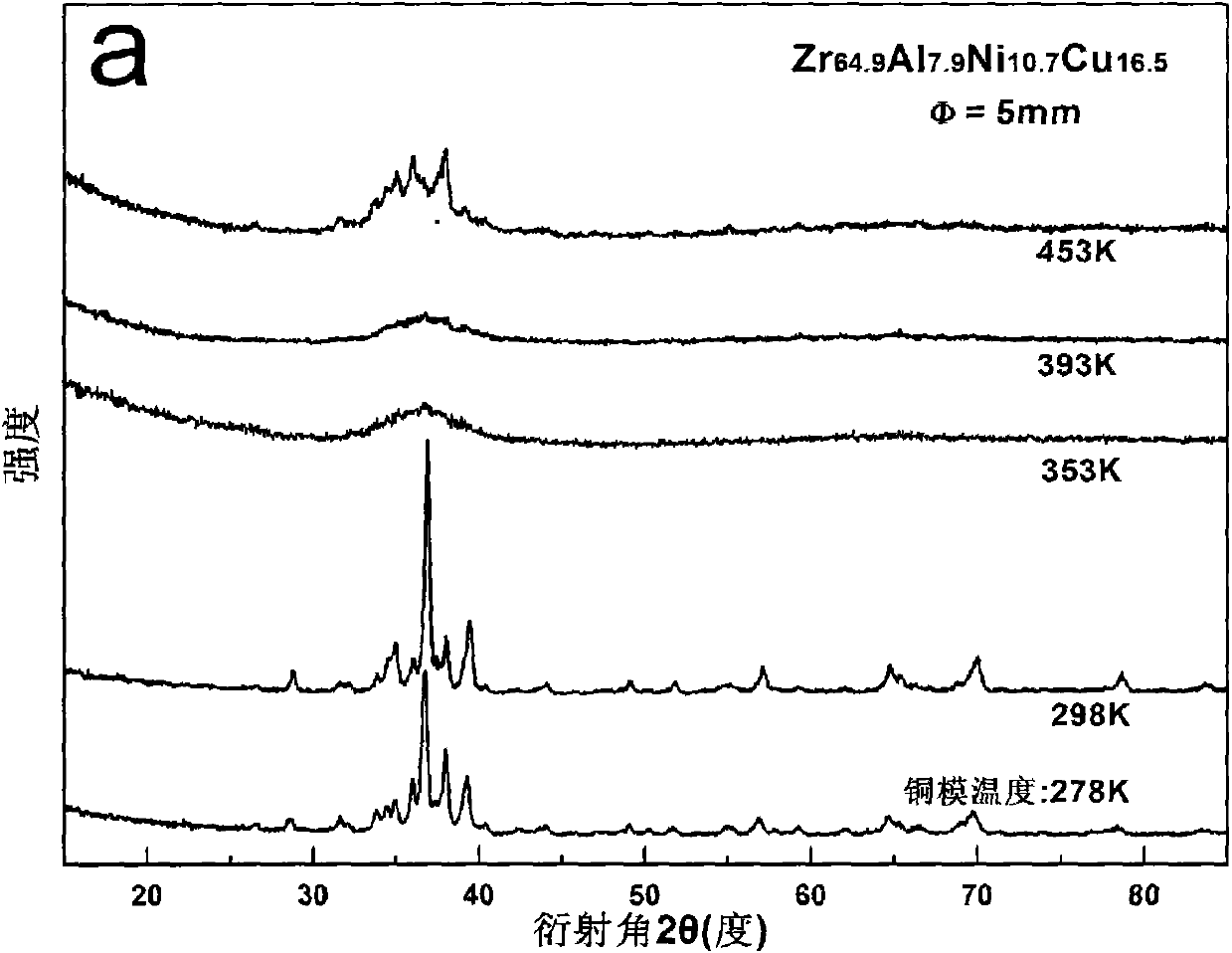

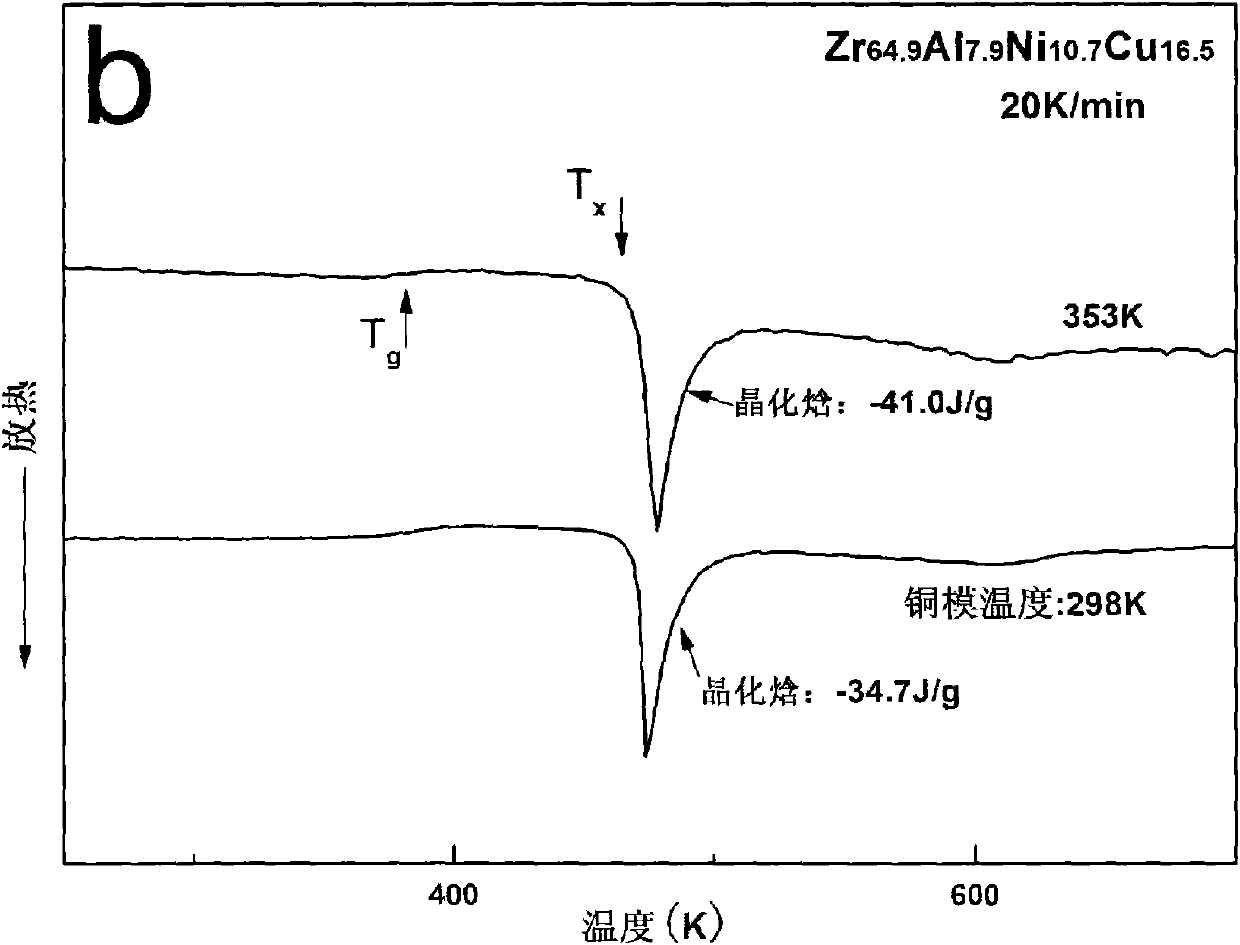

Method for improving forming ability and strength of amorphous alloy by controlling solidifying condition

The invention relates to a preparation technology of block amorphous alloy, in particular to a method for improving the forming ability and strength of amorphous alloy by controlling solidifying condition. The method has low process cost, is simple and easy, can obviously strengthen the forming ability of block amorphous alloy and improve the material strength and is suitable for a majority of amorphous systems. The casting is carried out when the preheating temperature of a die reaches 353-393K by adjusting the preheating temperature of the die through adopting a copper die casting method and the amorphous forming ability can be improved so that the amorphous alloy in a larger size can be obtained; meanwhile, the strength of an amorphous alloy material is improved by 4-18 percent. The invention develops a novel method for improving the forming ability of the block amorphous alloy, confirms a novel process parameter for producing the block amorphous alloy in larger size and improving the strength and broadens the application field of the block amorphous alloy.

Owner:辽宁金研液态金属科技有限公司 +1

Solar cell and hydrogenated amorphous silicon i membrane surface processing method thereof

ActiveCN107425087AImprove performanceEasy to cleanFinal product manufacturePhotovoltaic energy generationHydrogenPhysical chemistry

Owner:ENN SOLAR ENERGY

Nitride semiconductor device and production process thereof

ActiveUS20050116248A1Suppressed ionizationImprove leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesIndiumNitrogen

A nitride semiconductor device, which includes a III-V Group nitride semiconductor layer being composed of a III Group element consisting of at least one of a group containing of gallium, aluminum, boron and indium and V Group element consisting of at least nitrogen among a group consisting of nitrogen, phosphorus and arsenic, including a first nitride semiconductor layer including the III-V Group nitride semiconductor layer being deposited on a substrate, a second nitride semiconductor layer including the III-V Group nitride semiconductor layer being deposited on the first nitride semiconductor and not containing aluminum and a control electrode making Schottky contact with the second nitride semiconductor layer wherein the second nitride semiconductor layer includes a film whose film forming temperature is lower than the first nitride semiconductor layer.

Owner:NEW JAPAN RADIO CORP

Dry etching method, fabrication method for semiconductor device, and dry etching apparatus

InactiveUS20060258117A1Avoid feature degradationReduce surface stateElectric discharge tubesDecorative surface effectsSiliconDry etching

When etching is performed with respect to a silicon-containing material by using a dry etching apparatus having a dual power source, the application of bias power is initiated before oxidization proceeds at a surface of the silicon-containing material. Specifically, the application of the bias power is initiated before the application of source power is initiated. Alternatively, the source power and the bias power are applied such that the effective value of the source power reaches a second predetermined value after the effective value of the bias power reaches a first predetermined value.

Owner:TAIWAN SEMICON MFG CO LTD