Semiconductor structure and forming method thereof

A semiconductor and integrated circuit technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc. Links etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

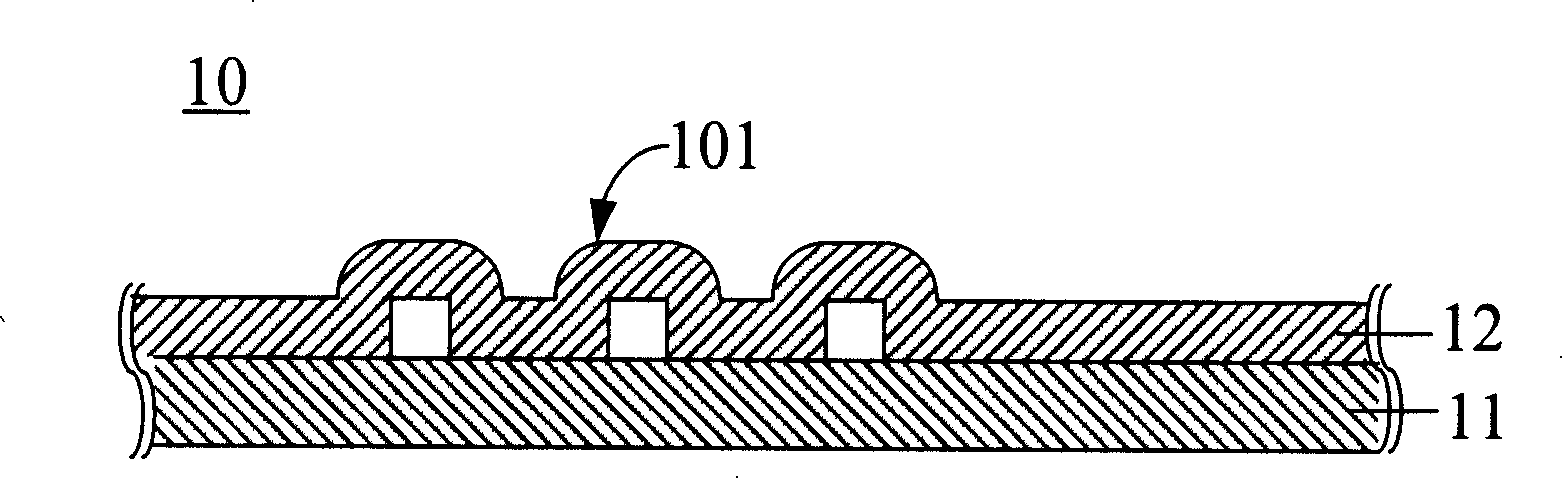

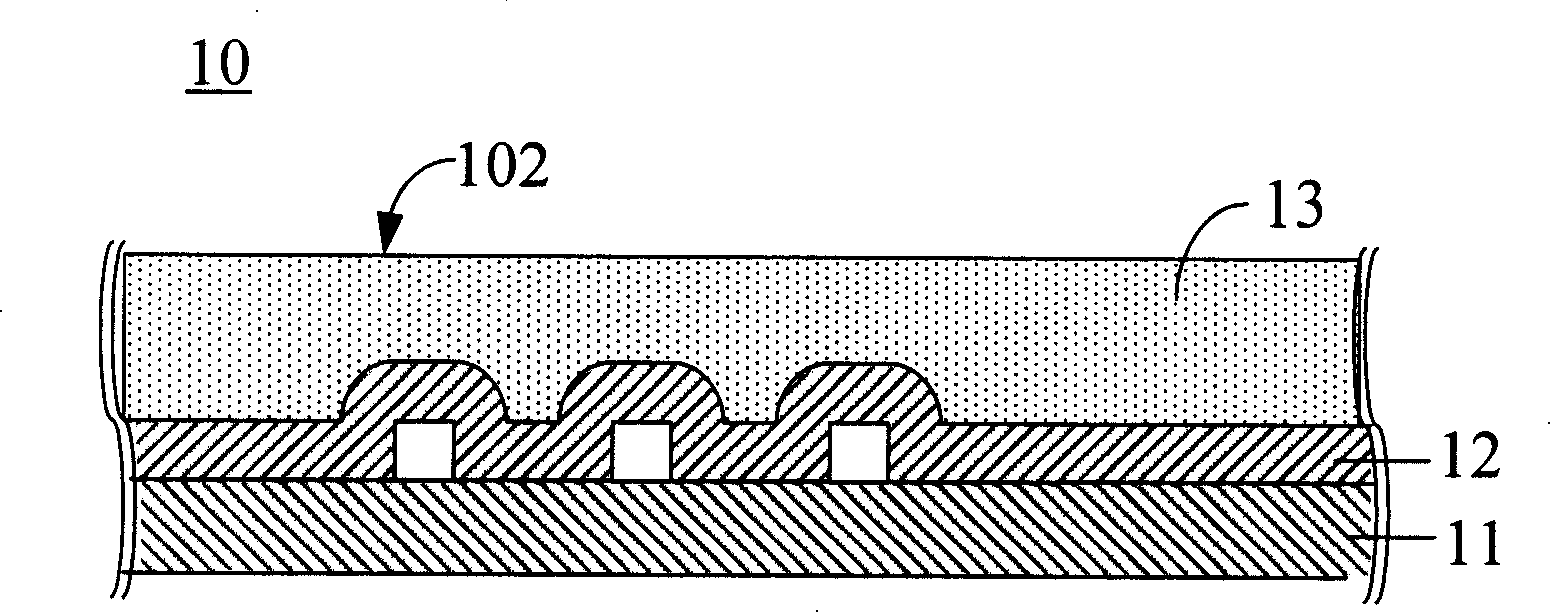

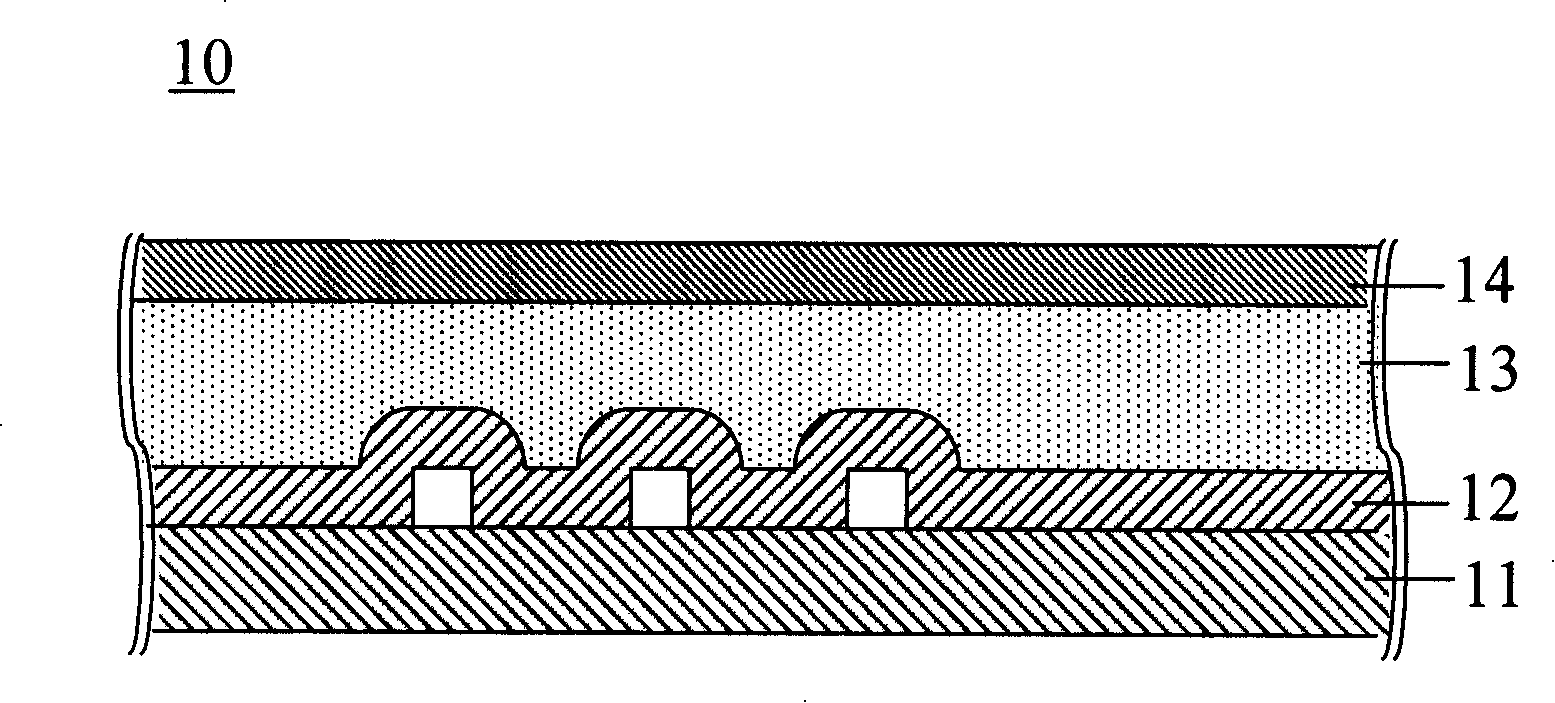

[0012] Figure 1(a) to Figure 1(d) A preferred embodiment of the present invention is shown to present a manufacturing process of a semiconductor structure 10 having a conductive structure.

[0013] As shown in Figure 1(a), the semiconductor structure 10 includes a base material 11 and a passivation layer 12 arranged above the base material 11. Because there is an integrated circuit layout on the base material 11, the passivation layer 12 The surface is not flat; as shown in the figure, the passivation layer 12 has an uneven first upper surface 101 . If a conductive underlying metal is directly formed on the first upper surface 101 , the underlying metal may form breakpoints at the turning points of the first upper surface 101 , resulting in uneven impedance and poor conductivity. Since the substrate 11 with the integrated circuit layout is manufactured, the passivation layer 12 has also been formed together, and the passivation layer 12 is widely and isotropically formed on t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com