Phase selection programmable frequency divider

A phase selection and frequency divider technology, applied in the field of frequency synthesizers, can solve the problems of limited frequency accuracy, logic errors, glitches, etc., to improve the overall phase noise, reduce in-band phase noise, and reduce the probability of errors.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

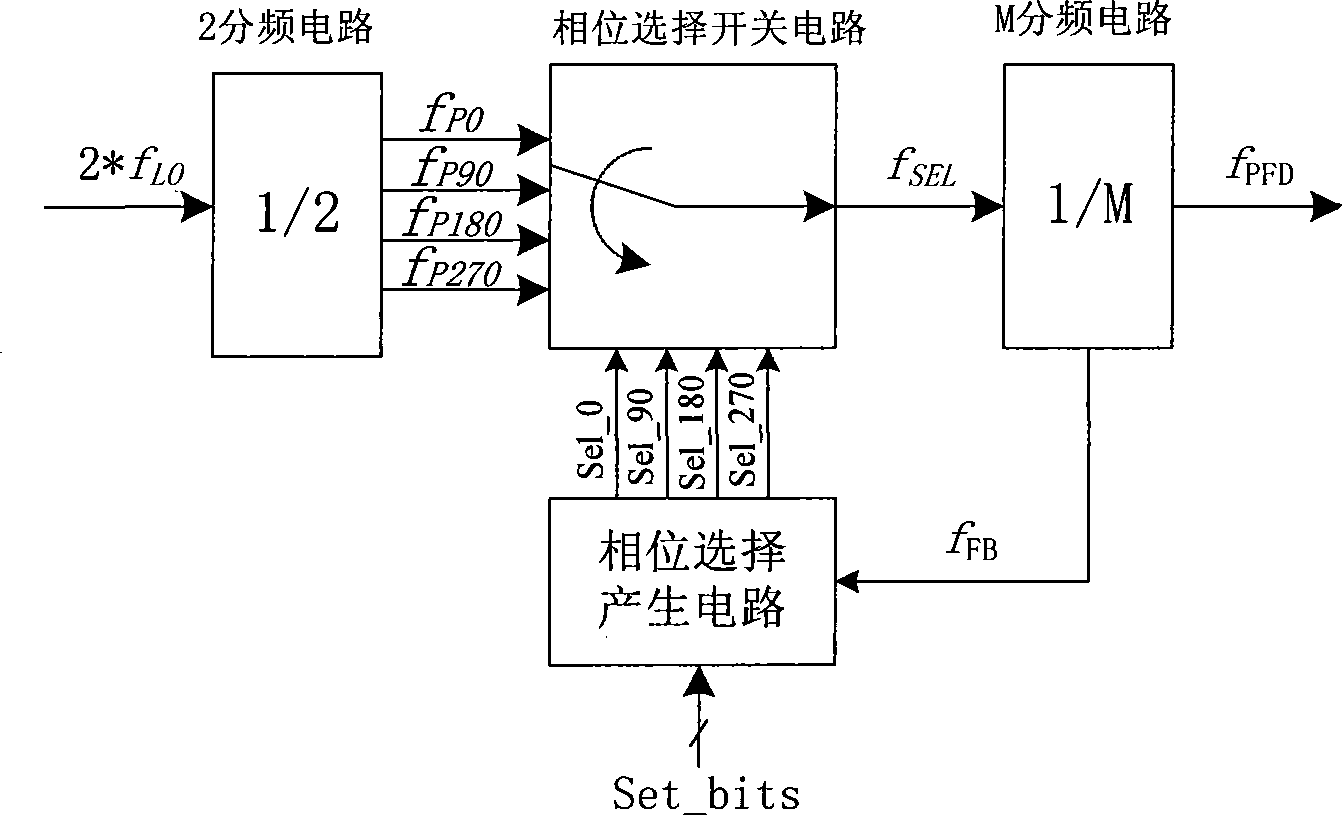

[0015] In one embodiment, such as figure 1 As shown, the phase selection programmable frequency divider of the present invention includes a 2 frequency division circuit, a phase selection switch circuit, a phase selection generation circuit and an M frequency division circuit.

[0016] The 2 frequency division circuit is a 2 frequency division circuit with orthogonal output characteristics. In the present invention, the frequency of the input signal of the 2 frequency division circuit is 2 times the actual operating frequency of the system, i.e. 2*f L0 , its output signal is four signals f with a phase difference of 90 degrees P0 , f P90 , f P180 and f P270 , those skilled in the art should know that the frequencies of these four output signals are the same as the actual working frequency of the system.

[0017] The phase selection switch circuit is used to select and output one of the four signals with a phase difference of 90 degrees under the control of the switching co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More