System and method for validating and testing on-chip system

A system-on-chip and test interface technology, which is applied in the computer field, can solve problems such as slow speed, and achieve the effect of reducing the delay of pins, improving the speed of verification, and increasing the speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

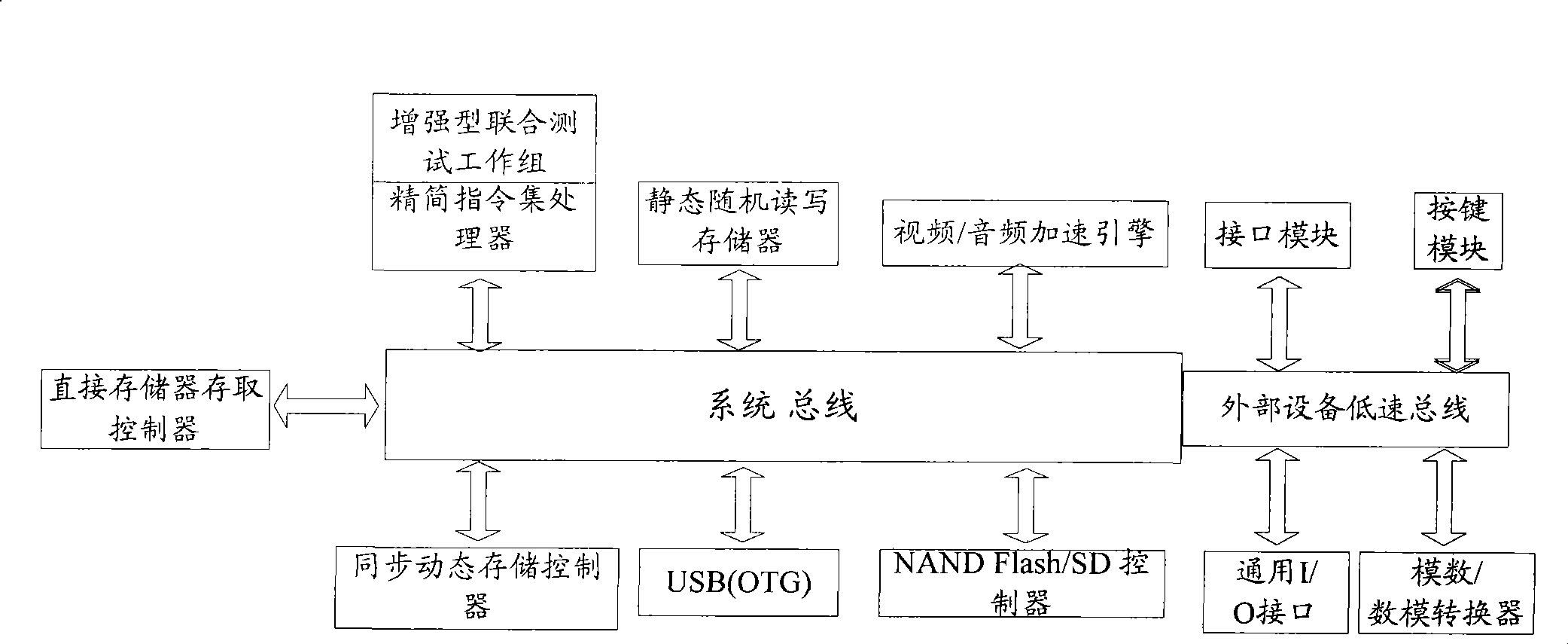

[0077] Implementation 1: The verification stimulus device only includes the RISP bus control unit, so that the system-on-chip needs to be verified only through the test interface circuit, the data connected between the test interface circuit and the RISC bus control unit, and the control line interface is The first interface, the specific process is as follows, see Image 6 :

[0078] Step 601: Determine that the operating mode of the SoC emulation device is the first operating mode, and at this time, the test interface circuit controls the system bus mode.

[0079] By injecting the clock signal, the reset signal and the timing of the mode signal, the system-on-chip emulation device runs in the first working mode.

[0080]Step 602: The reduced instruction set processor bus control unit sends verification programs to the test interface circuit through the first interface. These verification programs include parsing the assembly-like instruction set to generate verification tim...

Embodiment 2

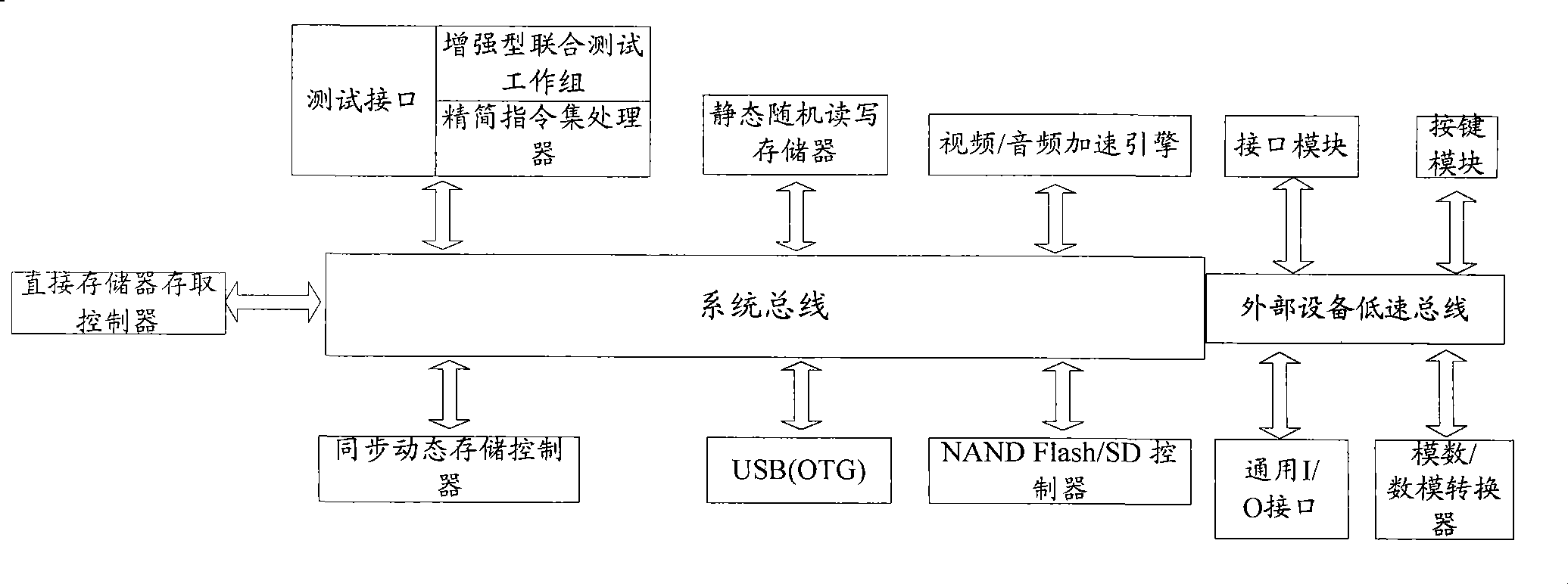

[0086] Embodiment 2: According to the architecture of the above system-on-chip verification, the verification stimulus device includes an RISP bus control unit and an enhanced joint test working group bus control unit. For data between the test interface circuit in the simulation device and the RISP bus control unit, the control line interface is the first interface, between the RISC processor in the simulation device and the enhanced joint test working group bus control unit The data of the control line interface is an enhanced joint test working group interface. The specific process of system-on-chip verification is as follows, see Figure 7 :

[0087] Step 701: Determine that the working mode of the SoC is the first working mode, and at this time, the test interface circuit controls the state of the system bus.

[0088] In the embodiment of the present invention, by controlling the pins of the SOC simulation device, that is, by injecting the clock signal, the timing sequen...

Embodiment 3

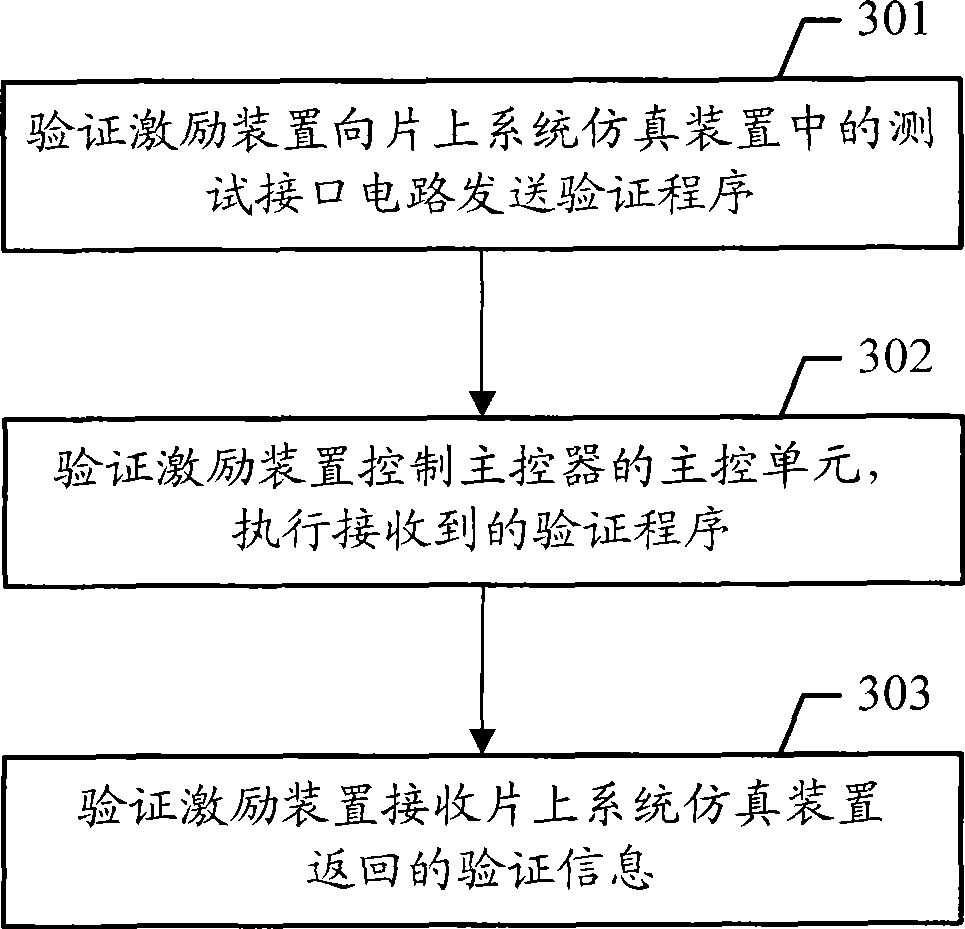

[0128] Implementation 3: The test stimulus device only includes the RISP bus control unit, so that the system-on-chip needs to be tested only through the test interface circuit, the data connected between the test interface circuit and the RISC bus control unit, and the control line interface is The first interface, the specific process is as follows, see Figure 11 :

[0129] Step 1101: Determine that the working mode of the system on chip is the first working mode, and at this time, the test interface circuit controls the system bus mode.

[0130] The system-on-chip runs in the first working mode by pouring in the timing of the clock signal, the reset signal and the mode signal.

[0131] Step 1102: The RISP bus control unit simulates the test timing signal according to the test vector generated in the verification process. Here, the verification process can be performed according to the verification method provided in the embodiment of the present invention, or according t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More