Resistance memory and method for fabricating integrated circuit with same

A resistive memory and integrated circuit technology, which is applied in the field of integrated circuits and their manufacturing, can solve the problems of complex manufacturing process, damage to the interface structure of the storage medium 170, influence on the performance of resistive memory, etc., and achieves simplified manufacturing process, flexible and controllable process method, The effect of good interface quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0045] This embodiment provides a method for manufacturing an integrated circuit including a resistive memory, including:

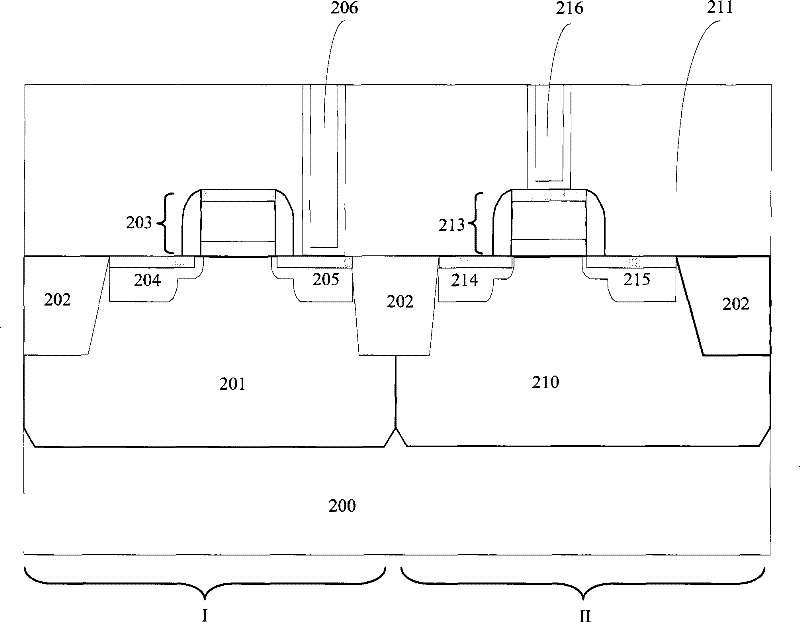

[0046] Provide a semiconductor substrate and an interlayer dielectric layer on the semiconductor substrate, the semiconductor substrate and the interlayer dielectric layer include a core device area and a peripheral circuit area;

[0047] A first interconnection structure is formed in the interlayer dielectric layer in the core device area, a second interconnection structure is formed in the interlayer dielectric layer in the peripheral circuit area, the first interconnection structure is used to electrically connect the semiconductor devices in the core device area, The second interconnection structure is used to electrically connect the semiconductor devices in the peripheral circuit area;

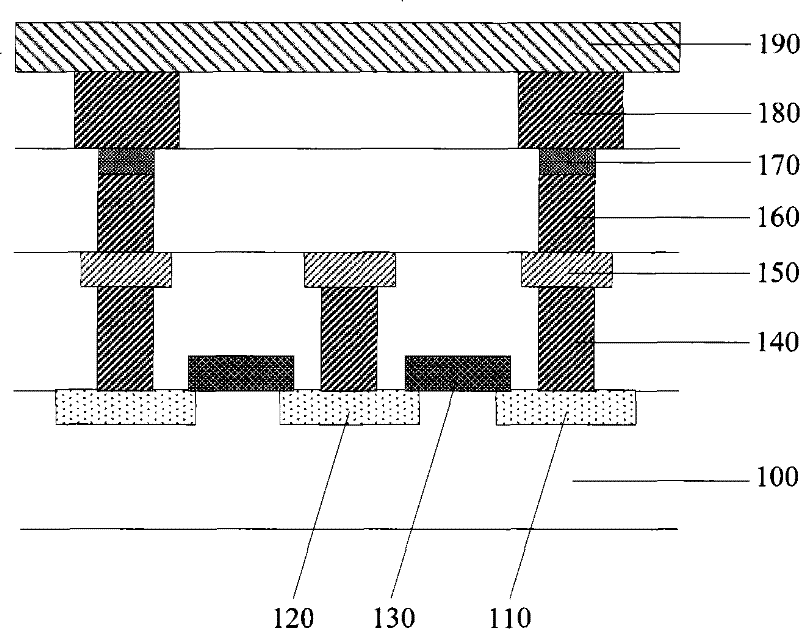

[0048] forming a first dielectric layer on the first interconnection structure, and forming a second dielectric layer on the second interconnection structure;

[0...

specific Embodiment approach

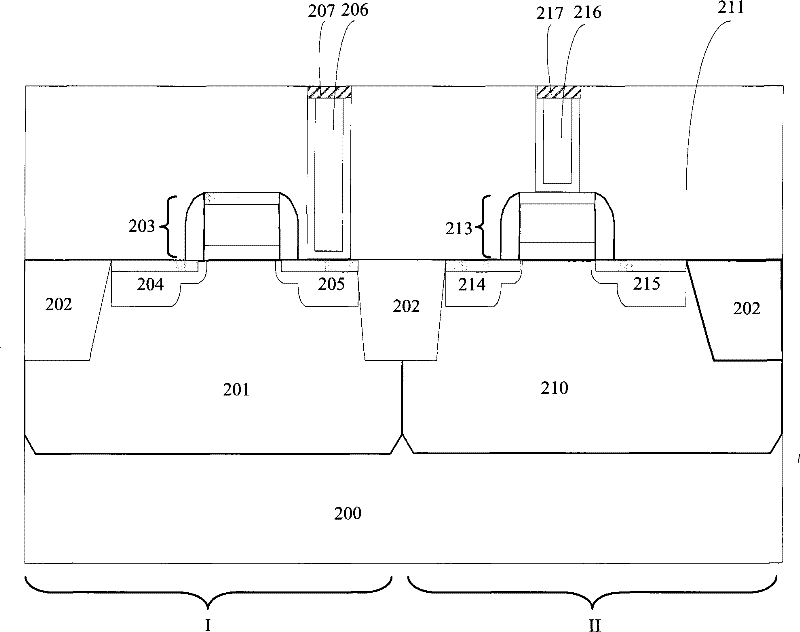

[0077] By adopting the first specific implementation manner, the subtle influence of the ashing process on the photoresist on the surface of the second interconnection structure is avoided, and a good surface of the second interconnection structure is maintained.

[0078] On the other hand, the first conductive layer and the second dielectric layer in the peripheral circuit area are removed to expose the second interconnection structure, and only the first conductive layer on the first dielectric layer is left in the core device area. The method can be: refer to the attached Figure 5 As shown, a mask layer 218 is formed on the first conductive layer 212. The mask layer 218 is, for example, a photoresist layer. Refer to the attached Figure 6 As shown, the photoresist layer 218 is exposed and developed, the photoresist layer in the peripheral circuit region II and the photoresist layer other than the position corresponding to the first interconnection structure 206 in the core...

Embodiment 2

[0090] This embodiment provides a resistance memory, refer to the attached Figure 10 As shown, it includes a first interconnection structure 206 as a lower electrode, a first dielectric layer 207 as a storage medium layer, and a first conductive layer 212 and a second conductive layer 209 as an upper electrode.

[0091] Wherein, the first interconnection structure 206 is metal copper or metal tungsten, and the attached Figure 10 The second interconnection structure 216 in the peripheral circuit area of the integrated circuit is formed at the same time, and the formation process is any prior art well known to those skilled in the art.

[0092] The first dielectric layer 207 may be formed by direct oxidation of the first interconnection structure 206, preferably a thermal oxidation process. Or the WO deposited directly on the first interconnection structure 206 by chemical vapor deposition or physical vapor deposition X ,TiO 2 , NiO, ZrO 2 , HfO 2 , CeO 2 , RuO X , Cu...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More