Method for manufacturing shallow junction complementary bipolar transistor

A technology of bipolar transistor and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of low withstand voltage of transistors, difficult to meet the high-precision and dynamic adjustment requirements of high-speed analog integrated circuits, and achieve the characteristics of The effect of increasing frequency, reducing leakage current, and increasing withstand voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The specific embodiments of the present invention are not limited to the following description. The present invention will now be further described with reference to the drawings.

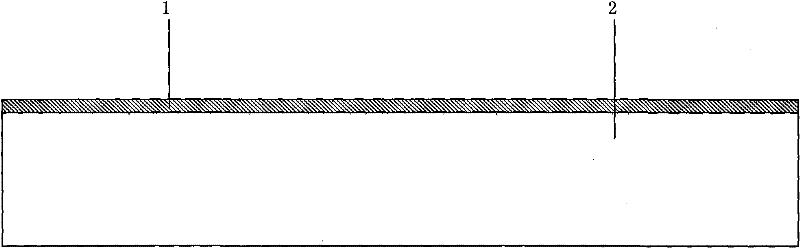

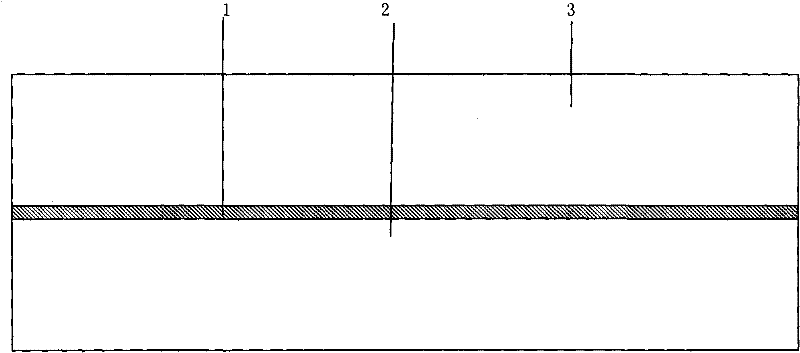

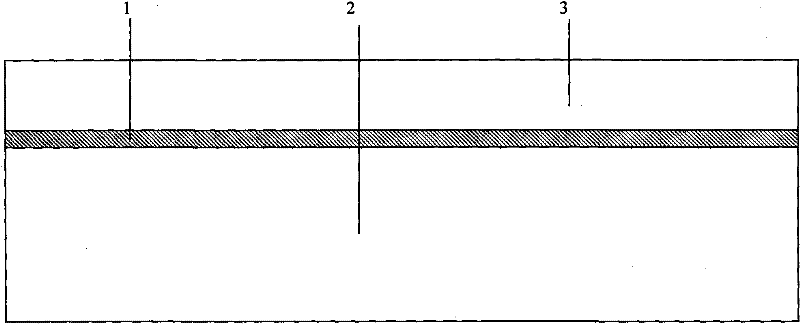

[0046] The method of the present invention first uses silicon / silicon bonding, CMP thinning and polishing technology to obtain the required SOI material sheet, and then forms the SOI material sheet by implanting a buried layer, decompressing ultra-thin epitaxy, deep trench etching, and polysilicon backfilling. The deep trench dielectric isolation plus shallow isolation wall technology, combined with the complementary bipolar process compatible with the vertical PNP of the shallow junction polysilicon emitter and the vertical NPN, is used to manufacture the shallow junction complementary bipolar transistor.

[0047] 1. The steps of forming SOI material sheet by silicon / silicon bonding, thinning and polishing method are:

[0048] 1# liquid (NH) for P-type silicon wafer 2 with crystal orientation an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More