Processing method of fuse wire on copper interconnection layer and semiconductor device thereof

A technology of copper interconnection and manufacturing method, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of increasing the relative dielectric constant of IMD, complicated operation process, and increased power consumption. Achieve the effects of optimizing electrical performance and operating speed, simplifying process production, and improving parameter matching

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

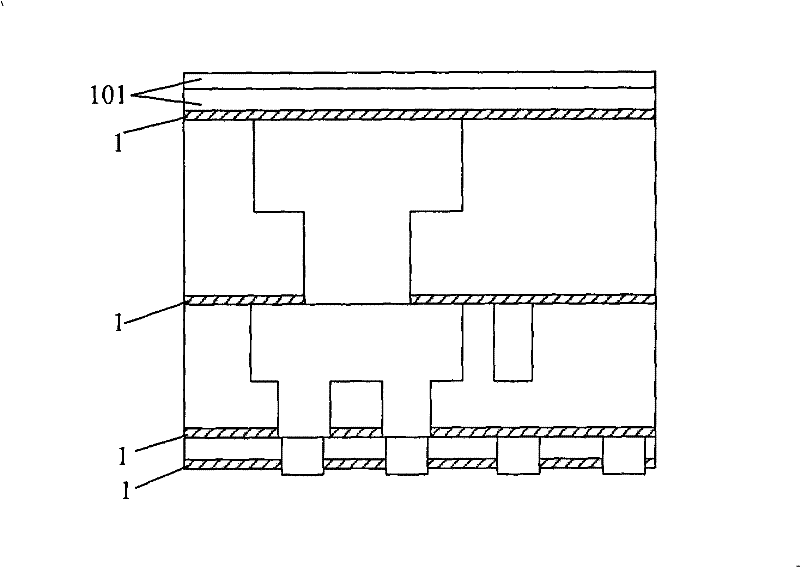

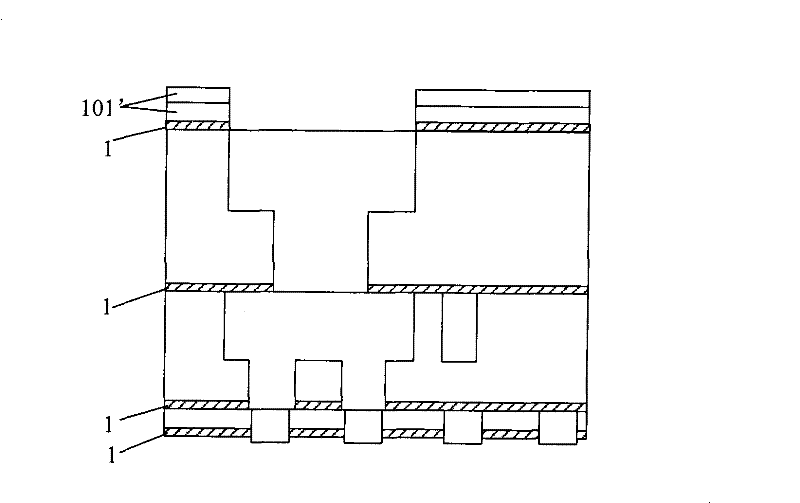

[0058] In order to make the object, technical solution, and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

[0059] The present invention has been described in detail using schematic diagrams. When describing the embodiments of the present invention in detail, for the convenience of explanation, the schematic diagram showing the structure will not be partially enlarged according to the general scale, which should not be used as a limitation of the present invention. In addition, in actual production In , the three-dimensional space dimensions of length, width and depth should be included.

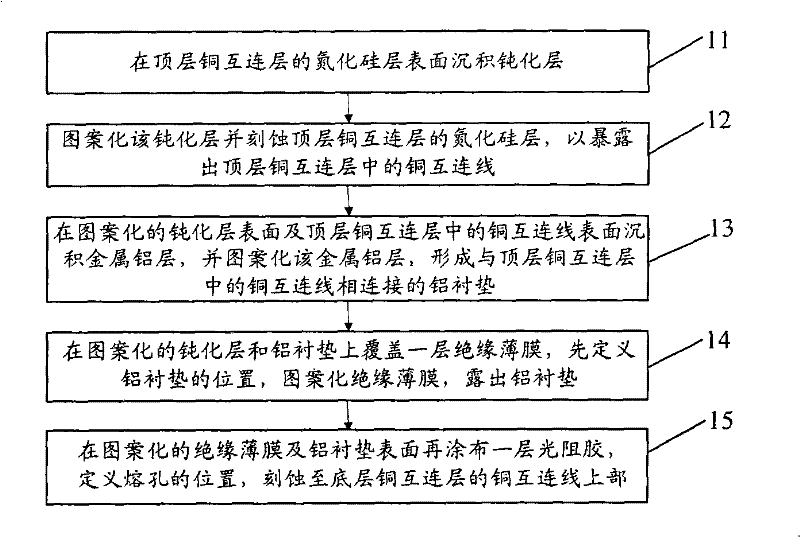

[0060] The manufacturing method of the fuse on the copper interconnection layer in the present invention comprises the following steps:

[0061] Step 31, first depositing a passivation layer on the surface of the silicon nitride layer of the top copper interconnection laye...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More