Substrate structure and manufacturing method thereof

A substrate structure and manufacturing method technology, applied in the direction of microstructure technology, microstructure devices, manufacturing microstructure devices, etc., can solve the problems of increasing product cost, affecting stress-sensitive devices, micromechanical devices and circuit manufacturing processes, etc. , to improve performance and avoid stress

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

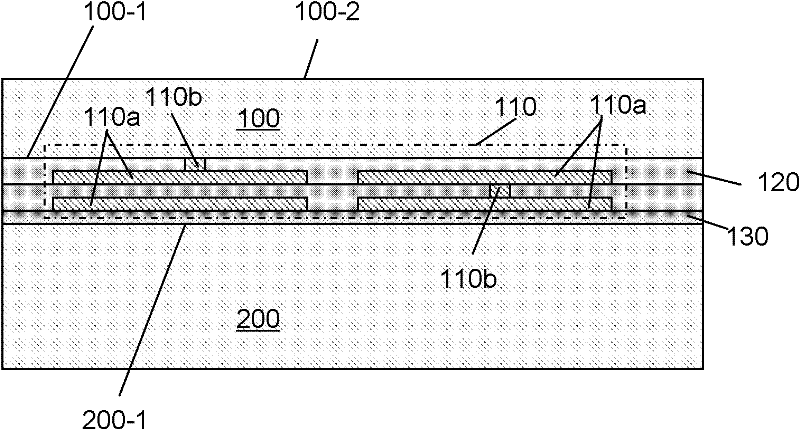

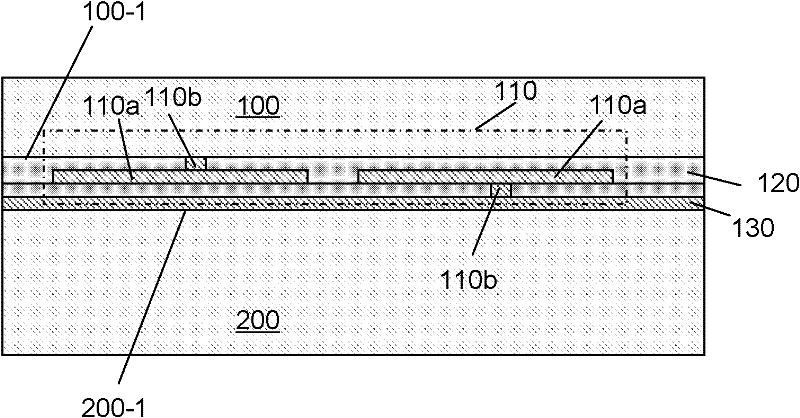

[0066] refer to figure 1 , figure 2 , is an embodiment of the substrate structure in which the bonding layer is an insulating layer and a conductive layer in this embodiment. As shown in the figure, the substrate structure includes:

[0067] The first substrate 100 and the second substrate 200 arranged oppositely;

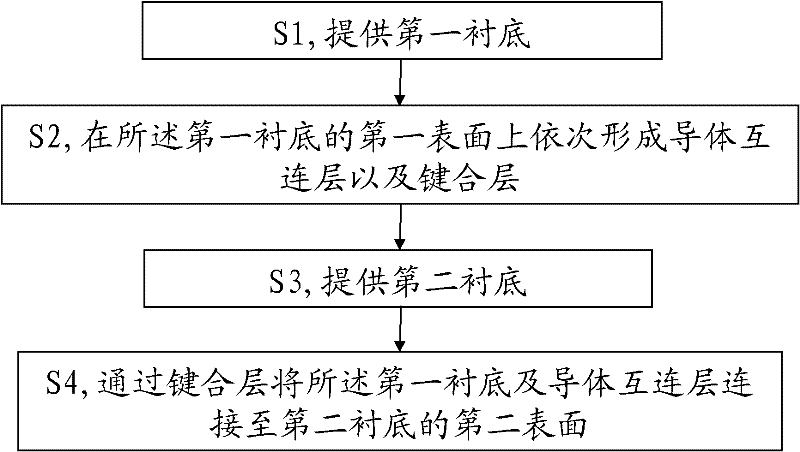

[0068] The first surface 100-1 of the first substrate 100 faces the second surface 200-1 of the second substrate 200, and the first surface 100-1 is sequentially provided with a conductor interconnection layer 110 and a bonding layer 130;

[0069] The bonding layer 130 connects the first substrate 100 and the conductor interconnection layer 110 with the second substrate 200 .

[0070] Among them, such as figure 1 As shown, the bonding layer 130 may be an insulating layer, and may be a non-conductive material, such as silicon oxide, silicon oxynitride, or undoped amorphous silicon, or other suitable materials. In the embodiment where the bonding layer 130 is an...

Embodiment 2

[0093] The following will only describe the aspects that the second embodiment differs from the first embodiment. The parts not described should be considered to be performed by the same steps, methods or processes as those in Embodiment 1, and thus will not be repeated here.

[0094] refer to Figure 7 , Figure 8 , is an embodiment of the substrate structure in which the bonding layer is an insulating layer and a conductive layer in the second embodiment, and may further include an isolation region penetrating the first substrate on the basis of the substrate structure of the first embodiment, as shown in FIG. As shown, specifically, the substrate structure includes:

[0095] The first substrate 100 and the second substrate 200 arranged oppositely;

[0096] Through the isolation region 140 of the first substrate 100, the plurality of isolation regions 140 separate the first substrate 100 into mutually insulated regions;

[0097] The first surface 100-1 of the first subst...

Embodiment 3

[0110] The following will only describe the aspects that the third embodiment differs from the first embodiment. The parts not described should be considered to be performed by the same steps, methods or processes as those in Embodiment 1, and thus will not be repeated here.

[0111] Figure 9 , Figure 10 It is an embodiment of the substrate structure in which the bonding layer is an insulating layer and a conductive layer in Embodiment 3. On the basis of the substrate structure in Embodiment 1 or Embodiment 2, it may further include the first substrate in the second substrate The cavity 150 or the second cavity 152 between the first surface 100 - 1 and the second surface 200 - 1 , or further includes a combination of the first cavity 150 and the second cavity 152 .

[0112] like Figure 9 As shown, specifically, in some embodiments, the substrate structure includes:

[0113] The first substrate 100 and the second substrate 200 arranged oppositely;

[0114] The first sur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More