Flat and lug combined bidirectional diode chip and manufacturing process thereof

A bidirectional diode and manufacturing process technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems that the chip performance is difficult to achieve the desired effect, the amount of acid used is uncontrollable, and the environment is damaged. It is not easy to break , reduced fragmentation rate, and wide adaptability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

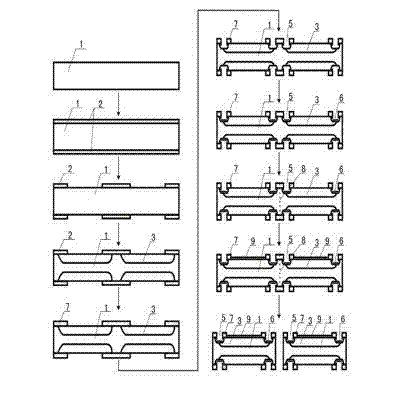

[0030] Below in conjunction with accompanying drawing, the present invention is described in further detail:

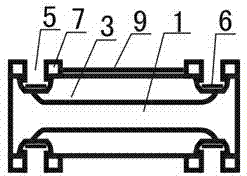

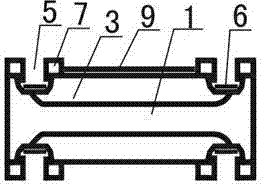

[0031] Such as figure 1 As shown, the flat and platform combined bidirectional diode chip of the present invention is processed from a P-type original silicon chip 1, and both sides of the chip are provided with a primary oxide layer near both ends (, figure 1 not visible in, see figure 2 In the primary oxide layer 2), the two sides of the chip are also provided with a phosphorus diffusion layer 3, and a secondary oxide layer is also provided on the primary oxide layer and the phosphorus diffusion layer 3. The secondary oxide layer and the primary oxide layer form an overlapping oxide layer 7. A mesa groove 5 is opened in the area where the oxide layer 7 overlaps, and a silicon nitride passivation layer 6 is arranged on the mesa groove 5, and nickel layers 9 are also arranged on the surface layers on both sides of the chip.

[0032] Such as figure 2 As shown, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More