A testing device for a phase-change memory cell array

A unit array and testing device technology, applied in the field of micro-nano electronics, achieves the effects of simple structure, flexible operation, and accurate electrical characteristic parameters

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

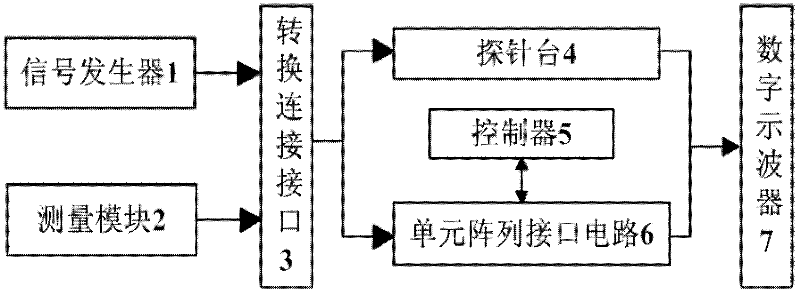

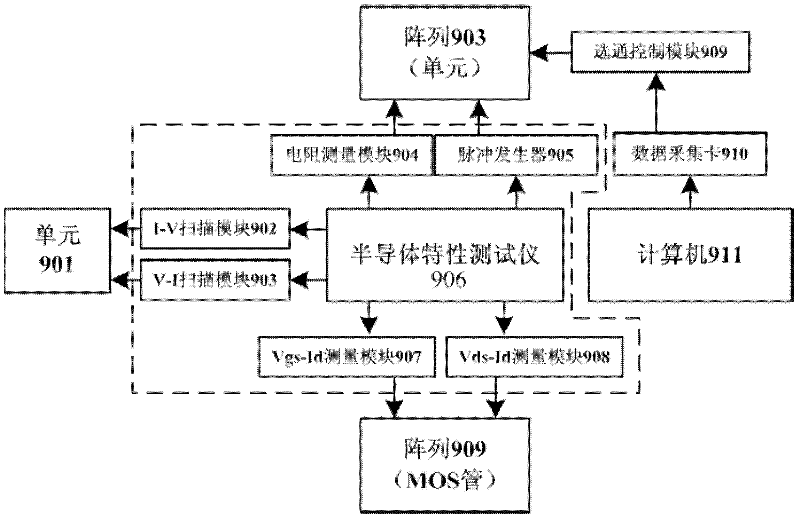

[0035] figure 2 An example of a phase-change memory cell array testing device, the signal generator 1 adopts a pulse signal generator 905, and the measurement module 2 adopts an I-V scanning module 902, a V-I scanning module 903, and a resistance measurement module 904 integrated in a semiconductor characteristic tester 909 , Vgs-Id measurement module 907, Vds-Id measurement module 908, wherein I-V scanning module 902, V-I scanning module 903 are used for the test of unit 901, resistance measurement module 904, pulse generator 905 are used for the unit test in the array, Vgs -Id measurement module 907, Vds-Id measurement module 908 is used for the test of the MOS tube in the array; The conversion connection interface adopts the integrated source and measurement unit SMU integrated in the semiconductor characteristic tester; the probe station 4 connects the unit to be tested 901 into the test device, the unit array interface circuit 6 connects the array 909 or 903 to be tested...

Embodiment 2

[0055] The unit under test adopts such as Figure 7 The phase-change memory unit shown, the thickness of each layer of film is: the lower electrode TiW film 100nm; the second layer of SiO 2 Thin film 150nm; third layer GST thin film 100nm; fourth layer SiO 2 The thin film is 150nm; the upper electrode TiW thin film is 150nm.

[0056] Initial resistance test. Use the DC voltage scanning function of the semiconductor characteristic tester to scan the unit from 0V to 0.2V with a step size of 0.1V, and the measured resistance is 283.7K ohms, indicating that the unit is conductive and in an amorphous state.

[0057] Initialize the unit. After applying a single pulse with a height of 1.5V and a width of 150ns to the cell, the measured resistance is 16K ohms, indicating that the cell has been initialized to a crystalline state.

[0058] Test unit DC I-V characteristics. Apply a write pulse excitation to the unit, the amplitude is 4.6V, the pulse width is 50ns, the falling edge i...

Embodiment 3

[0061] Select an array of 1T1R structure with a MOS tube width-to-length ratio of 50u:500n, and use the cell array interface circuit 6 to respectively lead out the source, drain and gate of the MOS tubes. Connect the SMU of the Keithley 4200 semiconductor characteristic tester to the gate and drain of the MOS transistor, and the source and substrate of the MOS transistor to ground. Set it to MOS tube module test in the semiconductor characteristic tester, and the test steps are as follows:

[0062] Test the Vgs-Id curve. A sweep voltage of 0-3 V was applied on the gate while the current on the drain was measured. The obtained scanning result curve shows that the MOS tube can work normally, and the threshold voltage is 0.8V.

[0063] Test the Vds-Id curve. The gate is given from 0V to 3V at every 0.5V step, and the drain is scanned from 0-3.3V with a step of 0.05V. The graph of the scanning result shows that the MOS tube can work normally.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More