A processing method for monolithic integration of micro-mechanical structure and integrated circuit

A micro-mechanical structure and integrated circuit technology, applied in micro-structure technology, micro-structure devices, manufacturing micro-structure devices, etc., can solve problems such as affecting device reliability, easy generation of residues on the sidewalls of isolation grooves, affecting processing yields, etc. , to avoid the effect of lateral etching

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

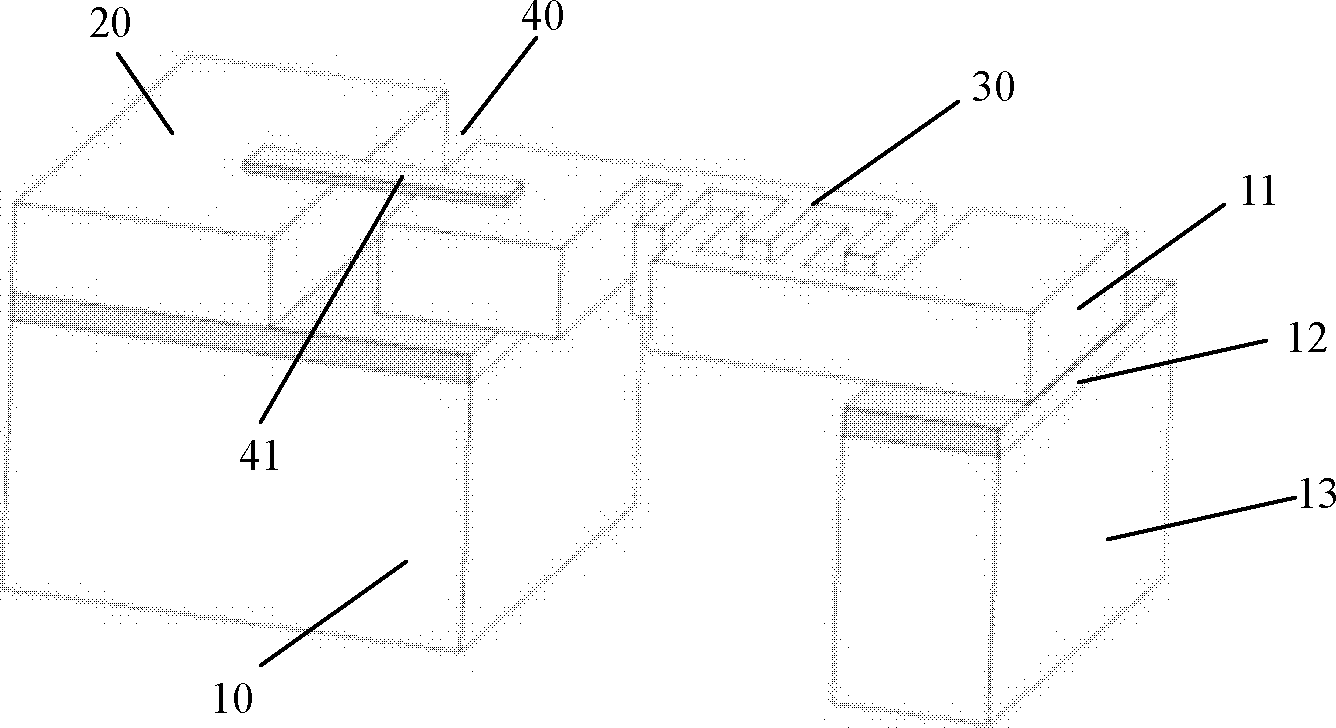

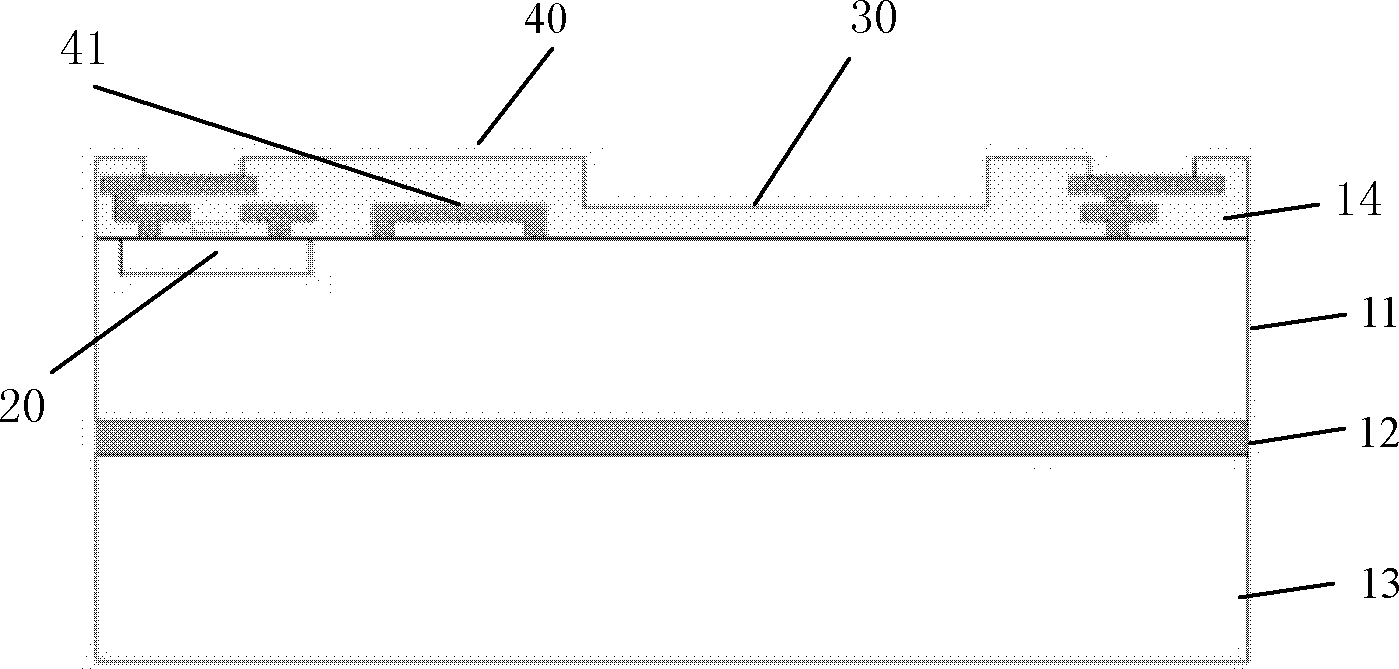

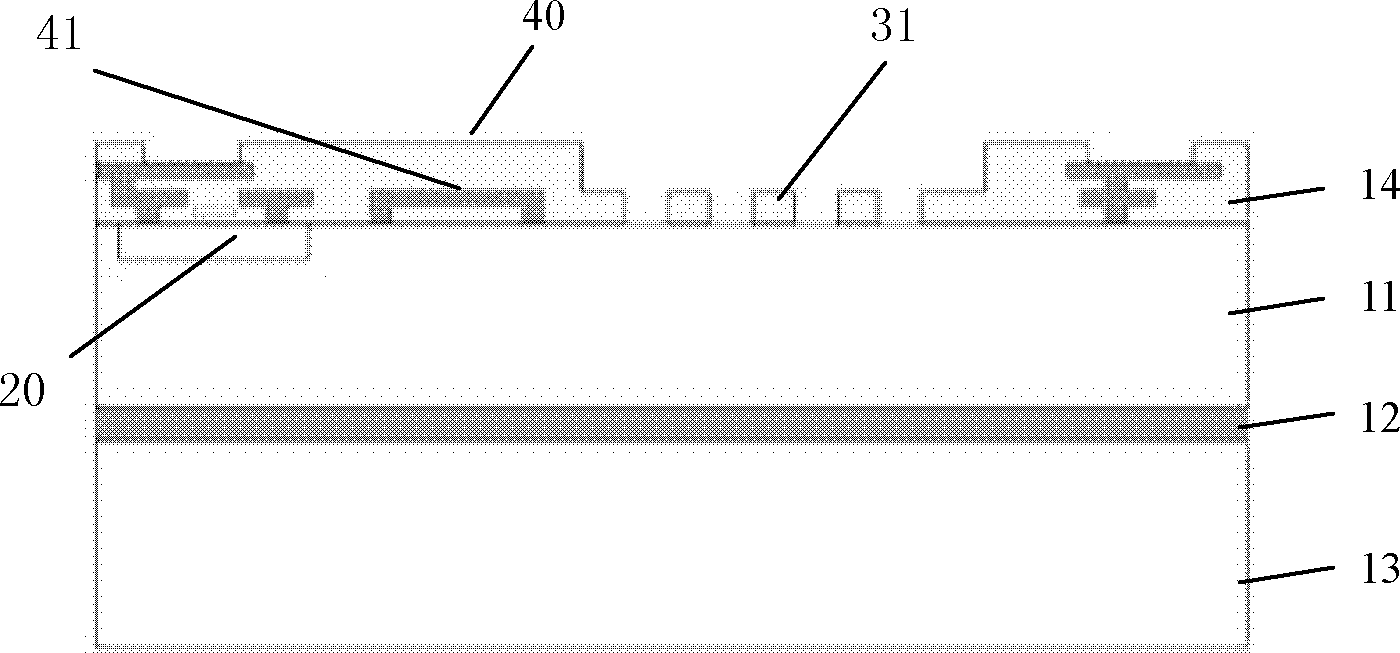

[0020] Such as figure 1 As shown, the present invention integrates and processes MEMS devices on an SOI substrate 10 . The SOI substrate 10 includes a single crystal silicon device layer 11 , a silicon dioxide buried oxide layer 12 and a single crystal silicon substrate layer 13 . The device layer 11 is divided into an integrated circuit area 20 and a MEMS structure area 30 , and an isolation area 40 for separating the integrated circuit area 20 and the MEMS structure area 30 . The silicon in the isolation region 40 is removed to form an isolation groove, so that the silicon structures corresponding to the integrated circuit region 20 and each MEMS structure region 30 are independent from each other to realize electrical isolation. The integrated circuit region 20 and the silicon structures corresponding to each MEMS structure region 30 are mechanic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More