Memory controller and method for controlling commands

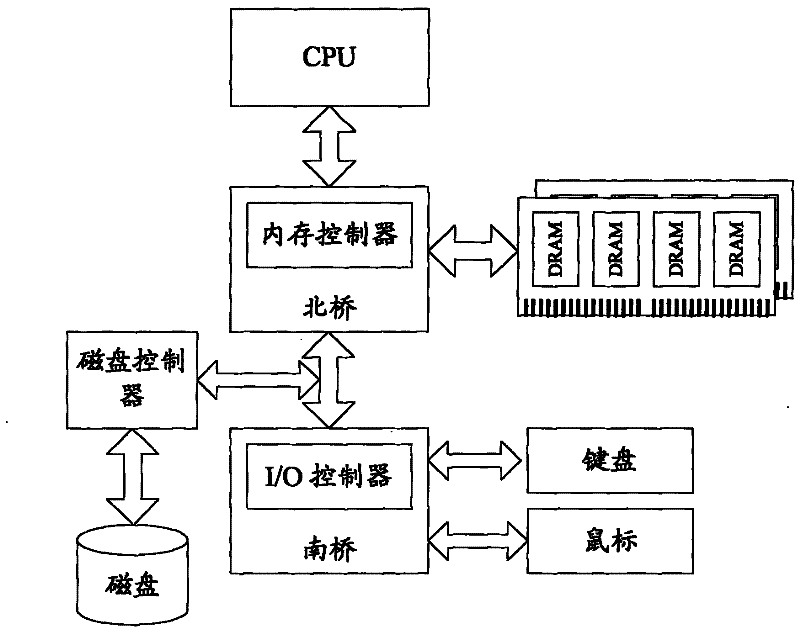

A memory controller and command control technology, applied in static memory, digital memory information, instruments, etc., can solve the problem of high power consumption of memory controller, inability to ensure DDR2SDRAMBANK interleaved access performance at low frequency, and difficulty in meeting the establishment time between logic registers and retention time to achieve high performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0073] This embodiment takes DDR2 SDRAM as an example.

[0074] Such as Figure 10 As shown, the memory controller for DDR2 SDRAM in this embodiment includes a Ctrl module, a Write data path module, and a Read datapath module running at the internal operating frequency of 133MHz, and the memory controller also includes a user interface that can interact with user logic module, and a DRAM IO interface module that connects to the external bus of DDR2 SDRAM and realizes the conversion between the internal operating frequency and the external bus frequency.

[0075] The Ctrl module is mainly used to realize the matching of all DRAM interface protocols, DRAM interface timing parameters, and generate various CMDs; the Ctrl module has two output commands CMD[0] and CMD[1], and the Ctrl module can be based on user logic instructions , according to Figure 9 The state machine shown performs state transition, and generates two 133MHz half-rate ACT commands and RD / RD+AP / WR / WR in parall...

Embodiment 2

[0094] This embodiment takes DDR3 SDRAM as an example. The internal structures of DDR3 SDRAM and DDR2 SDRAM are basically the same, and the interface protocols are also basically the same. Therefore, the implementation of the memory controller for DDR3 SDRAM in this embodiment is basically the same as that for DDR2 SDRAM memory controller in Embodiment 1.

[0095] Such as Figure 12 As shown, the memory controller for DDR3 SDRAM in this embodiment includes a Ctrl module, a Write data path module, and a Read datapath module running at the internal operating frequency of 167MHz, and the memory controller also includes a user interface that can interact with user logic module, and a DRAM IO interface module that connects to the external bus of DDR3 SDRAM and realizes the conversion between the internal operating frequency and the external bus frequency.

[0096] The Ctrl module is mainly used to realize the matching of all DRAM interface protocols, DRAM interface timing paramete...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com