Optimizing design method of nanometer technical metal layer map

A metal layer and layout technology, applied in the field of optimized design of nano-process metal layer layout, to achieve the effects of improving manufacturability, optimizing area, reducing the amount of data and correction time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

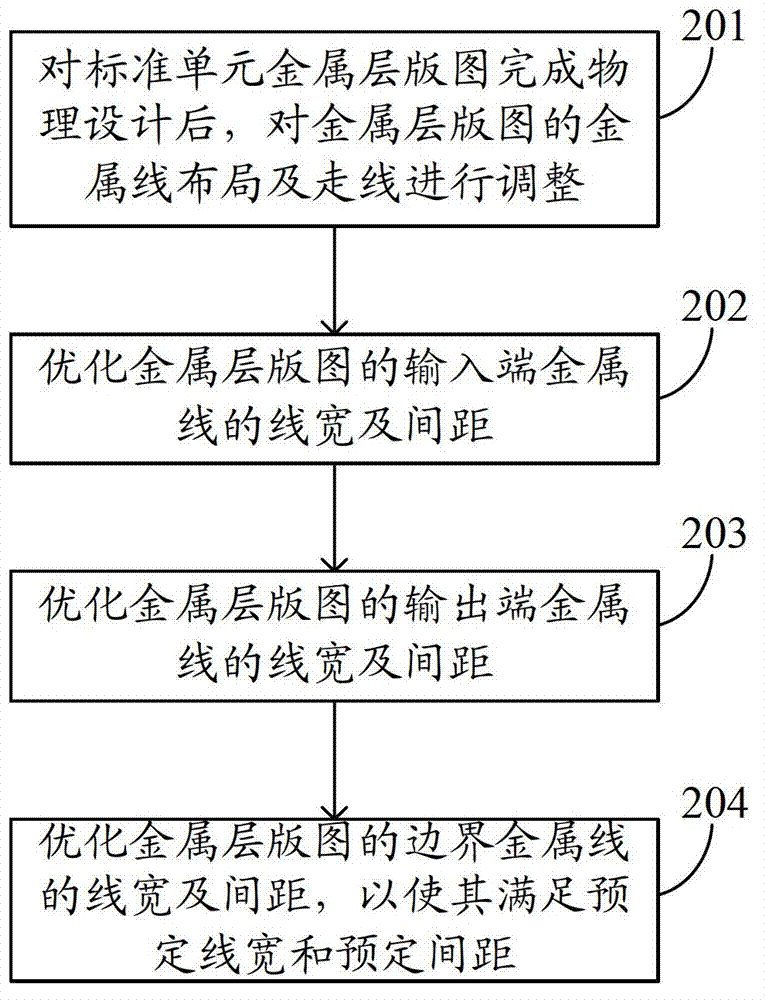

[0047] An embodiment of the present invention provides a method for optimizing the design of a metal layer layout in nanotechnology, the flow chart of which is as follows figure 2 shown, including the following steps:

[0048] Step 201: After completing the physical design of the metal layer layout of the standard cell, adjust the metal line layout and routing of the metal layer layout;

[0049]Specifically, after the physical design of the standard cell metal layer layout is completed, and before the OPC correction process is performed on the metal layer layout, according to the basic principle of OPC correction and the basic structure of the corrected mask pattern, the overall layout of the metal layer layout can be adjusted, The line width, height and spacing of metal lines are optimized.

[0050] Step 202: Optimizing the line width and spacing of the metal line at the input end of the metal layer layout;

[0051] Specifically, the line width of the metal lines at the in...

Embodiment 2

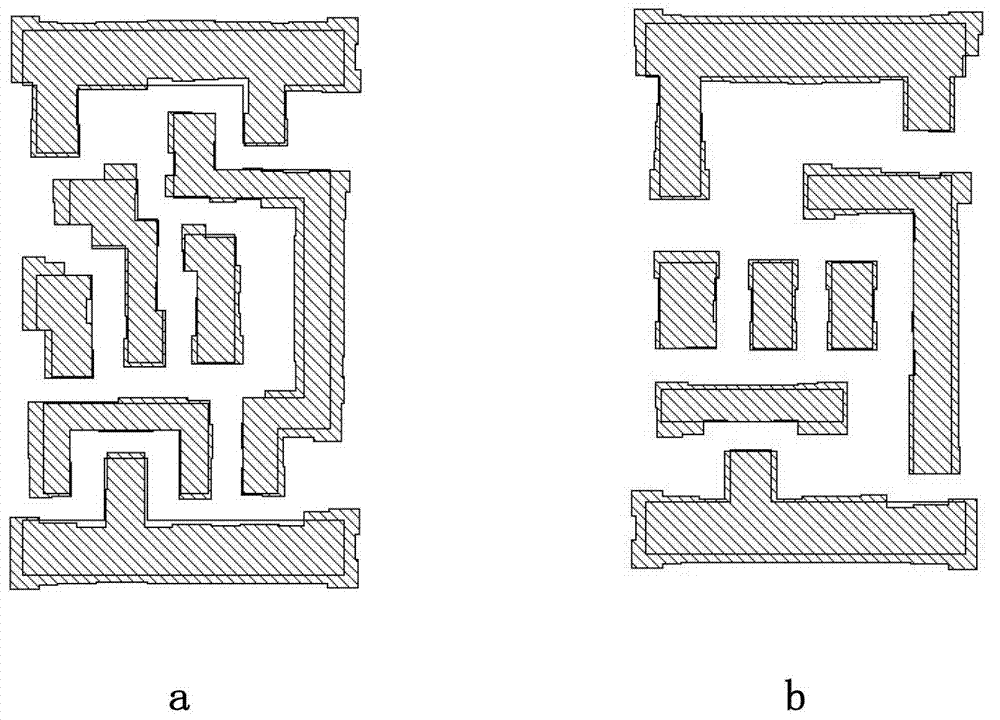

[0063] An embodiment of the present invention provides a method for optimizing the design of a metal layer layout in nanotechnology, the flow chart of which is as follows Figure 4 shown, including the following steps:

[0064] Step 401: reducing redundant corners of metal lines in the metal layer layout;

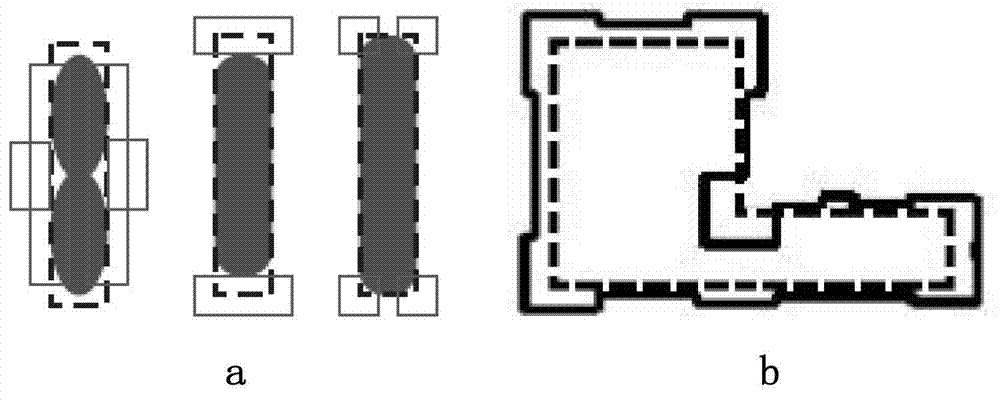

[0065] At the 90° corner of the metal line, due to large distortion due to optical effects, there is a large deviation between the actual graphic and the layout graphic; and for the metal line with multiple corners appearing continuously in a small range, the actual graphic obtained becomes extremely inconsistent. Rules, which affect the manufacturability of the chip, therefore, need to reduce the redundant corners of the metal lines in the metal layer layout.

[0066] Specifically, reducing the redundant corners of the metal lines of the metal layer layout may include the following steps:

[0067] For metal wires connecting multiple MOS tube ports, set the metal wire con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More