N-channel metal oxide semiconductor (NMOS) transistor and forming method thereof

A technology of transistors and semiconductors, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of limited performance improvement of transistors, small improvement of carrier mobility, limited stress, etc., and achieve the goal of improving mobility Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

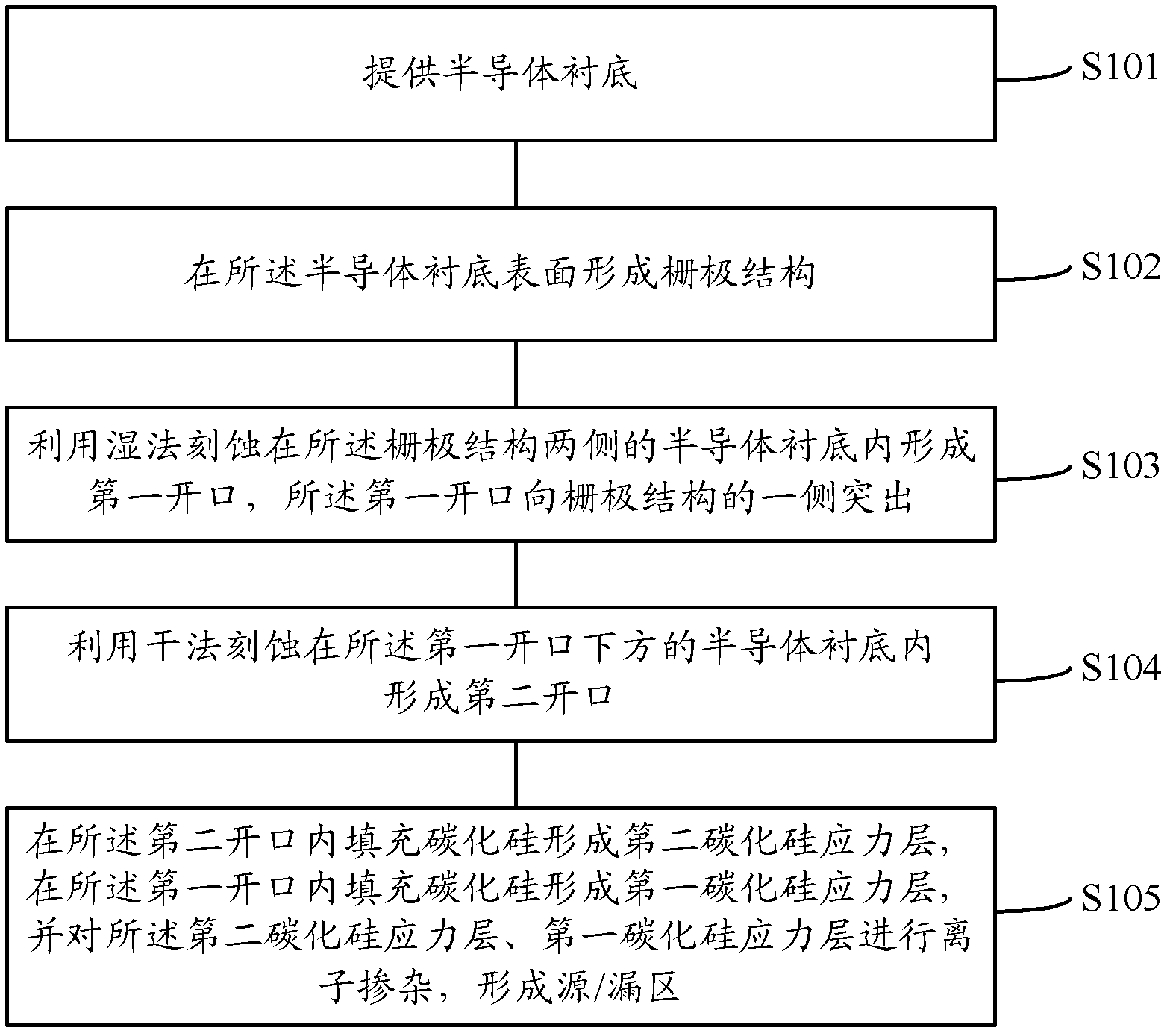

[0056] Please refer to figure 2 , is a schematic flowchart of the method for forming an NMOS transistor according to the first embodiment of the present invention, specifically including:

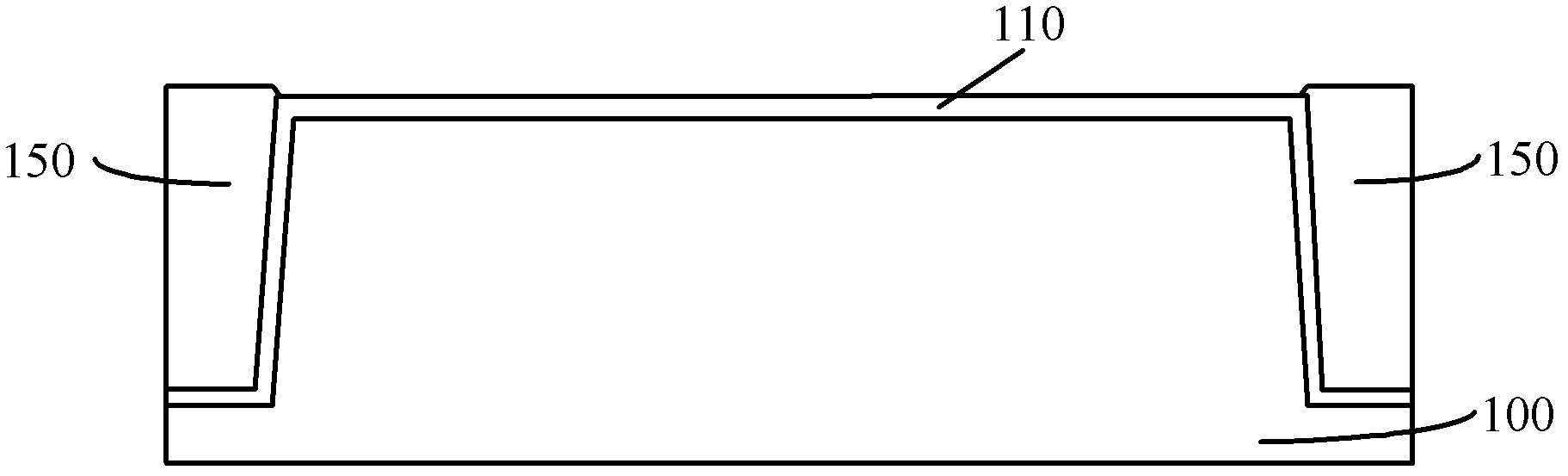

[0057] Step S101, providing a semiconductor substrate;

[0058] Step S102, forming a gate structure on the surface of the semiconductor substrate;

[0059] Step S103, using wet etching to form first openings in the semiconductor substrate on both sides of the gate structure, and the first openings protrude toward one side of the gate structure;

[0060] Step S104, forming a second opening in the semiconductor substrate below the first opening by dry etching;

[0061] Step S105, filling the second opening with silicon carbide to form a second silicon carbide stress layer, filling the first opening with silicon carbide to form a first silicon carbide stress layer, and adding the second silicon carbide stress layer, Ion doping is performed on the first silicon carbide stress layer to form ...

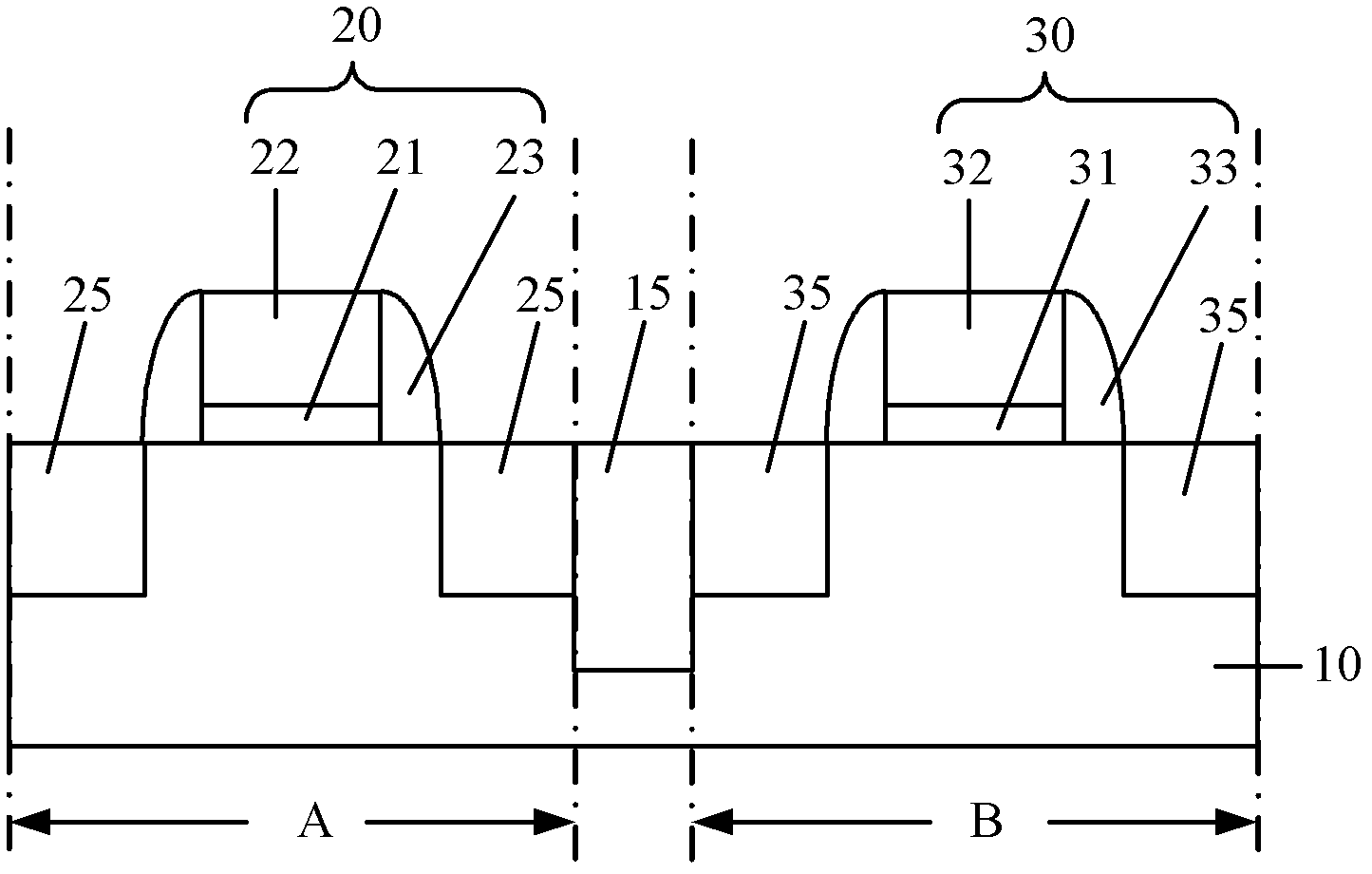

no. 2 example

[0099] Please refer to Figure 11 , is a schematic flow chart of the method for forming an NMOS transistor according to the second embodiment of the present invention, specifically including:

[0100] Step S201, providing a semiconductor substrate;

[0101] Step S202, forming a gate structure on the surface of the semiconductor substrate;

[0102] Step S203, using wet etching to form first openings in the semiconductor substrate on both sides of the gate structure, the first openings protruding to one side of the gate structure;

[0103] Step S204, performing carbon ion doping on the semiconductor substrate below the first opening to form a second silicon carbide stress layer;

[0104] Step S205 , filling the first opening with silicon carbide to form a first silicon carbide stress layer, and performing ion doping on the second silicon carbide stress layer and the first silicon carbide stress layer to form source / drain regions.

[0105] Figure 12 to Figure 14 It is a sche...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Depth range | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness range | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More