Post-CMOS integrated method for threshold presetting

A MOS tube and threshold technology, applied in gaseous chemical plating, process for producing decorative surface effects, coating, etc., can solve problems such as inability to obtain input results, asymmetric threshold of MOS tube, etc., and reduce process complexity , high yield, reducing the effect of parasitic capacitance and distributed capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

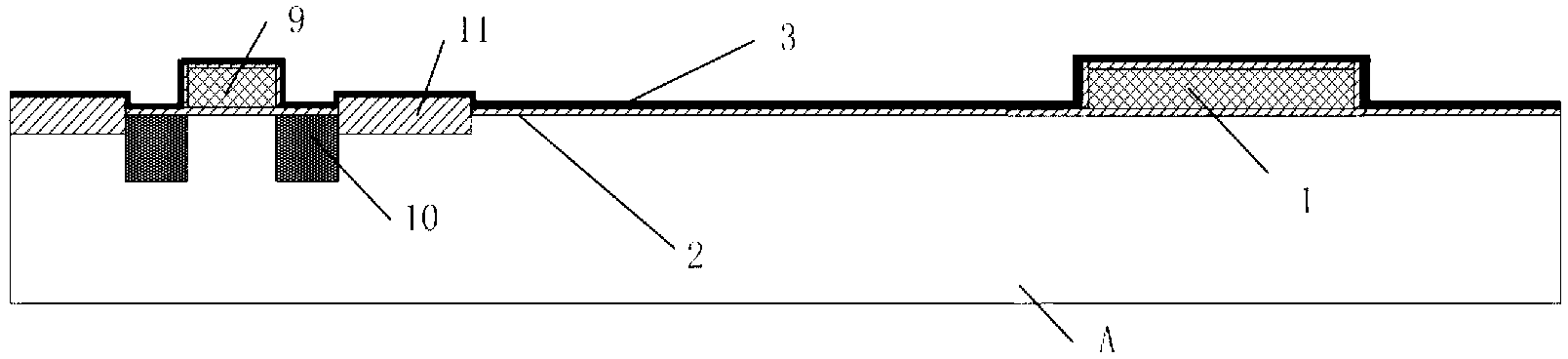

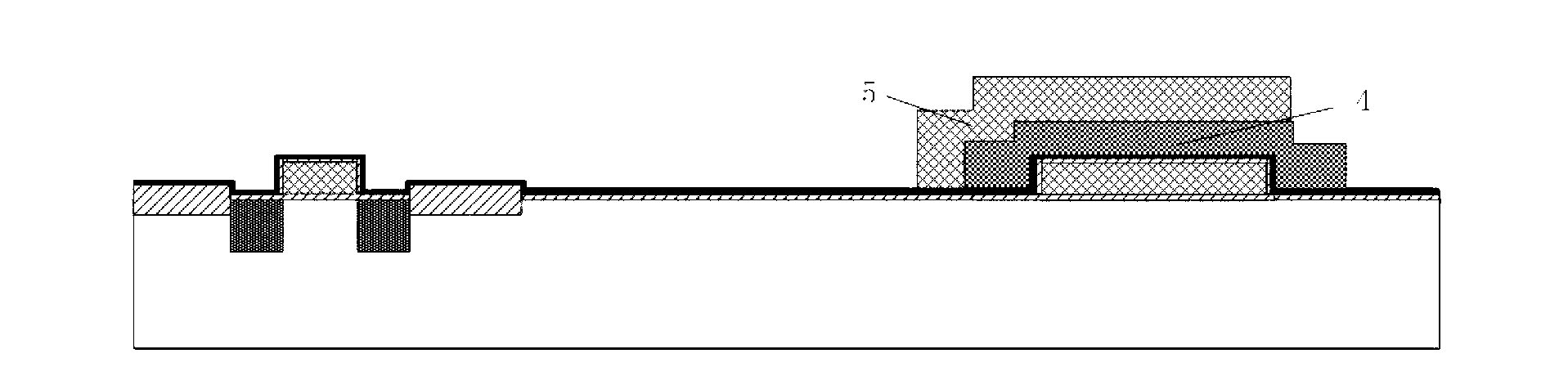

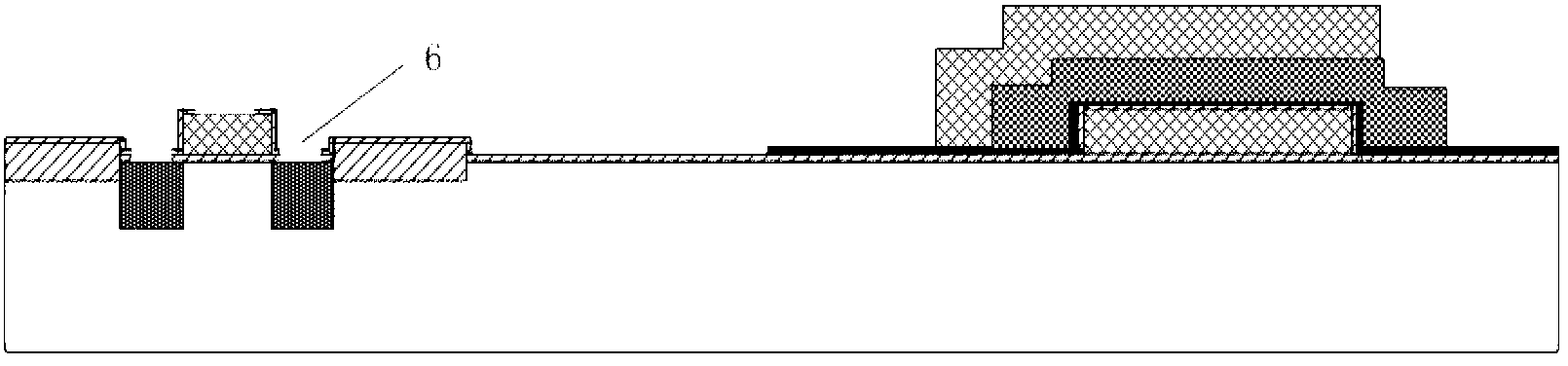

[0034] The present invention will be described in detail below through specific embodiments and accompanying drawings.

[0035] The integration method of the preset threshold value of the present invention is mainly applicable to MEMS device chips made on silicon substrates, including IC parts and movable structures realized by sacrificial layer technology, such as accelerometers, gyroscopes and other sensors, adjustable capacitors structure and other actuators. The following takes the preparation of a monolithic integrated planar capacitive resonator as an example to illustrate.

[0036] First estimate the stress that the MEMS process will introduce.

[0037] When estimating the amount of threshold drift caused by stress, those skilled in the art can obtain the stress value through simulation according to the materials and processes selected by MEMS, and then find other literature on the influence of stress in the field of microelectronic IC devices, and compare the numerica...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More