Structure and fabrication method of vertical junction-free gate-ring mosfet device

A junction ring and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as insufficient gate control capability, excessive leakage current, difficult process realization, etc., and achieve the ability to resist short channel effects. The effect of strong, enhanced gate control capability and simple manufacturing process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention is described in detail below in conjunction with accompanying drawing example:

[0023] combine figure 2 . As shown, an n-type silicon wafer substrate 101 with crystal orientation is prepared with a thickness of 100 nm.

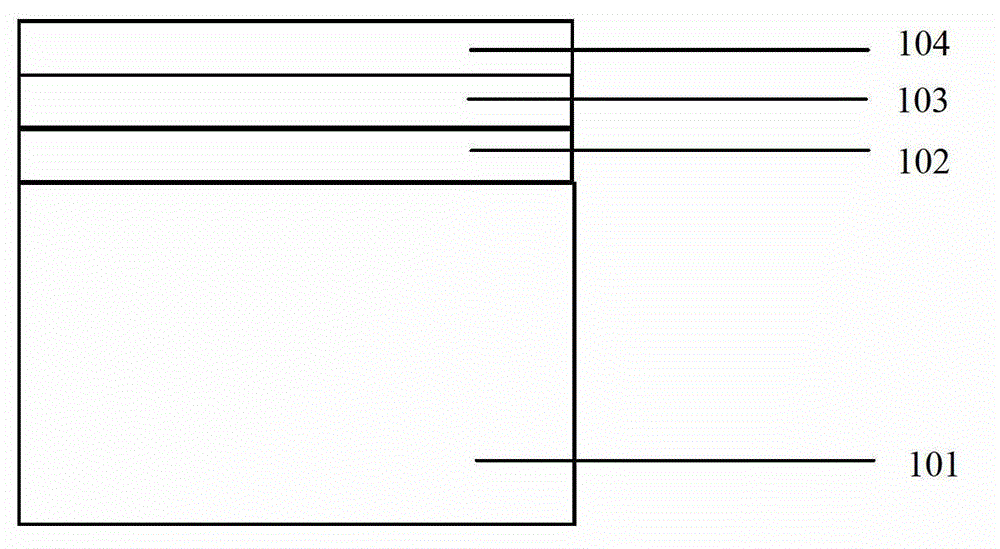

[0024] combine image 3 . On the n-type silicon wafer 101, SiO is sequentially deposited 2 layer 102, SiGe layer 103 and SiO 2 Layer 104. Of which SiO 2 layer 102, SiGe layer 103 and SiO 2 The thickness of the layer 104 is 20-50 nm.

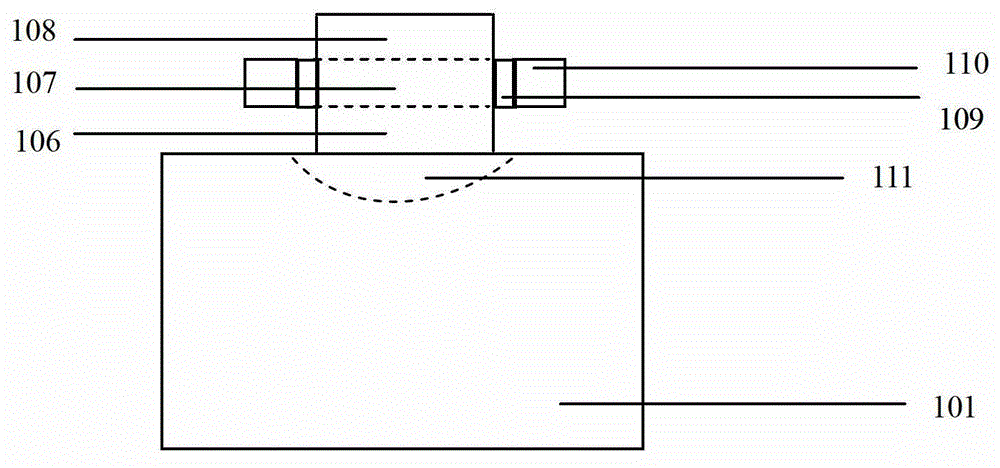

[0025] combine Figure 4 . right image 3 The structure is photolithographically made so that the middle part of the SiO 2 layer 102, SiGe layer 103 and SiO 2 Layer 104 is etched away in its entirety, forming a window. Then, the photoresist is used as a doping mask layer to perform n-type doping implantation on the silicon material, and rapid thermal annealing (RTA) activates the impurities to form the drain region 111 .

[0026] combine Figure 5 . An epitaxial silicon layer 105 i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More