Self-aligned graphene field effect transistor and manufacturing method thereof

A technology of field effect transistors and graphene, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of adverse effects on device characteristics, large sheet resistance, and inapplicability, and achieve good DC and RF performance, Reduced via resistance, good feasibility effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

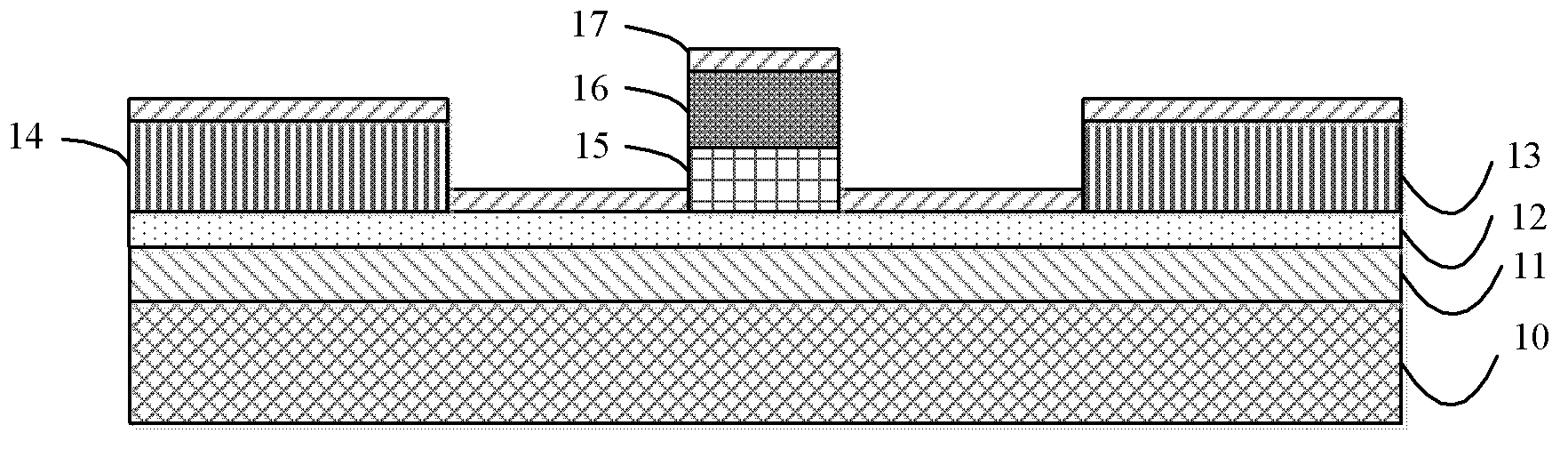

[0038] Such as figure 1 as shown, figure 1 is a schematic diagram of a self-aligned graphene field-effect transistor according to an embodiment of the present invention, and the self-aligned graphene field-effect transistor includes a semiconductor substrate 10, an insulating layer 11, a conductive channel 12, a source electrode 13, a drain electrode 14, a gate dielectric layer 15 , gate metal 16 and self-aligned metal 17 . Wherein, the insulating layer 11 is formed on the semiconductor substrate 10, the conductive channel 12 is formed on the insulating layer 11, the conductive channel 12 is made of graphene, and the source electrode 13 and the drain electrode 14 are respectively formed on both sides of the conductive ch...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More