Patents

Literature

152 results about "Graphene field effect transistors" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

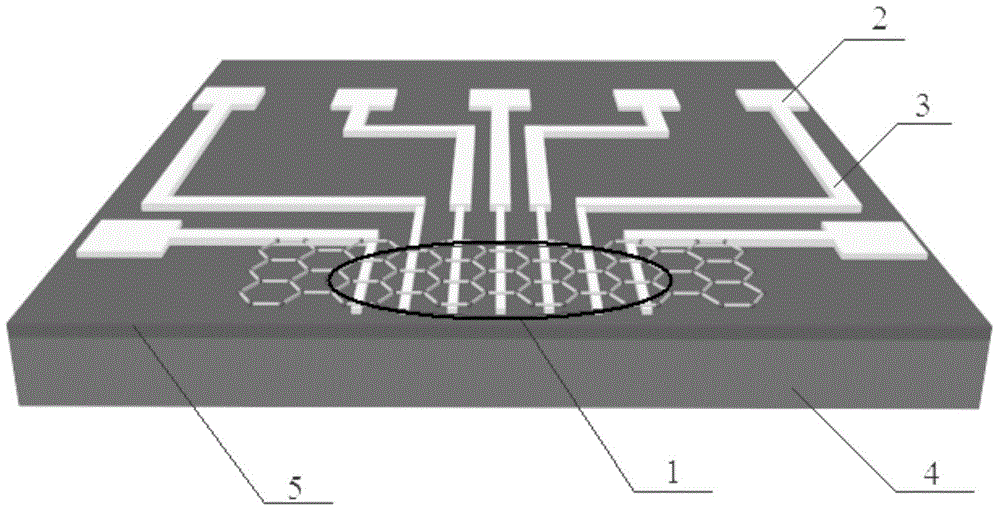

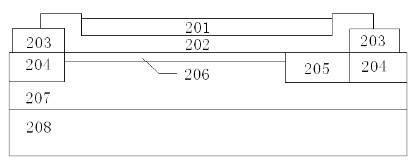

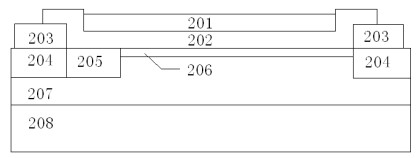

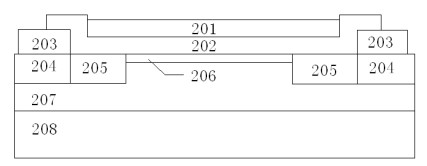

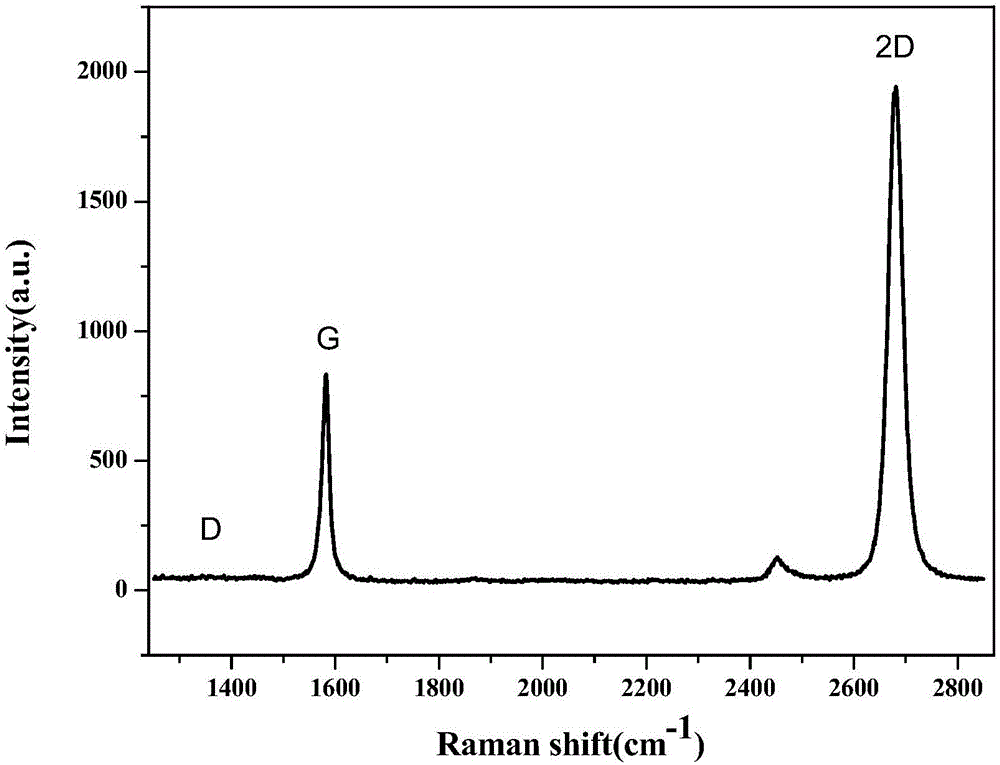

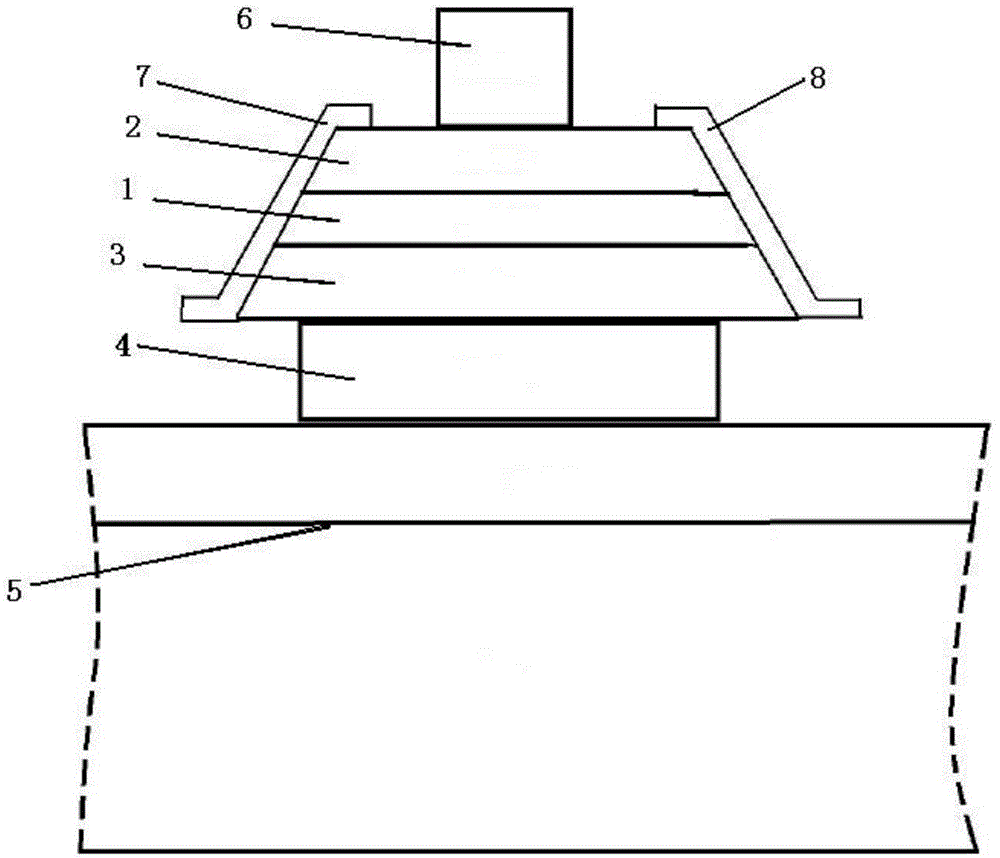

Graphene terahertz wave detector and manufacturing method thereof

InactiveCN104916732ARegulation of transport propertiesImplement detectionFinal product manufacturePhotometry using electric radiation detectorsCapacitanceLow noise

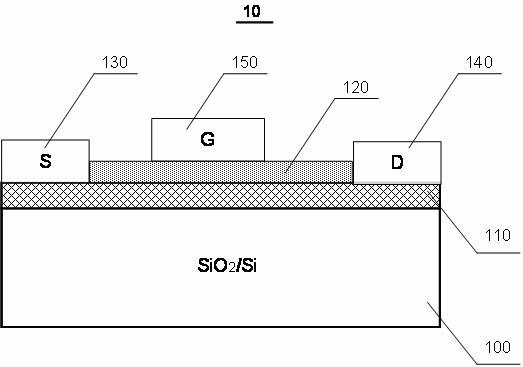

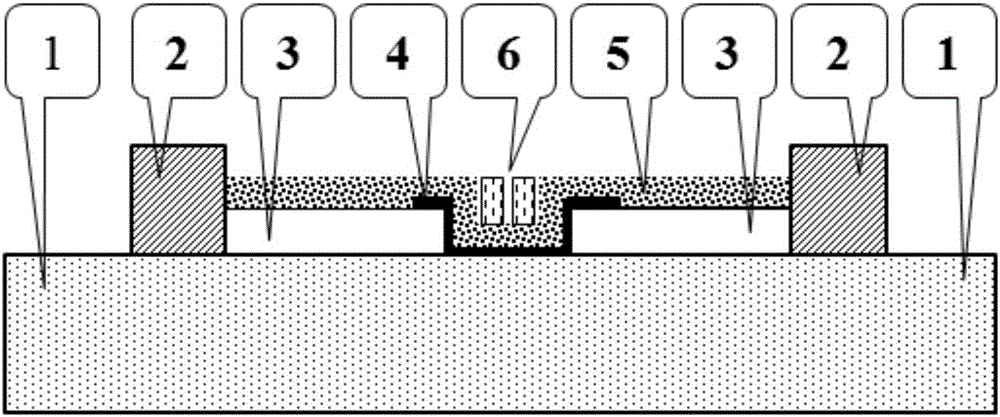

The invention discloses a graphene terahertz wave detector. The graphene terahertz wave detector comprises a graphene field effect transistor and an antenna which can be effectively coupled to terahertz waves. The antenna is in integrated arrangement with the graphene field effect transistor yet is completely independent from the source electrode and the drain electrode of the graphene field effect transistor. According to the invention, through combination between a top grid and a back grid, the transport property of a graphene two-dimensional electron gas is effectively regulated and controlled, and accordingly, the terahertz waves are detected. The two sides of the top grid of the graphene field effect transistor are integrated with a plane antenna which is independent from the source electrode and the drain electrode and can be highly efficiently coupled to the terahertz waves, such that terahertz wave signals are coupled to a grid electrode in the form of capacitance, and the response of the graphene detector to terahertz radiation can be effectively enhanced. The detector can generate photoelectric currents or open-circuit voltages under radiation of the terahertz waves so as to realize room-temperature, high-speed, high-efficiency, high-sensitivity and low-noise detection.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

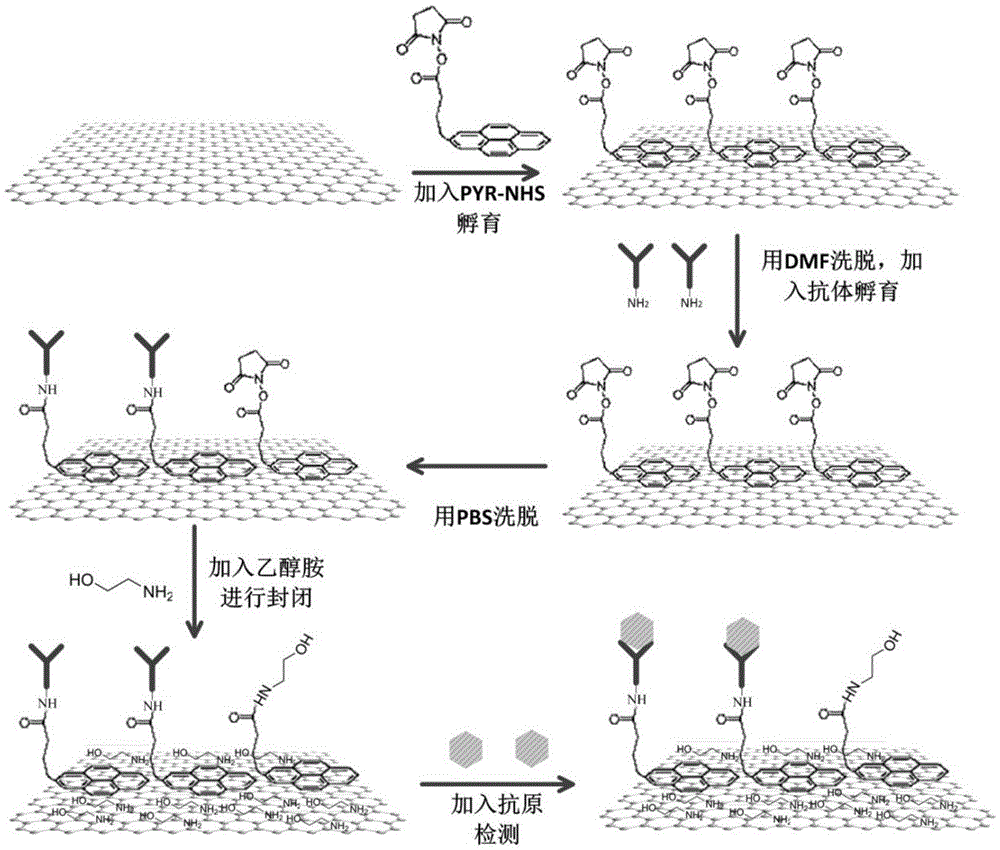

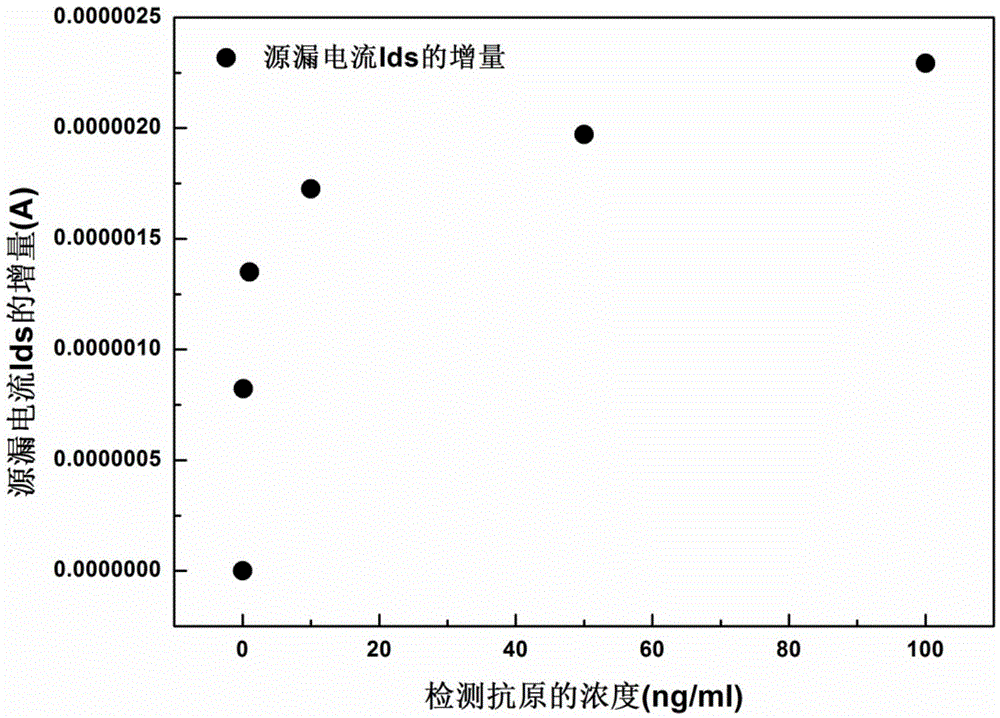

Non-covalently modified graphene field effect transistor-based tumor marker detection sensor and production method thereof

InactiveCN105651845ALittle influence on electrical characteristicsGood electrical propertiesMaterial analysis by electric/magnetic meansInsulation layerMetal electrodes

The invention relates to a non-covalently modified graphene field effect transistor-based tumor marker detection sensor and a production method thereof. The sensor comprises a silica substrate, a graphene channel and a reaction chamber. The production method comprises the following steps: making a metal electrode, carrying out wet transfer on graphene, making the graphene channel and a protection insulation layer of the graphene channel, and modifying the surface of graphene in a non-covalent mode. The sensor has the advantages of convenient making process, simple modification process, easy operation, and high sensitivity and good specificity in application; and the making method can also be used to make most of biosensors of capture probes with amino groups, and the sensor is used to detect target molecules.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

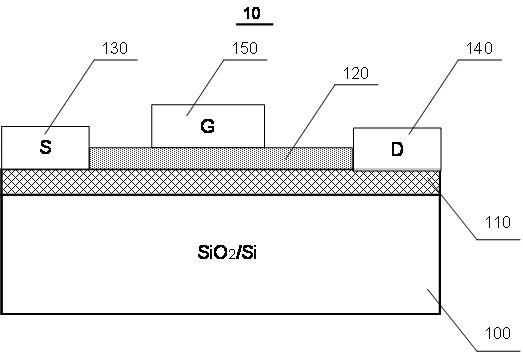

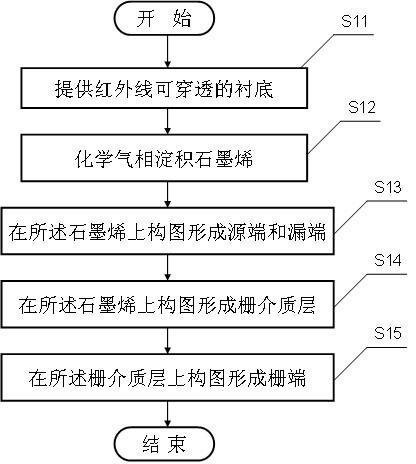

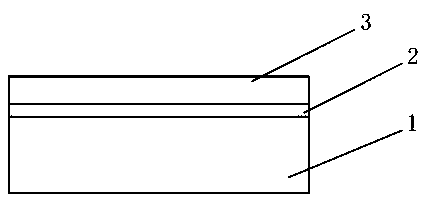

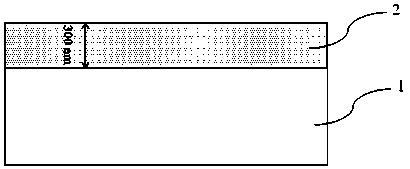

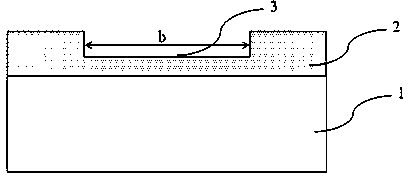

Preparation method of graphene field effect transistor

InactiveCN102184858AHigh sensitivityReduce power consumptionSemiconductor/solid-state device manufacturingChemical vapor deposition coatingInfraredIntegrated circuit manufacturing

The invention belongs to the technical field of field effect transistors, and particularly relates to a preparation method of a graphene field effect transistor. The method comprises the steps of: providing a substrate through which infrared rays can penetrate; carrying out chemical vapor deposition on graphene to form a graphene channel layer; constructing a pattern on the graphene channel layer to form a grid medium layer; and constructing a pattern on the grid medium layer to form a grid end, wherein the graphene channel layer generates a photoconductive effect operatively under the radiation of the infrared rays so as to lead the electric characteristic of the graphene field effect transistor to be changed. In the preparation method, the technique is simple in process and is compatible with an integrated circuit manufacturing technique, the prepared field effect transistor has the advantages that the sensitivity is high, the power consumption is low, the infrared detection function is ultra-light and ultra-stable, the infrared absorbing belt is wide and the adjustability can be achieved according to the practical application needs.

Owner:FUDAN UNIV

Graphene field effect transistor with photoconduction effect and infrared detector

The invention belongs to the technical field of graphene, and particularly discloses a graphene field effect transistor (GFET) with photoconduction effect and an infrared detector. The GFET comprises a graphene channel layer which generates photoconduction effect under infrared radiation operatively so as to change the electric characteristic of the GFET; the GFET is high in sensitivity and low in power consumption. The infrared detector manufactured by using the GFET does not need a refrigerating system, has low operating cost and is ultralight and ultrastable, the infrared absorbing bandwidth of the infrared detector can be adjusted according to the practical application need; and the problem that the traditional infrared detector is manufactured by complicated process and has hypertoxicity are also avoided; in addition, the infrared detector disclosed by the invention is especially suitable for application in sky-survey infrared detection.

Owner:FUDAN UNIV

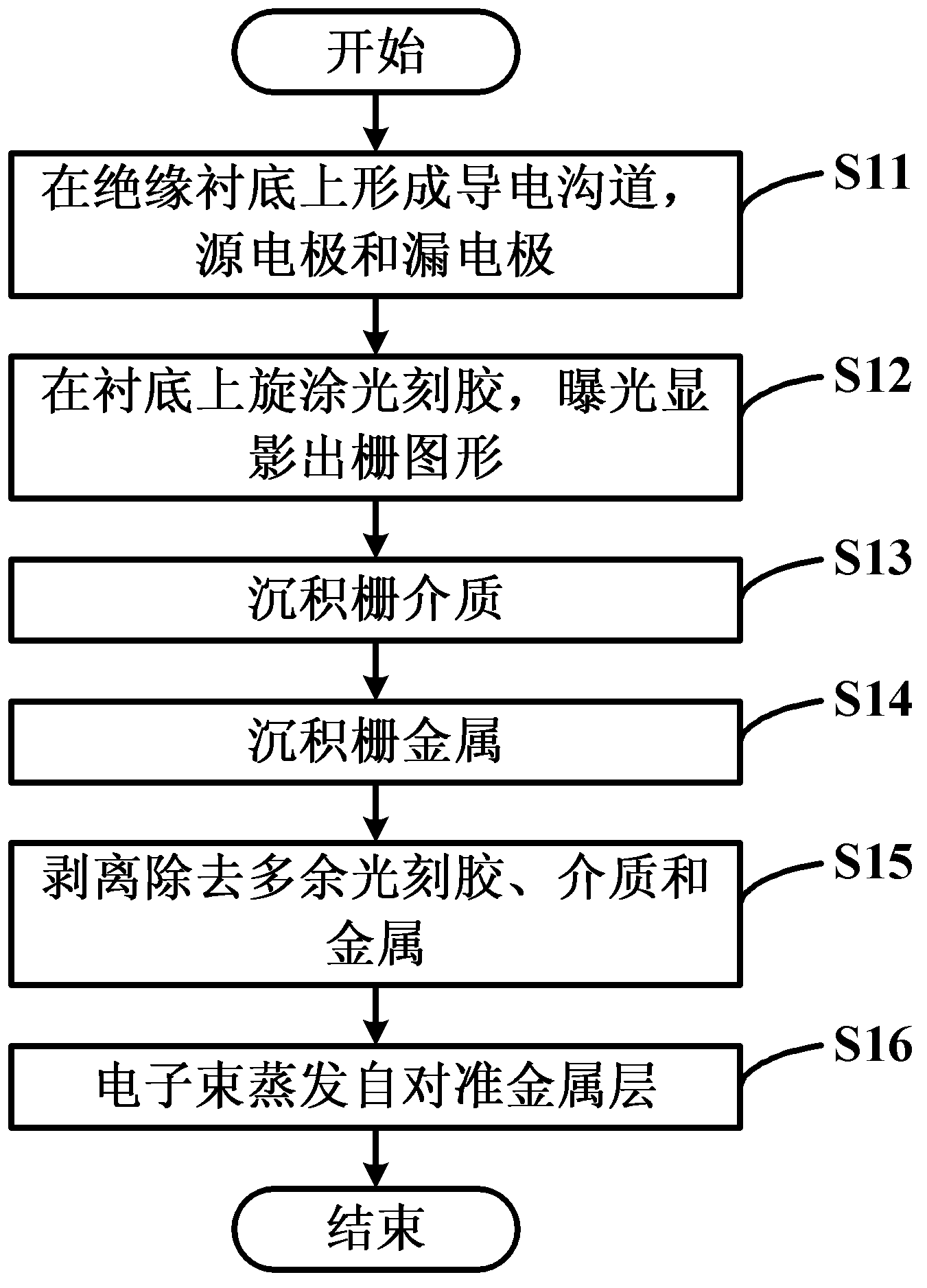

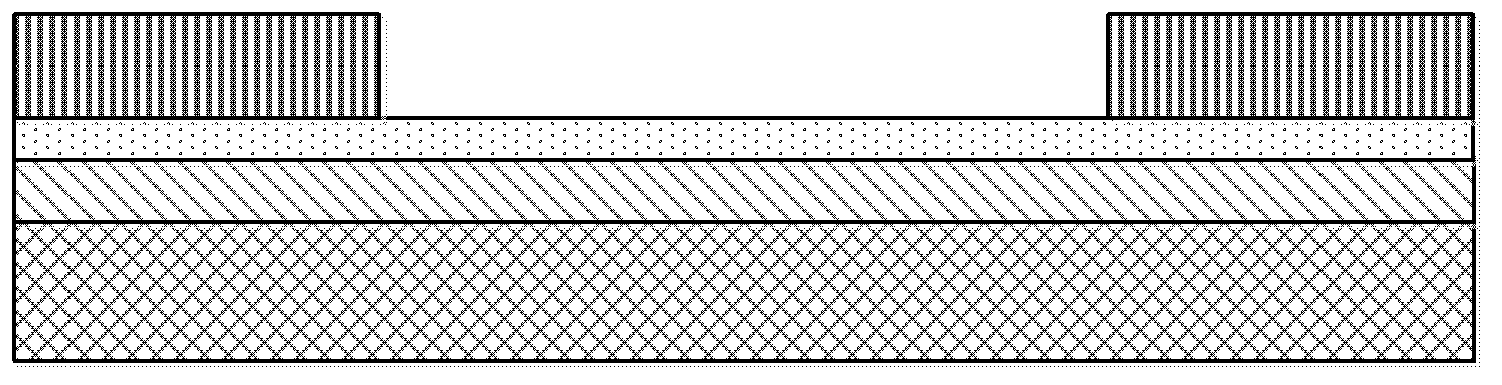

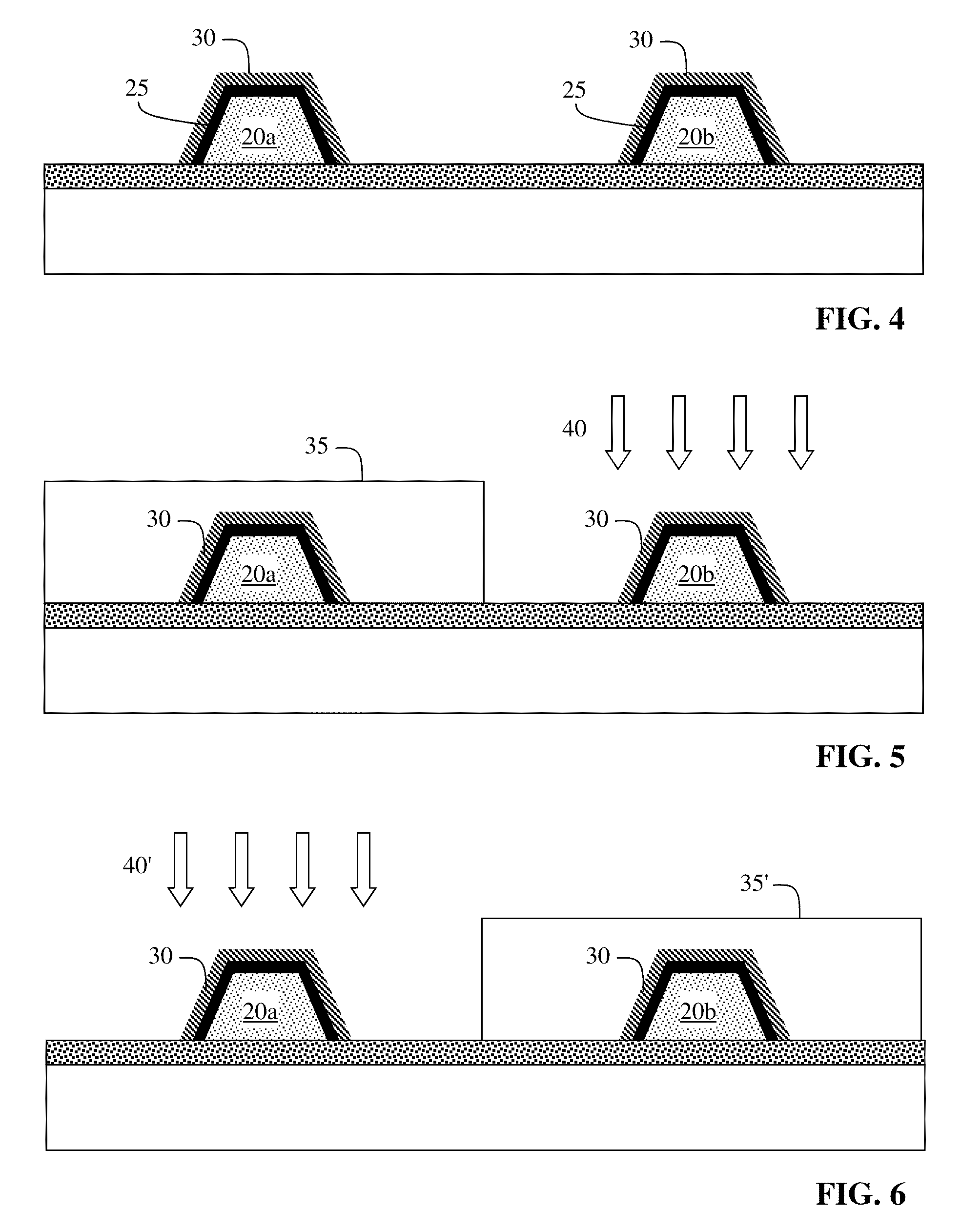

Self-aligned graphene field effect transistor and manufacturing method thereof

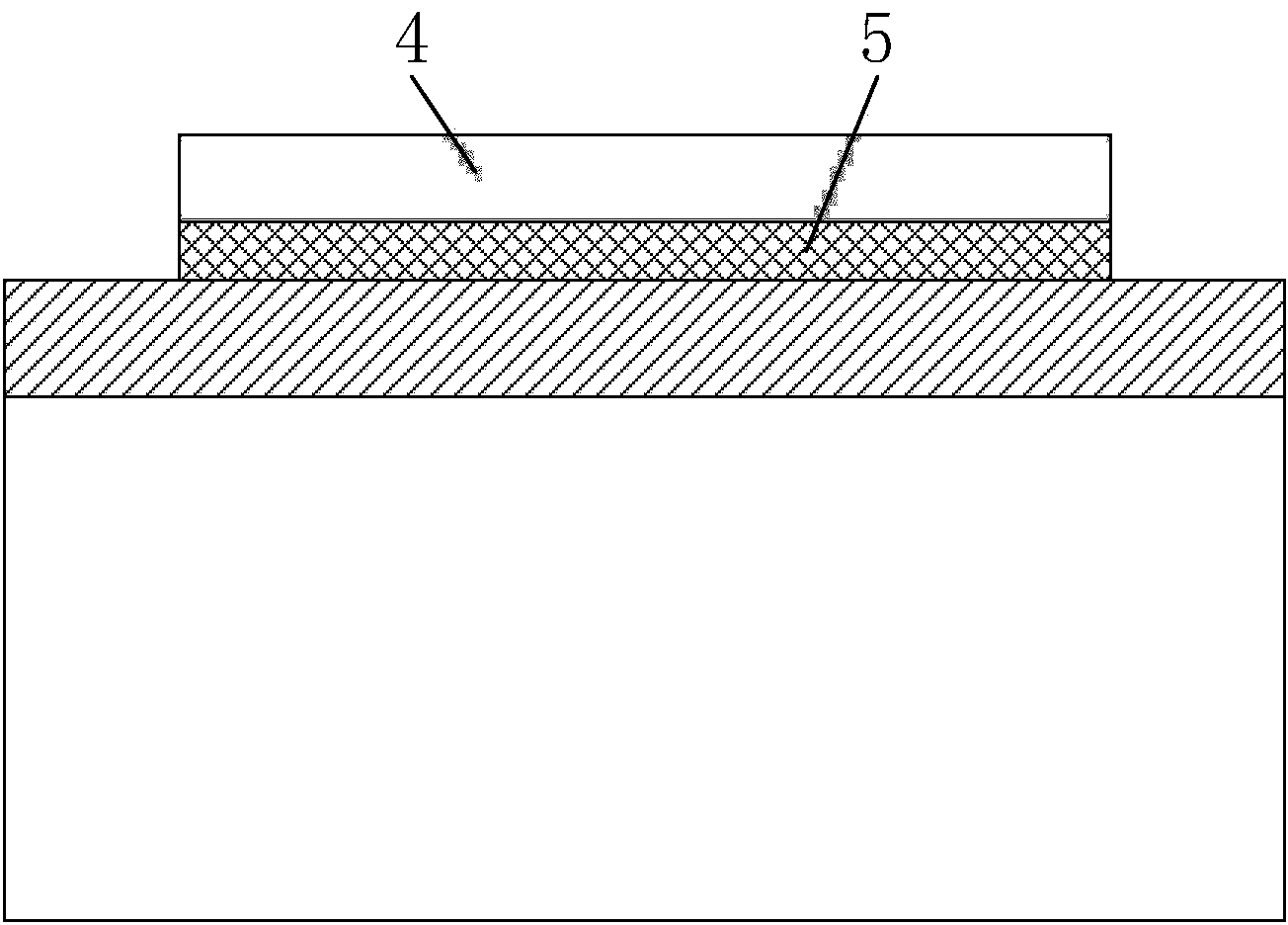

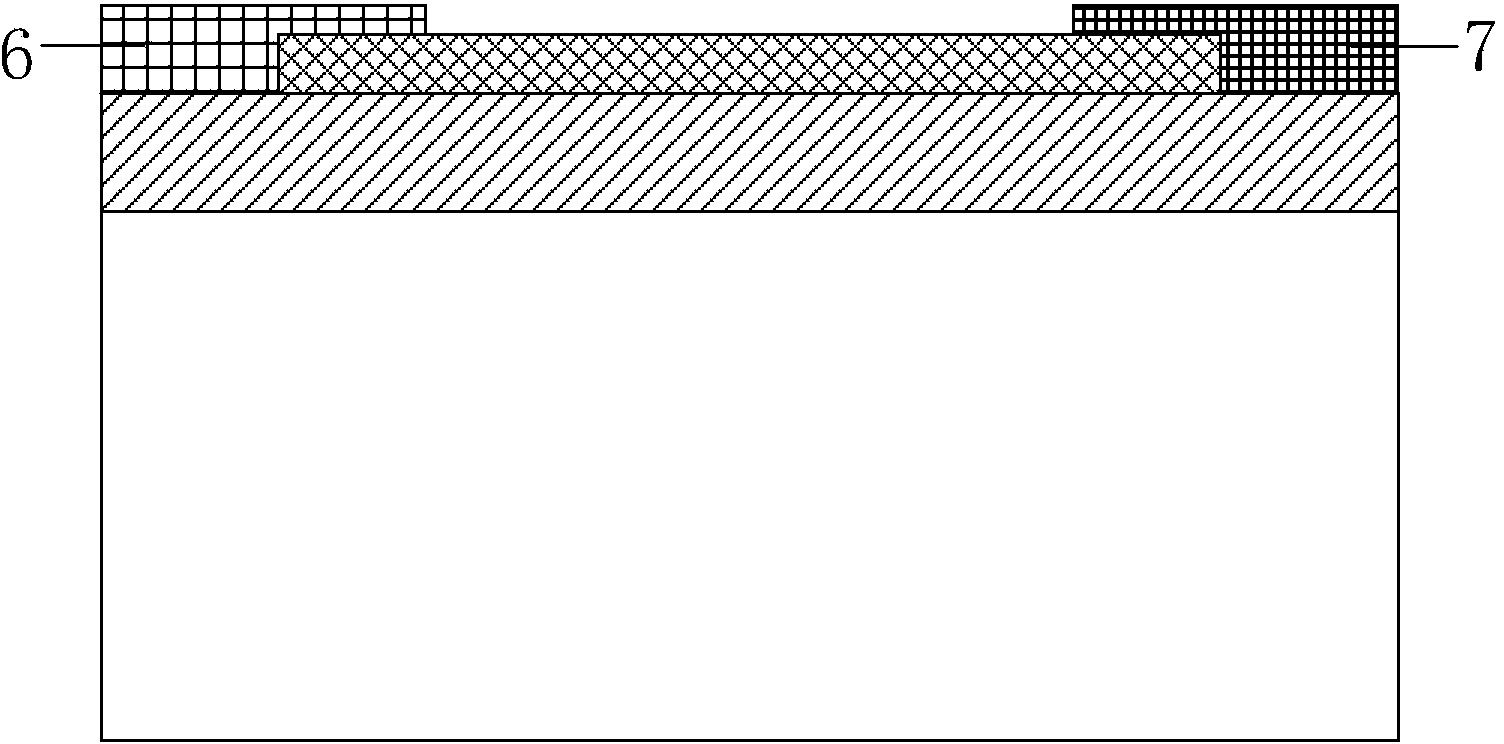

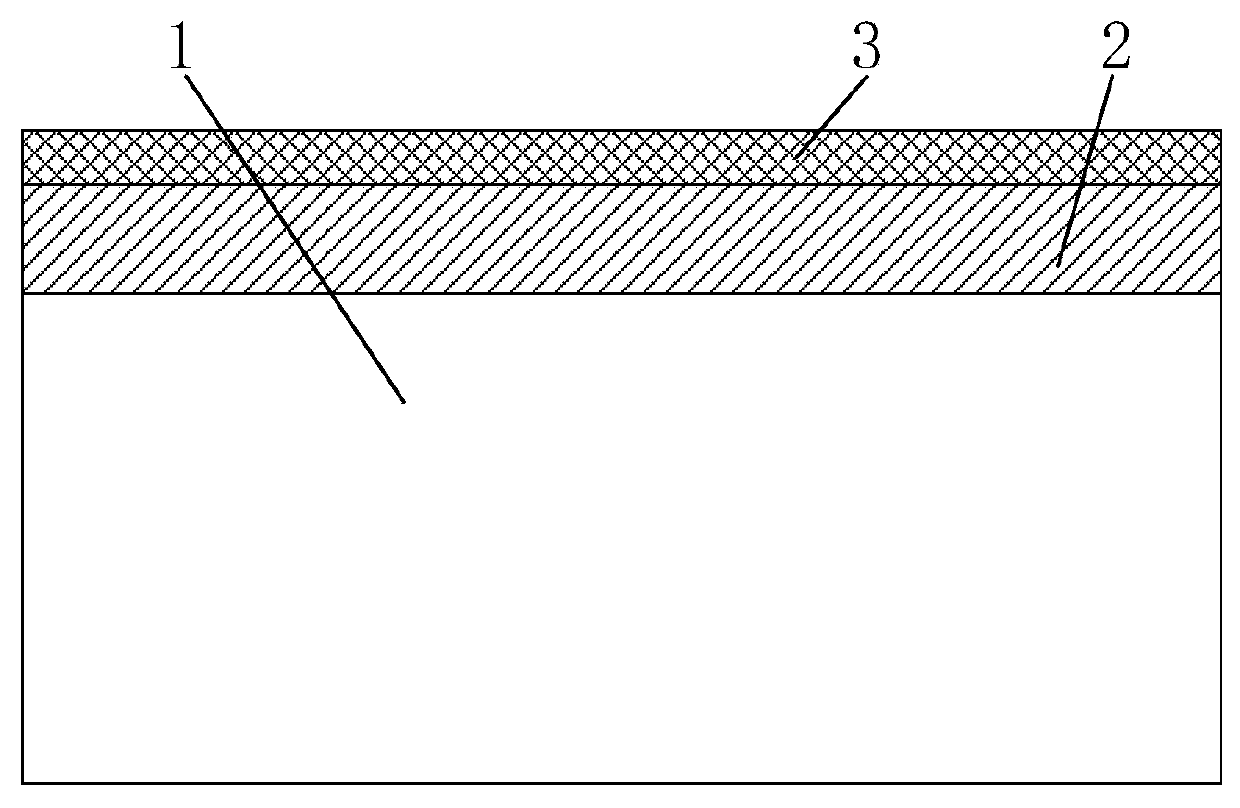

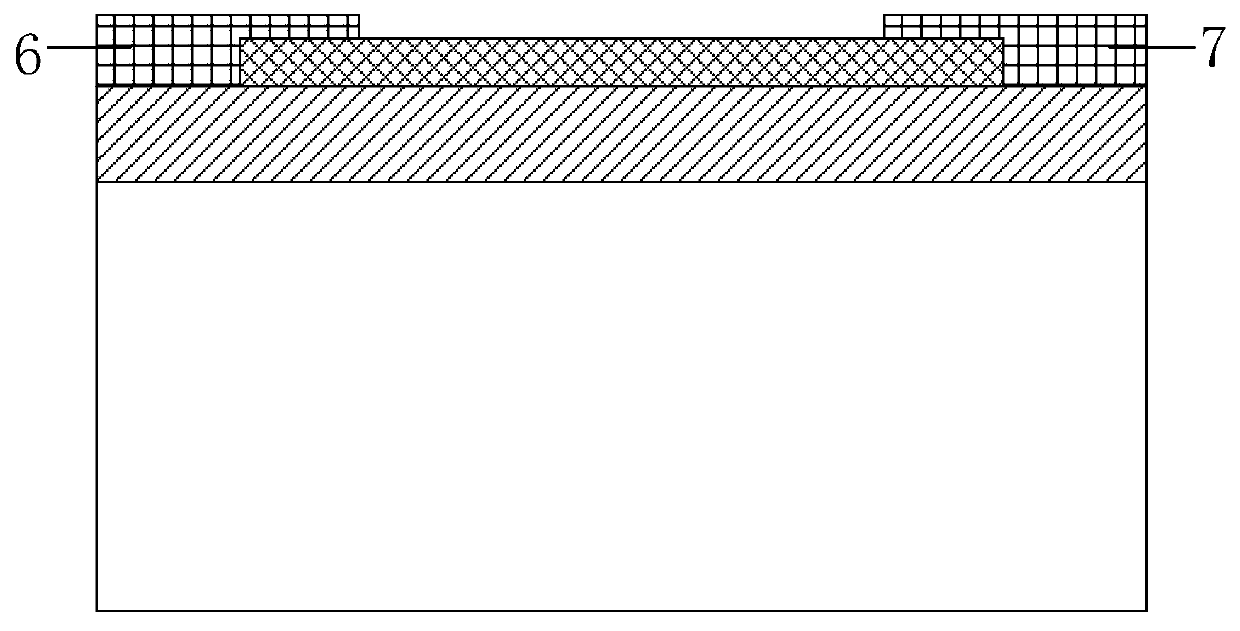

ActiveCN103311276AHigh selectivityAchieve coverageSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSelective deposition

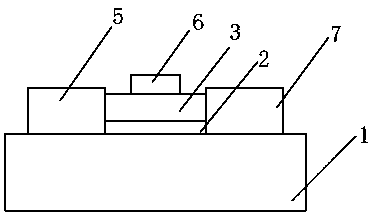

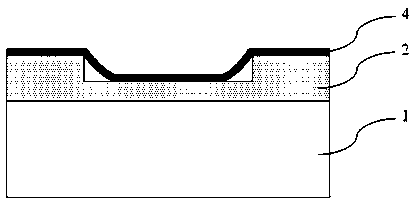

The invention discloses a self-aligned graphene field effect transistor and a manufacturing method thereof. The self-aligned graphene field effect transistor comprises a semiconductor substrate, an insulating layer, a conducting channel, a source electrode, a drain electrode, a gate dielectric layer, gate metal, self-aligned metal, the insulating layer is formed on the semiconductor substrate, the conducting channel is is formed on an insulator and formed by graphene, the source electrode and the drain electrode are formed on two sides of the conducting channel respectively, the gate dielectric layer selectively deposits on the conducting channel between the source electrode and the drain electrode, the gate metal is formed on the gate dielectric layer, and the gate dielectric layer and the gate metal are simultaneously and graphically piled together to form a gate accumulation layer to control carrier concentration of a channel area. A self-aligned metal layer covers on the source electrode, the drain electrode, the conducting channel and the gate metal, so that the area of a region not being covered by a grid and self-aligning of a device grid and the source electrode as well as the drain electrode is realized.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

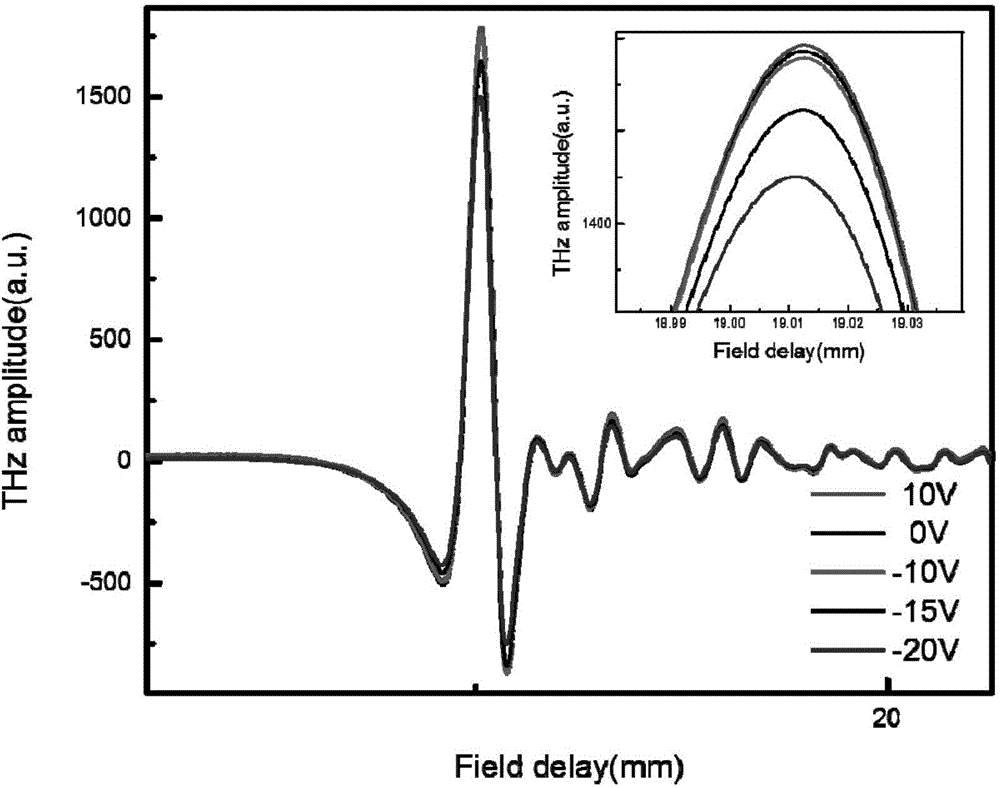

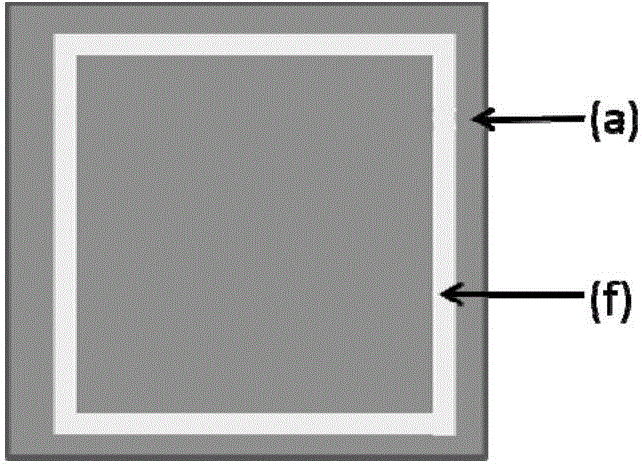

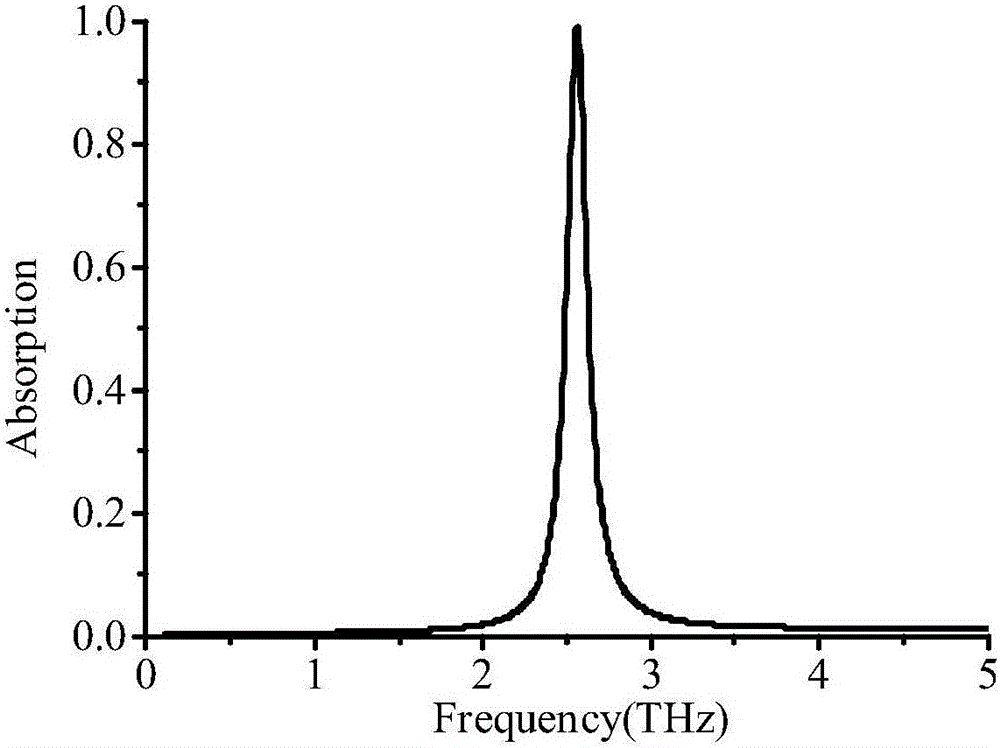

Graphene field effect transistor terahertz wave modulator and manufacture method thereof

InactiveCN104678597AReduce thicknessReduce leakage currentNon-linear opticsCommunications systemGrating

The invention provides a graphene field effect transistor terahertz wave modulator and a manufacture method thereof and aims to increase the modulating speed and depth of the graphene field effect transistor terahertz wave modulator. The graphene field effect transistor terahertz wave modulator comprises a semiconductor substrate, and a medium layer, a graphene film and source and drain electrodes which are arranged on the substrate, and an annular grating electrode which is arranged on the back of the substrate. The terahertz wave modulator is characterized in that the medium layer is an Al2O3 layer, and the thickness ranges from 5 to 100nm; the Al2O3 is deposited by the ALD (atomic layer deposition) method, and the Al2O3 is high in evenness, is free of defects and pores and has better voltage resistance; the leakage current is reduced greatly. The modulating speed of the terahertz wave modulator can be 178 KHz, the corresponded modulating depth is larger than 22%, and the modulating speed and depth are increased significantly; the terahertz wave modulator can be widely applied to the fields of terahertz wave communication systems, terahertz wave detection and terahertz wave imaging.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Graphene field effect transistor

The invention discloses a graphene field effect transistor, and belongs to the technical field of electronics and graphene. A basic structure of the graphene field effect transistor comprises a grid, a source, a drain, an insulation layer and an active layer, wherein the active layer is formed by compositing single-layer or multi-layer graphene with the insulator or semiconductor characteristic after passivation and other semiconductor materials. The graphene field effect transistor successfully overcomes the fatal defects of the existing graphene field effect tube, has the higher performance compared with the conventional semiconductor field effect tube, and can promote an application of the graphene in the technical field of the electronics.

Owner:李德杰

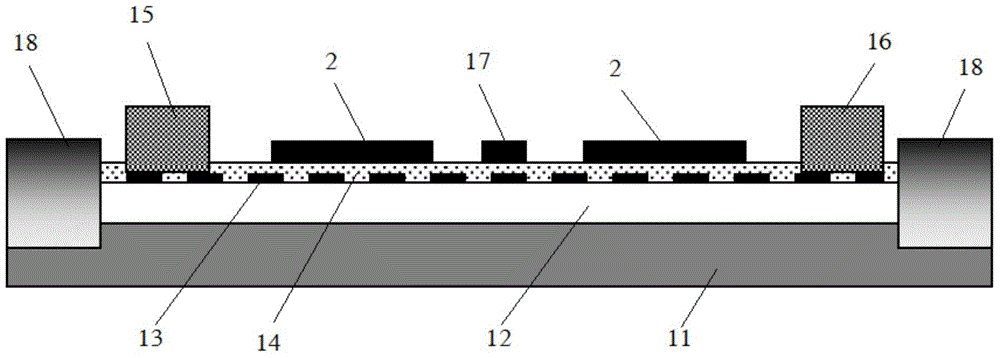

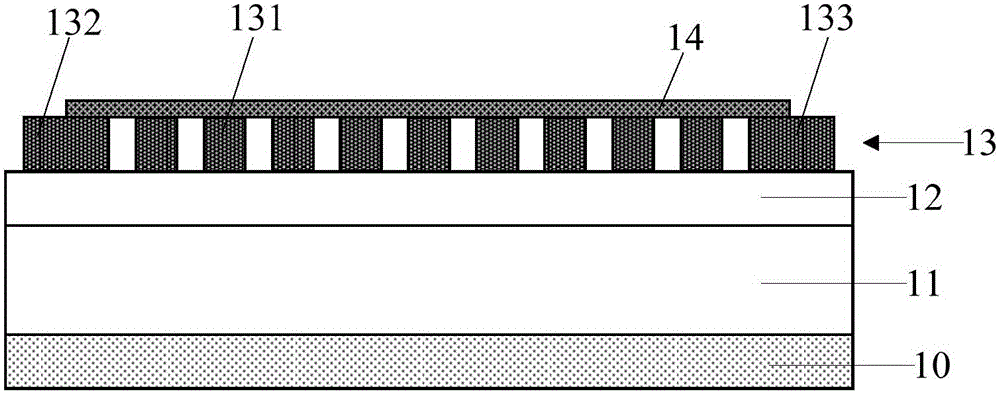

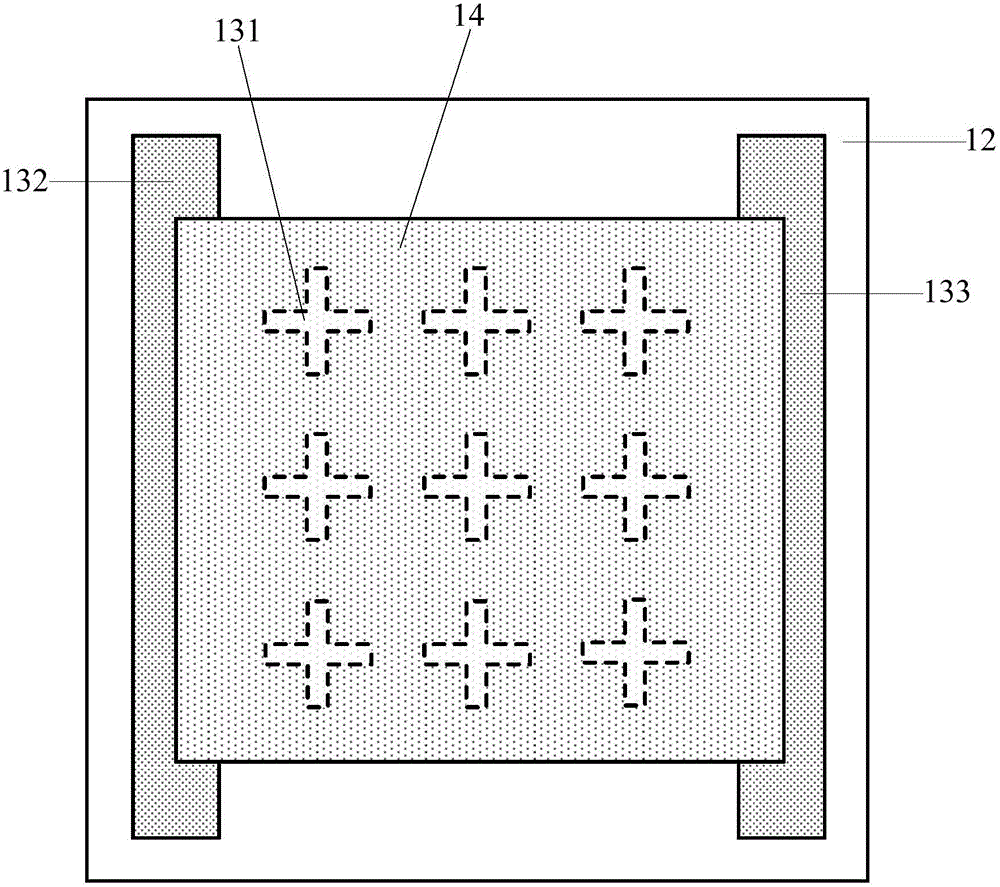

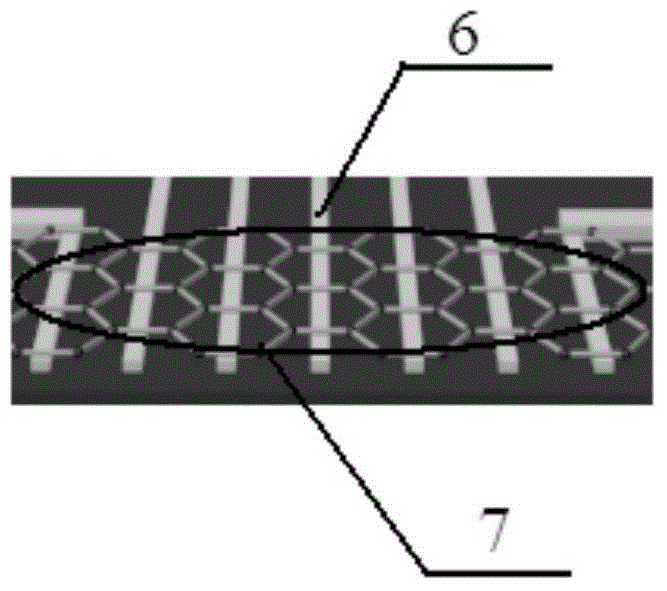

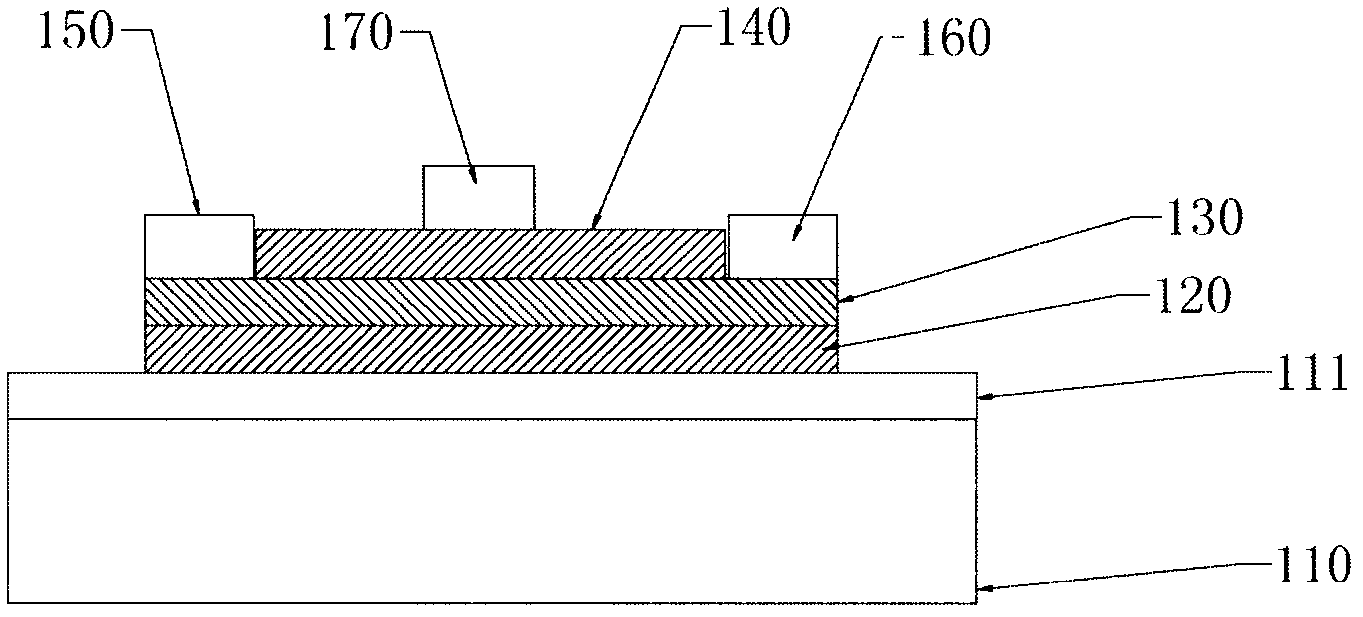

Graphene field effect transistor based terahertz detector and preparation method therefor

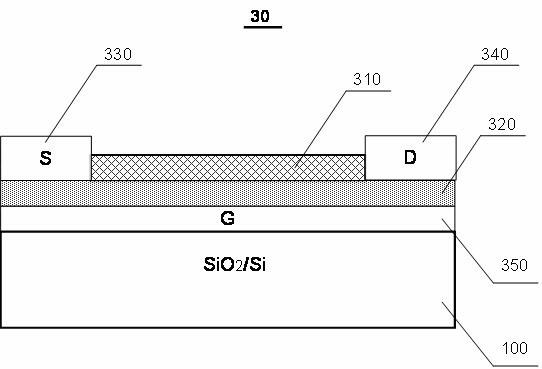

ActiveCN106129135AQuick responseFinal product manufactureSemiconductor devicesGrapheneMetal electrodes

The invention provides a graphene field effect transistor based terahertz detector and a preparation method therefor. The detector comprises a gate electrode, a substrate layer, an insulating layer, a metal electrode layer and a graphene channel layer from the bottom up, wherein the metal electrode layer comprises a metal electrode array, and a source electrode and a drain electrode which are positioned on the two sides of a metal pattern array; the metal electrode array comprises multiple metal electrodes which are periodically arranged at intervals; the metal electrodes, the source electrode and the drain electrode are the same in thickness; the graphene channel layer is formed on the metal electrode layer; and the graphene channel layer fully covers the metal electrode array and at least partially covers the source electrode and the drain electrode. By adoption of the way, the absorptivity of the detector on terahertz radiation can be improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

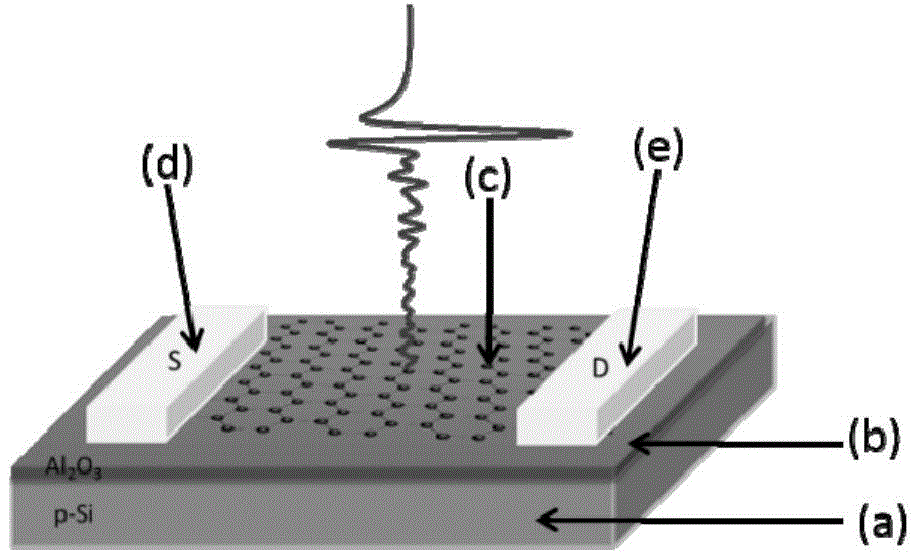

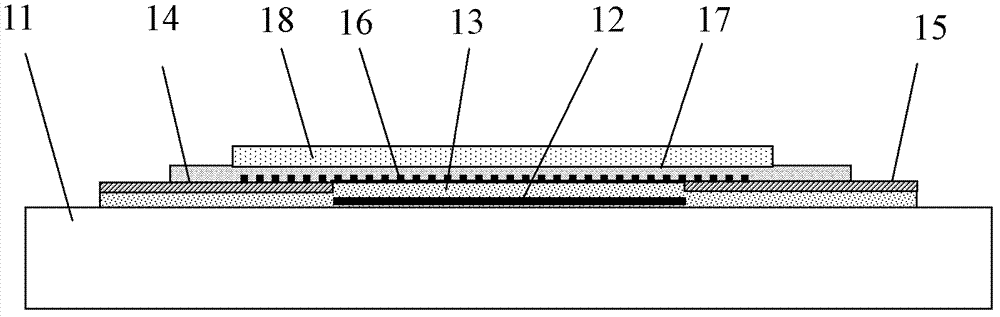

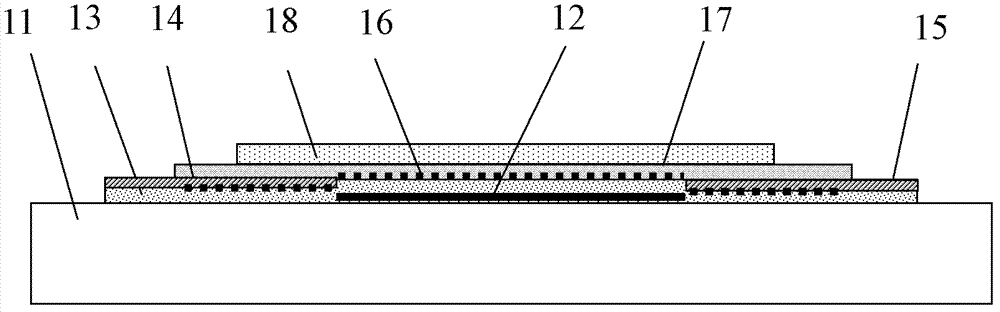

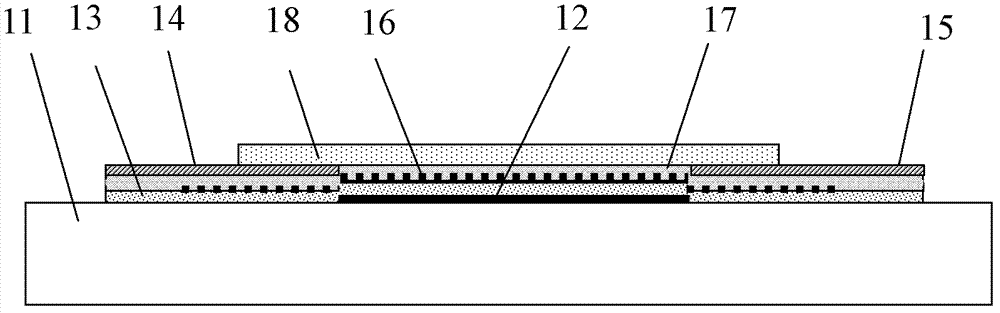

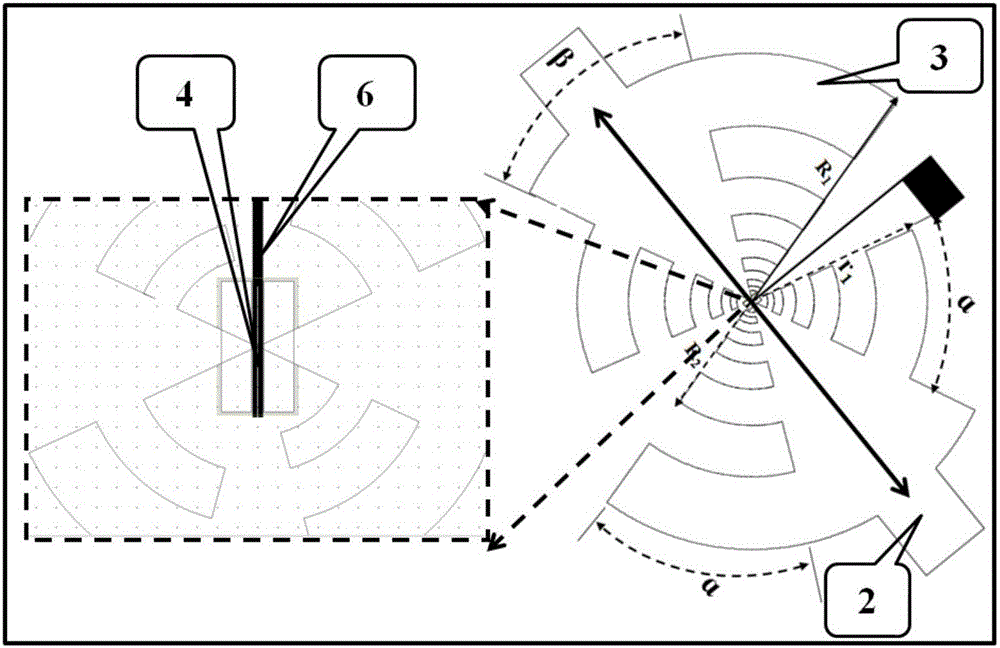

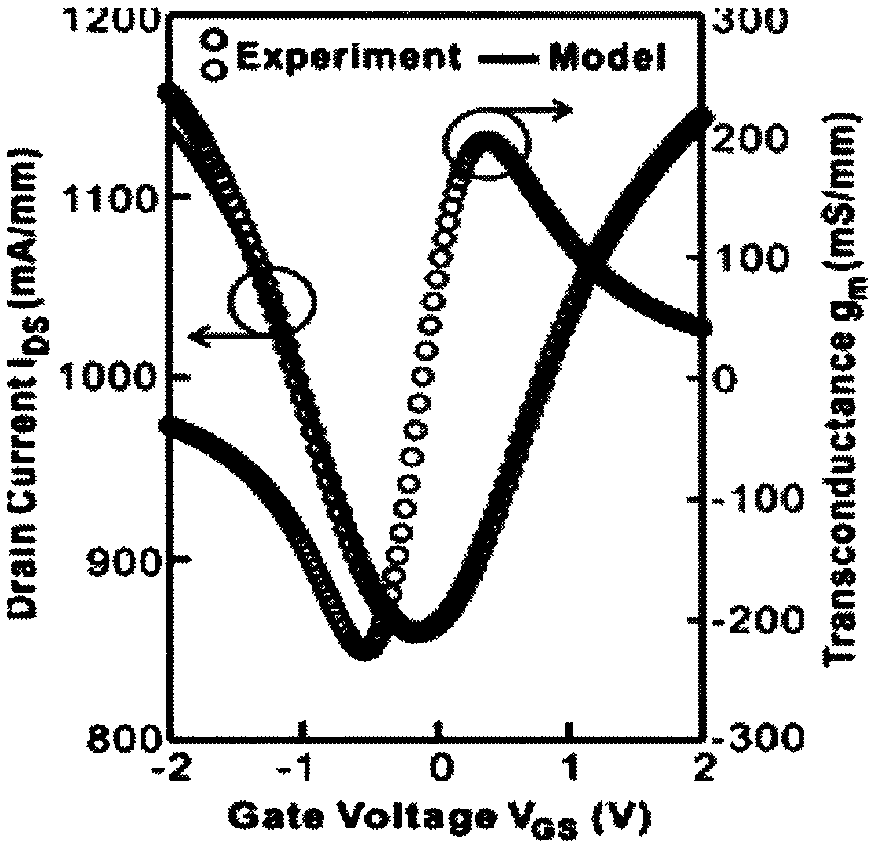

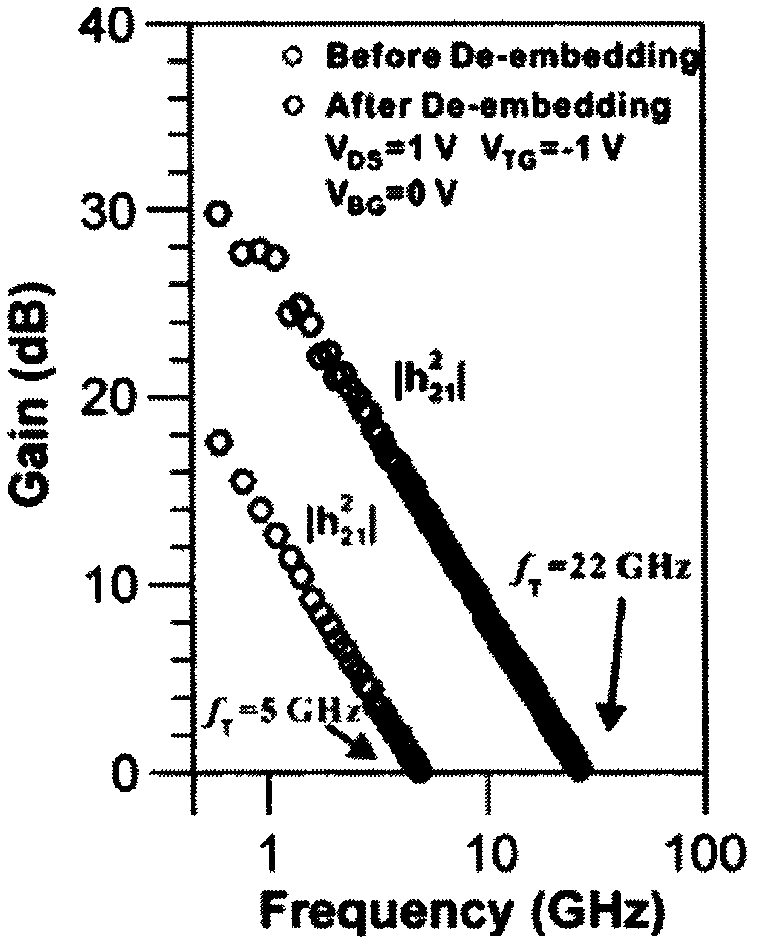

Room-temperature adjustable sub-Terahertz wave detector and preparation method

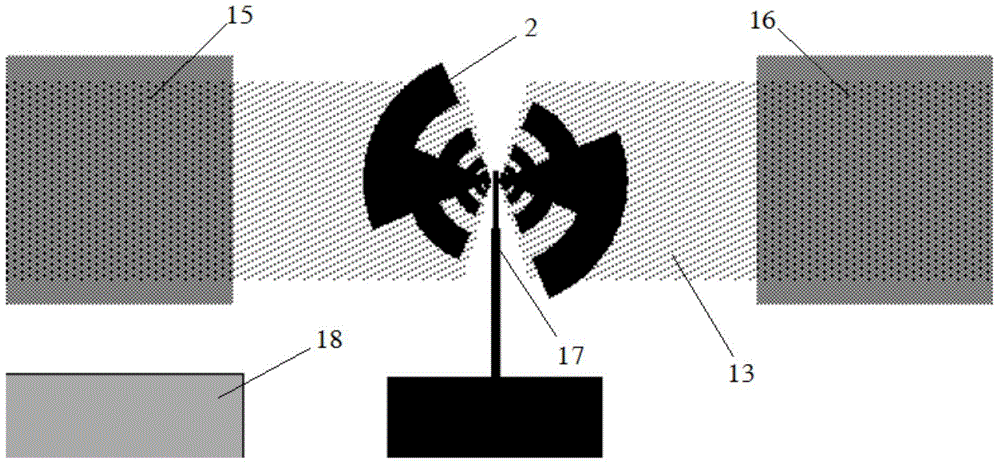

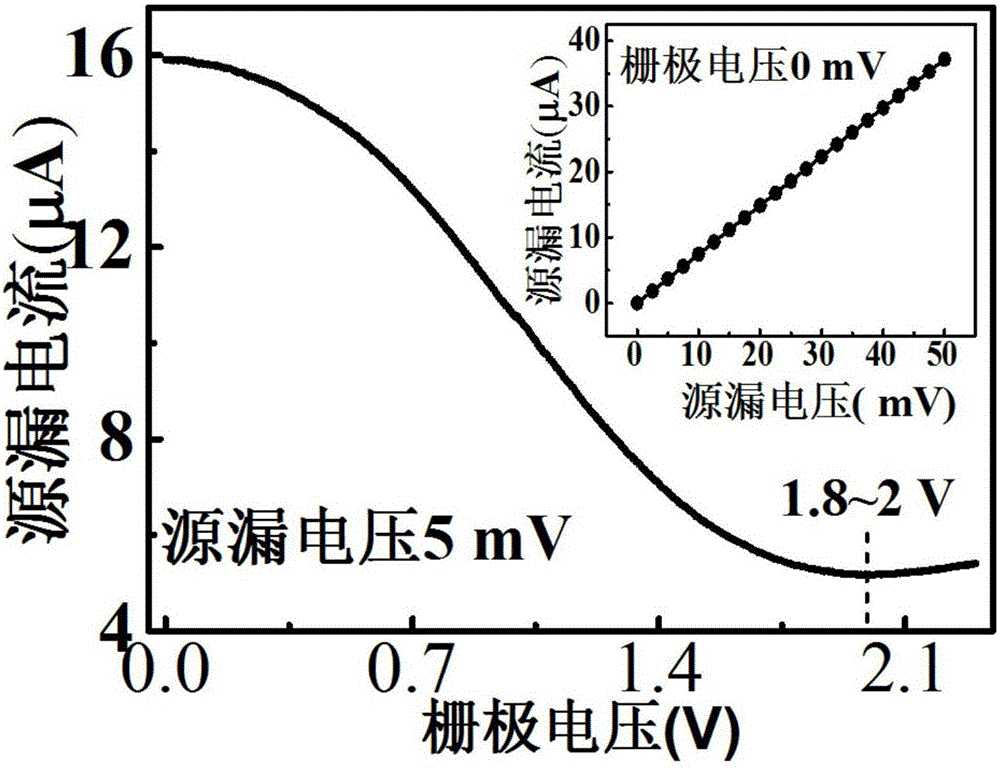

ActiveCN106374006AHigh speed detectionAdjustable detectionFinal product manufacturePhotovoltaic energy generationGate dielectricWave detection

The invention discloses a room-temperature adjustable sub-Terahertz wave detector and a preparation method. A graphene field effect transistor with high migration rate and adjustable carrier concentration is taken as a basic structure unit, and the field effect transistor is provided with a group of source and drain electrodes and cleavage grid electrodes of a sub-Terahertz wave coupled antenna. The detector is integrated with log-periodic antennas and corresponding feed electrodes on a sapphire substrate; the detector is provided with a graphene conducting channel transferred in an antenna distance; an aluminum oxide gate dielectric layer is arranged on the graphene conducting channel, and finally the cleavage grid electrodes and the corresponding lead electrodes are integrated on the aluminum oxide gate dielectric layer of the graphene conducting channel, so that adjustable sub-Terahertz wave detection is realized. The detector has the advantages that the detector is an adjustable lightguide-like and photovoltaic-like detector with high speed, wide band and high response; and the integration level, technical maturity and repeatability of the device lay the foundation of large-scale application of Terahertz detectors.

Owner:安徽荣程电子科技有限公司

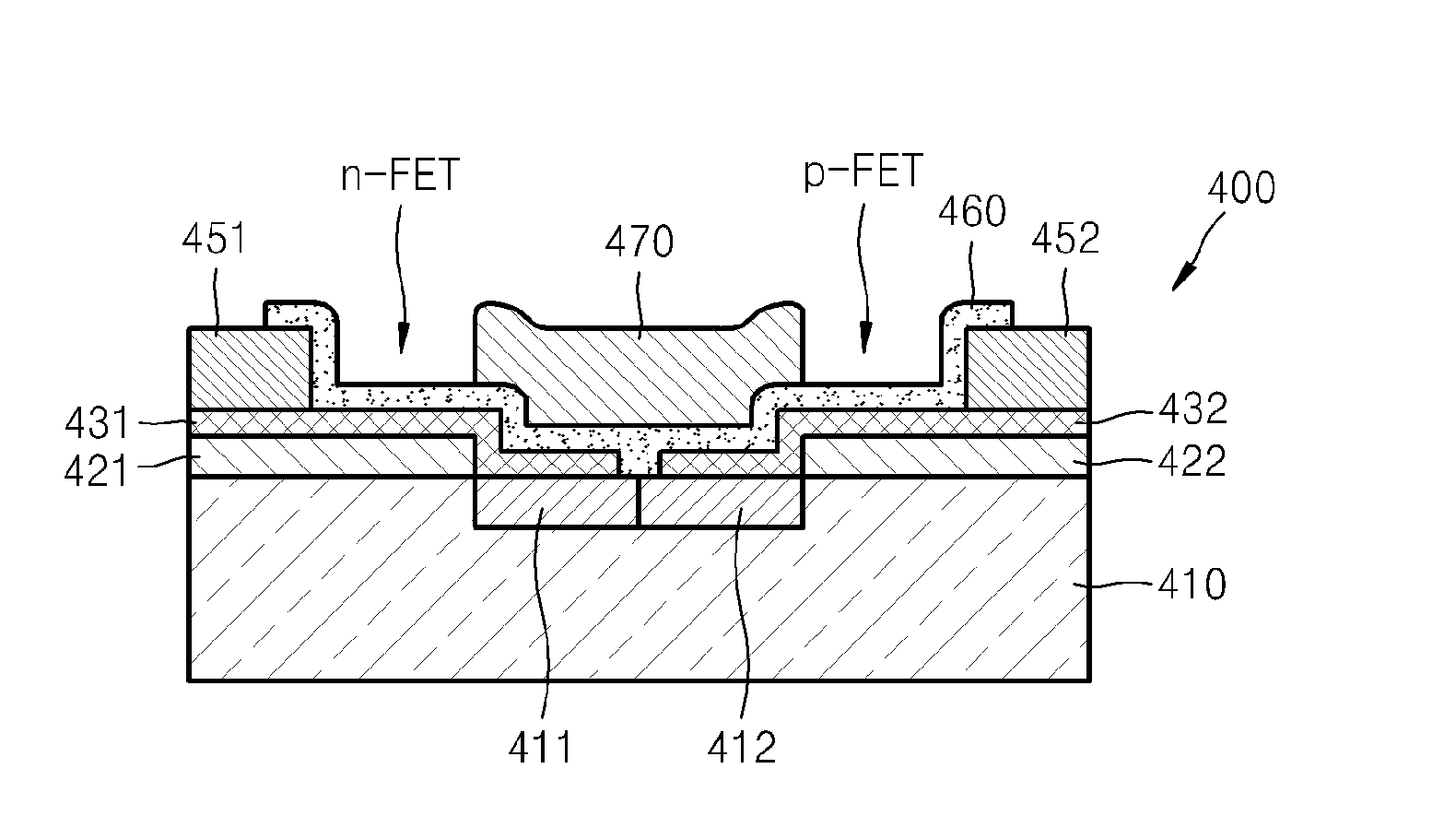

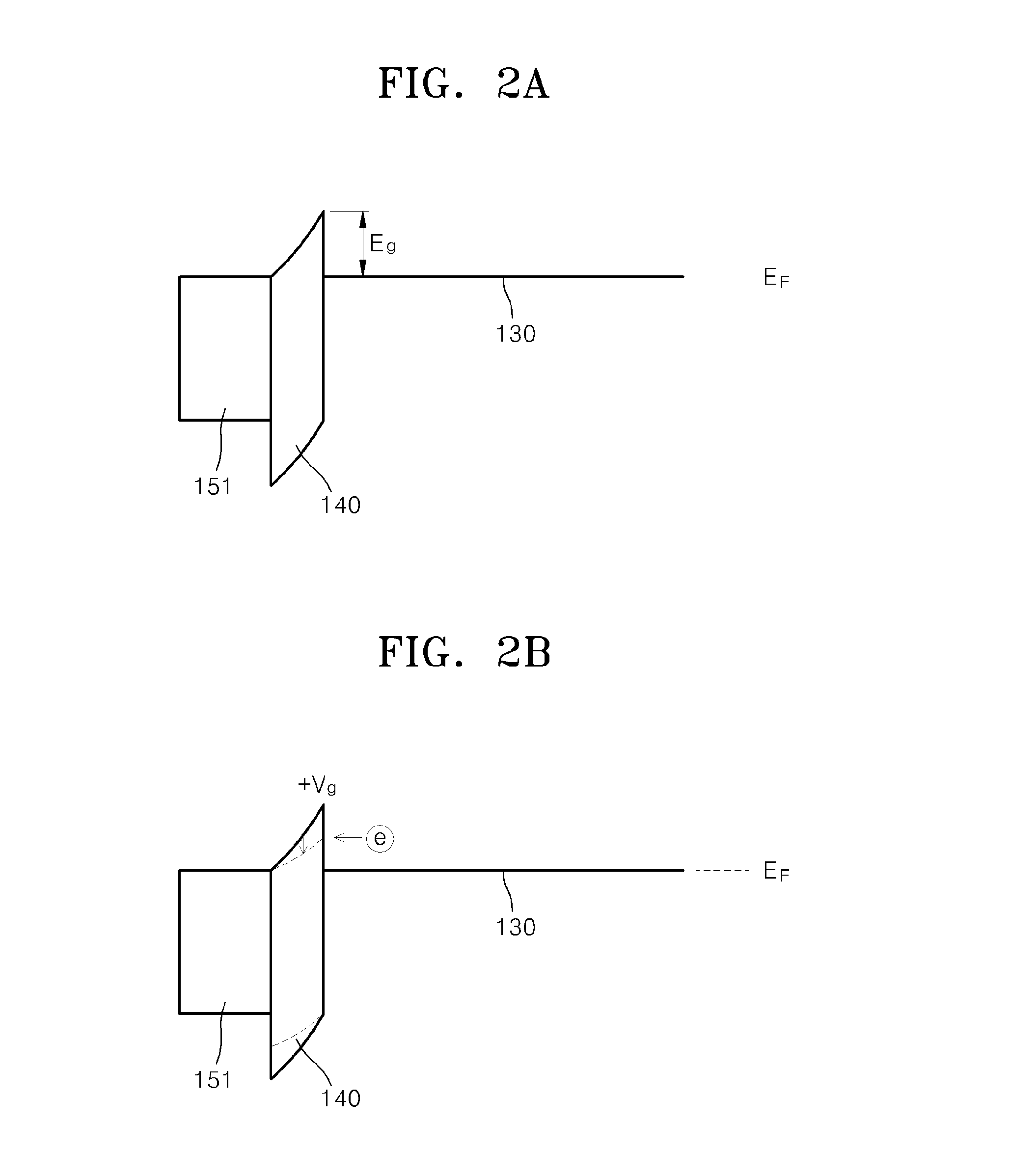

Inverter logic devices including graphene field effect transistor having tunable barrier

Inverter logic devices include a gate oxide on a back substrate, a first graphene layer and a second graphene layer separated from each other on the gate oxide, a first electrode layer and a first semiconductor layer separated from each other on the first graphene layer, a second electrode layer and a second semiconductor layer separated from each other on the second graphene layer, and an output electrode on the first and second semiconductor layers and configured to output an output signal. The first semiconductor layer is doped with a different type of impurities selected from n-type impurities and p-type impurities than the second semiconductor layer.

Owner:SAMSUNG ELECTRONICS CO LTD

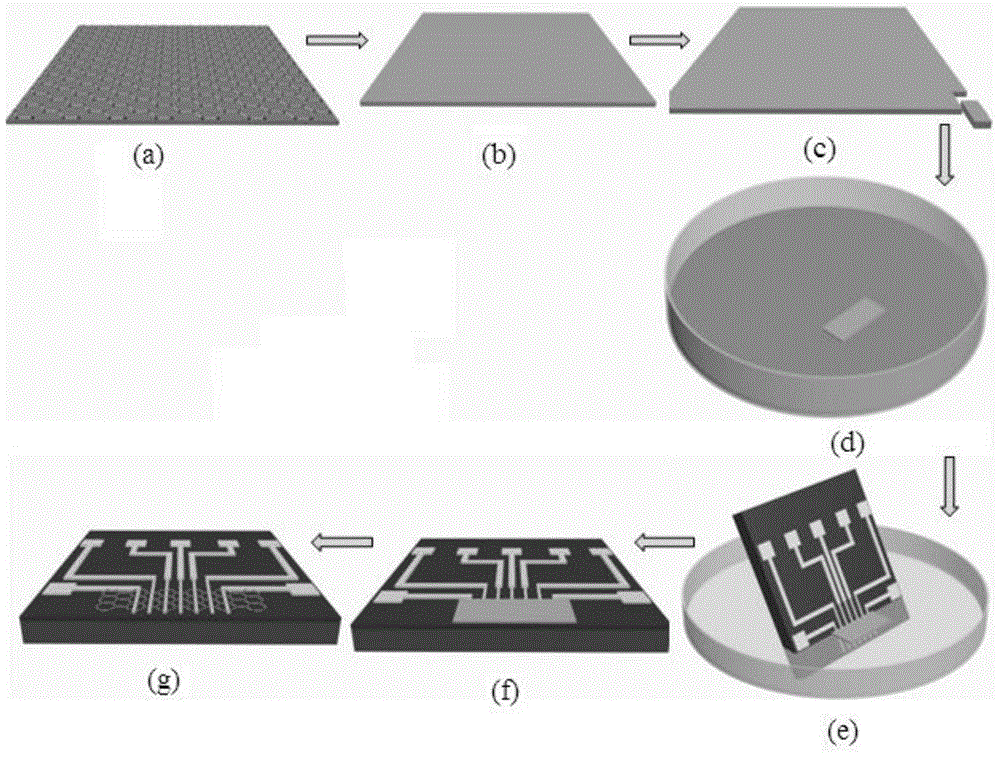

Preparation method of graphene field-effect transistor biosensor

ActiveCN104535635AKeep Superior PerformanceImprove cleanlinessMaterial analysis by electric/magnetic meansPolymethyl methacrylateSingle layer graphene

The invention belongs to a preparation method of a biosensor, and relates to a preparation method of a graphene field-effect transistor biosensor. The preparation method comprises the following steps: (1) preparing a single-layer graphene copper plate; (2) preparing devices on a substrate layer of a sensor; (3) performing directional transfer on graphene; and (4) heating to bake the sensor, removing PMMA (polymethyl methacrylate) with acetone, performing vacuum annealing, and modifying the graphene with probes to obtain the graphene field-effect transistor biosensor. According to the preparation method provided by the invention, large-scale preparation of the biosensor based on CVD (chemical vapor deposition) graphene can be realized, the copper etching time is short, and the preparation method is simple and quick and can greatly lower the manufacturing cost; and in the preparation process, the PMMA polymer is used only once (in the traditional method, the PMMA polymer is used for more times, at least three times), thus greatly improving the surface cleanliness of the graphene, retaining the intrinsic high performance of the graphene and being more beneficial to subsequent probe modification.

Owner:HUBEI UNIV OF CHINESE MEDICINE

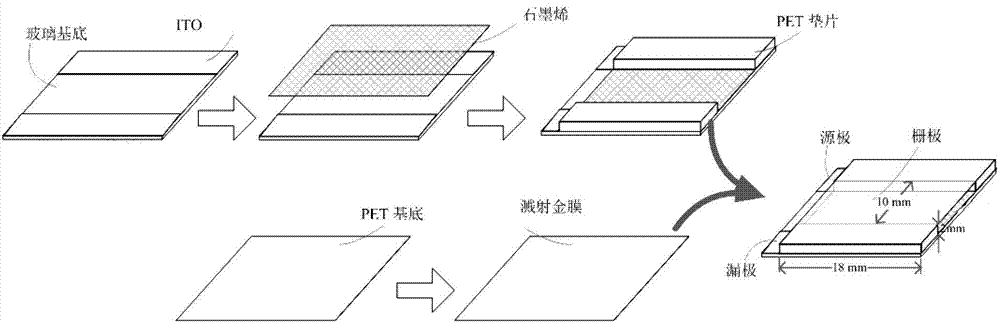

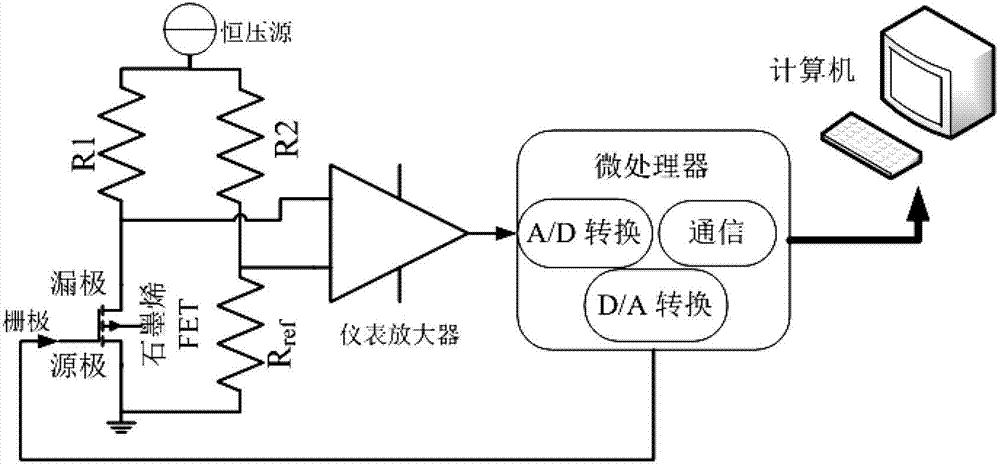

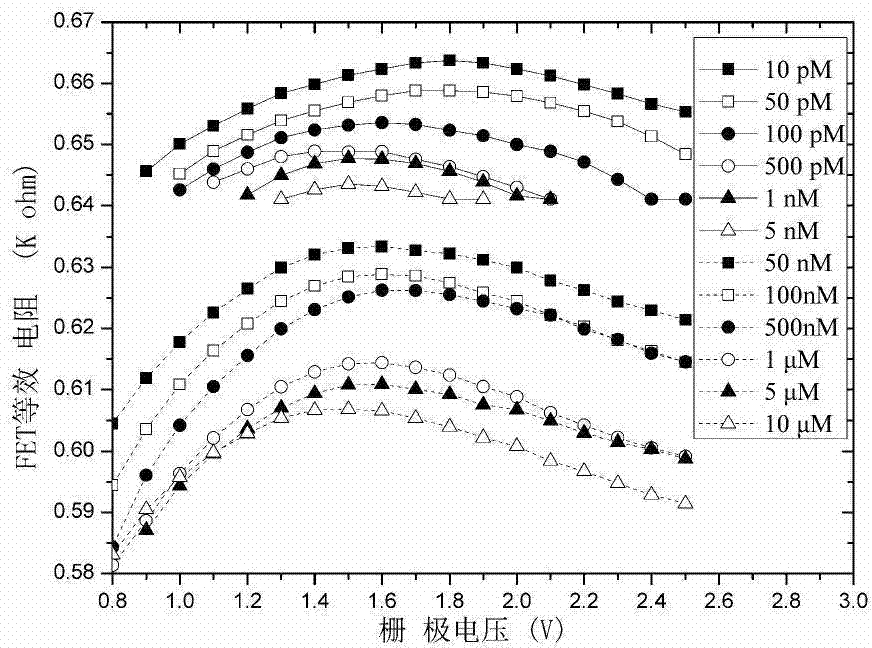

Graphene field-effect transistor biosensor as well as manufacturing method and detecting method thereof

InactiveCN103399071AIncrease the area of actionReduce contact resistanceMaterial analysis by electric/magnetic meansSemiconductor devicesPolyethylene glycolGold film

The invention discloses a graphene field-effect transistor biosensor as well as a manufacturing method and a detecting method thereof. The graphene field-effect transistor biosensor comprises glass substrates, wherein the two sides of each glass substrate are respectively provided with an ITO (indium tin oxide); parts of glass substrates at the same side as well as the ITOs of the parts of glass substrates are covered with graphene; the ITOs at the two sides of each glass substrate without graphene are respectively a source electrode and a drain electrode; a PET (polyethylene glycol terephthalate) gasket is covered on each ITO covered with the graphene and is covered with a PET substrate on which a gold film is sputtered; a sample cell is arranged in the middle of each glass substrate by insulating silica gel; the gold film is taken as a grid electrode. The contact resistance is reduced by means of covering the ITOs with graphene, the plane gold film electrode is taken as the grid electrode to exert a uniform electric field and increase the action area of electrolyte and graphene, and by the two aspects, the detection sensitivity is improved and the detection range is enlarged; by detection, the lower limit of adenosine triphosphate reaches 10pM.

Owner:SHANDONG NORMAL UNIV

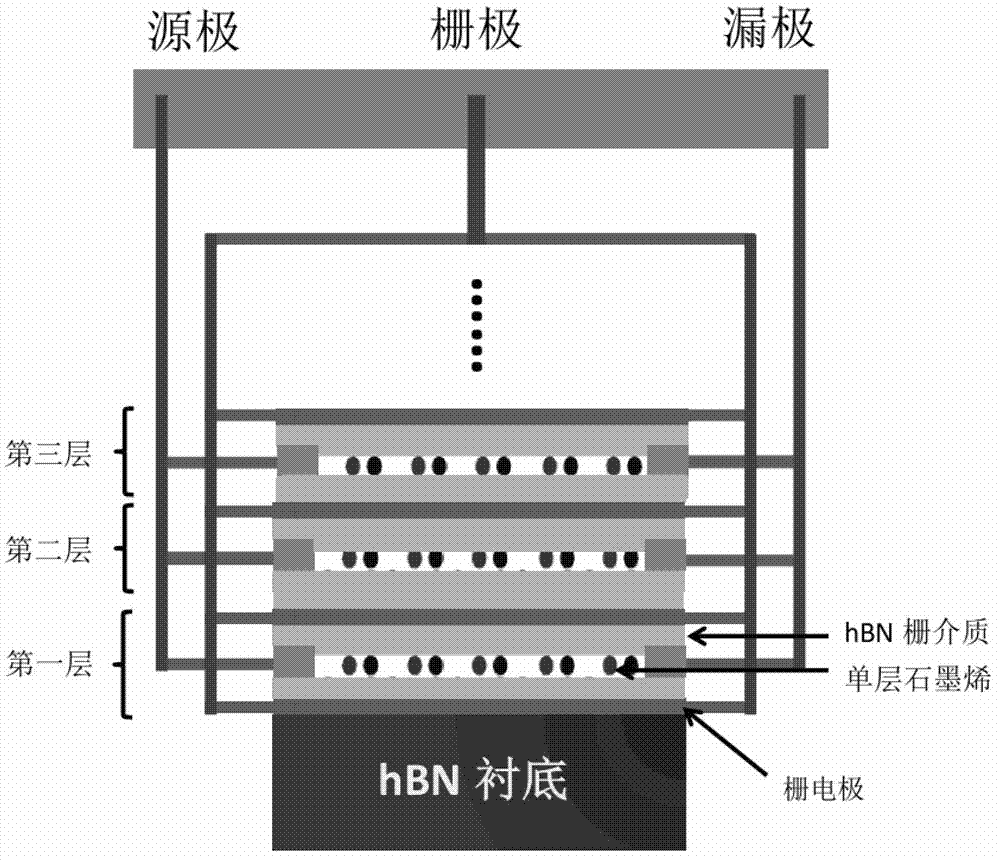

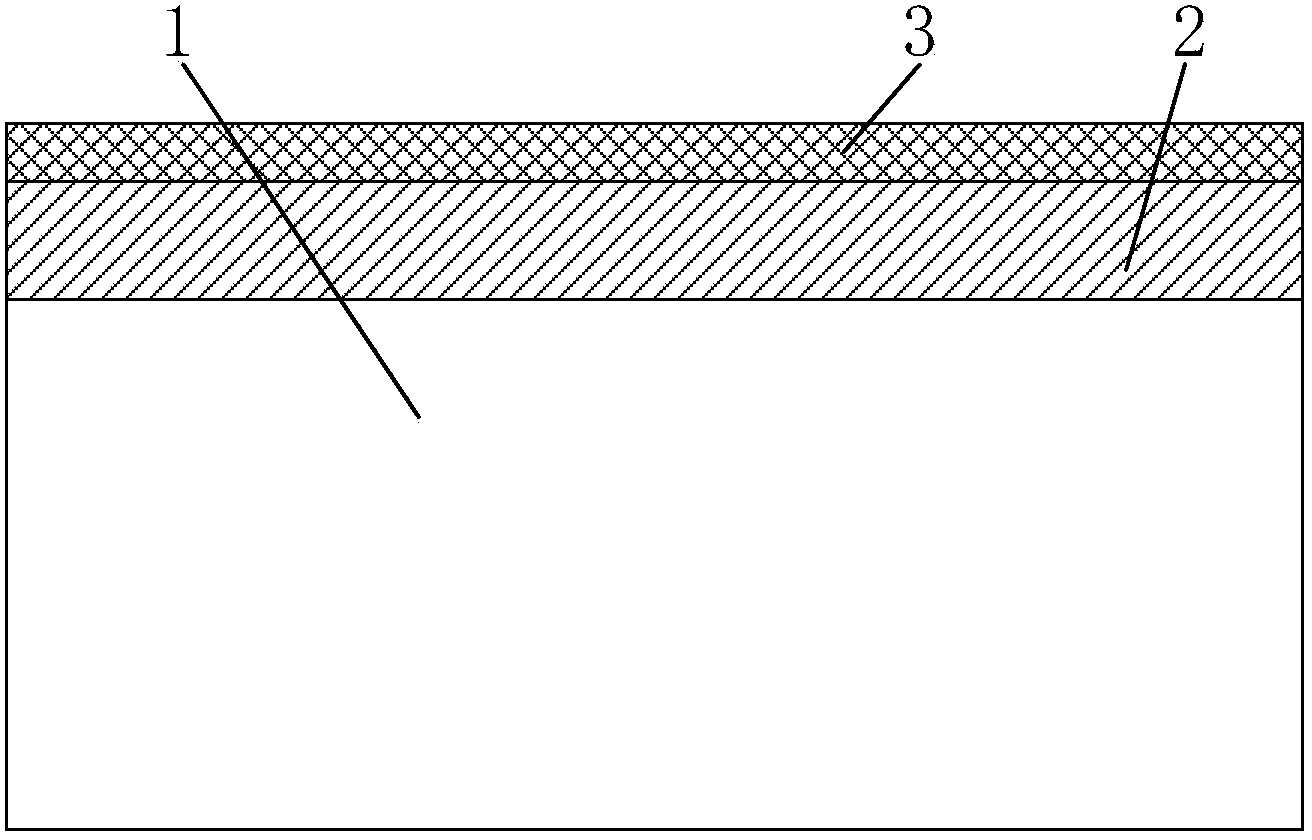

Multilayer dual-gate graphene field effect transistor and preparation method for same

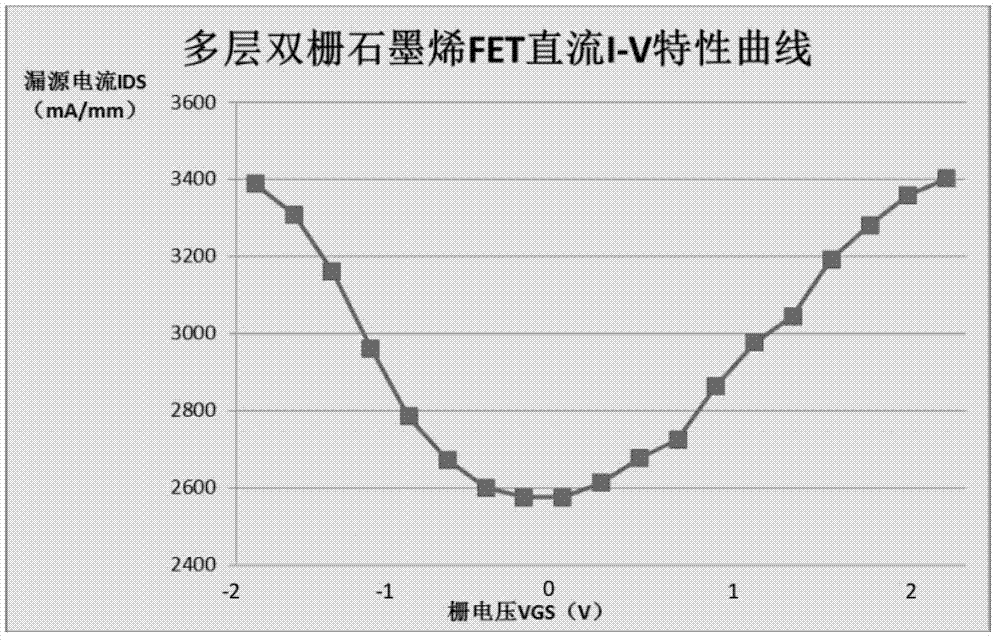

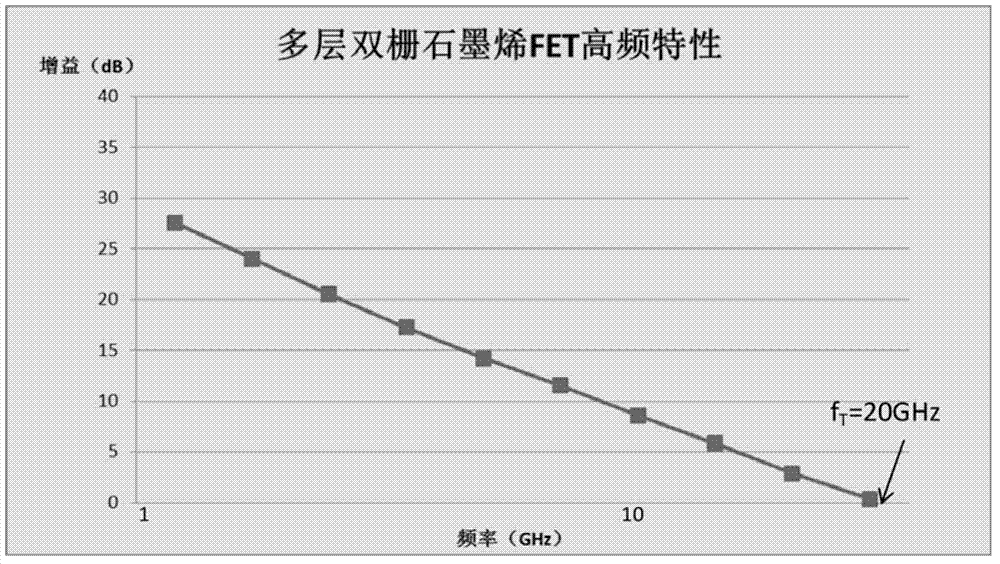

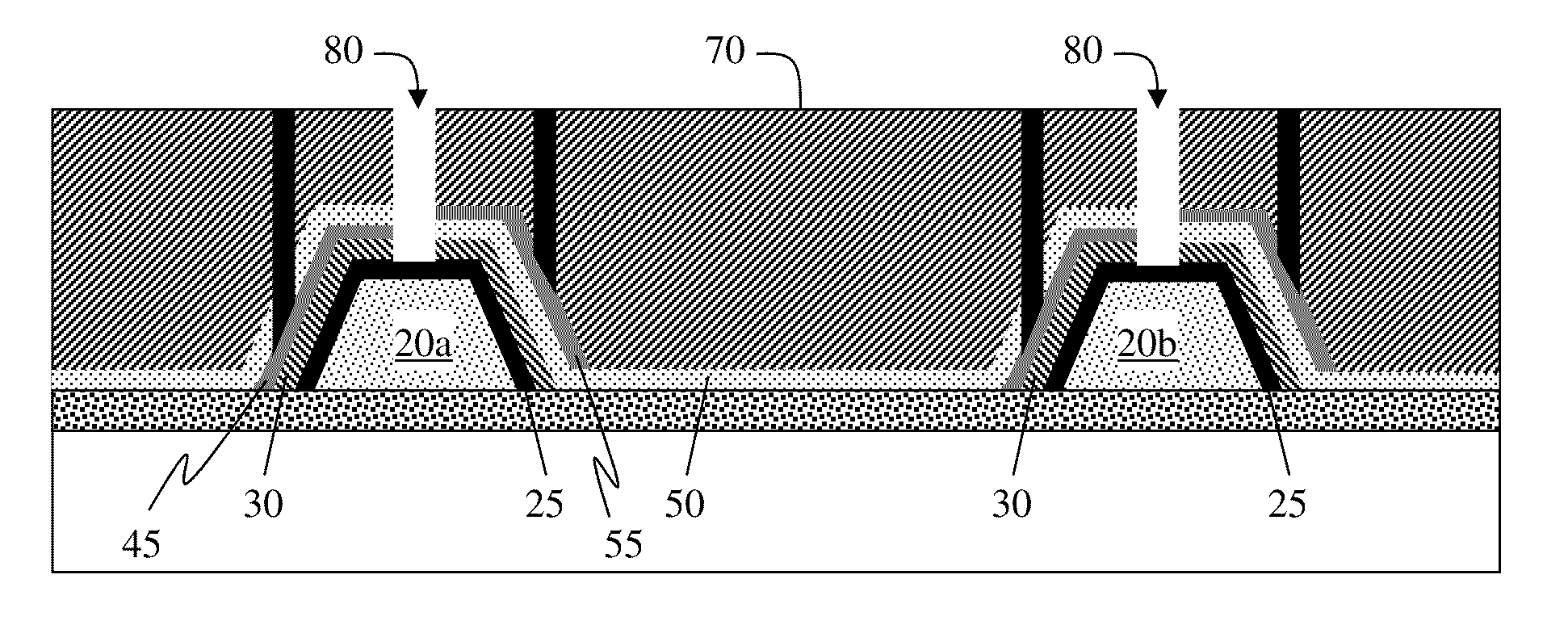

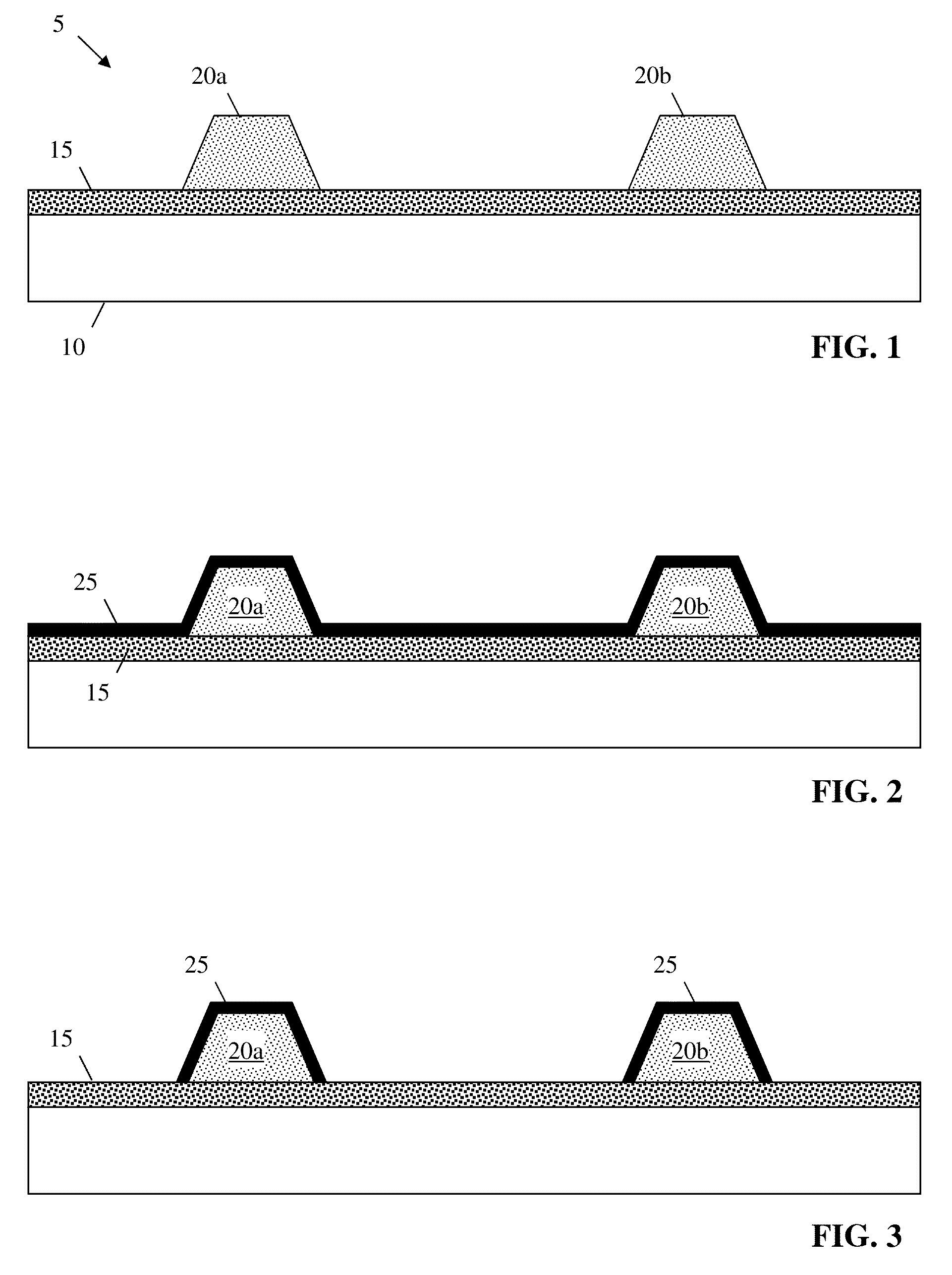

InactiveCN103208524AImprove mobilityRaise the cutoff frequencySemiconductor/solid-state device manufacturingSemiconductor devicesHexagonal boron nitrideBottom gate

The invention discloses a multilayer dual-gate graphene field effect transistor. The multilayer dual-gate graphene field effect transistor comprises a hexagonal boron nitride substrate, a source electrode, a drain electrode, a bottom gate metal electrode deposited on the substrate, a back gate medium, single-layer graphene, a top gate medium and a top gate metal electrode, wherein the bottom gate metal electrode is connected with the top gate metal electrode. In case of a plurality of layers of transistors, the transistors are connected in parallel, and the drain and source electrodes of the transistors are connected in parallel respectively. The multilayer dual-gate graphene field effect transistor has the advantage that hexagonal boron nitride is used as the top gate medium and the bottom gate medium, is a two-dimensional planar material, and has a few surface dangling bonds and trapped charges, so that the migration rate of carriers of a graphene channel can be increased. According to the multilayer dual-gate graphene field effect transistor, the drain and source current of the graphene field effect transistor can be maximally improved, and the graphene field effect transistor is widely applied to the field of high-frequency high-power devices.

Owner:XIDIAN UNIV

Graphene field effect transistor

Manufacturing a semiconductor structure including: forming a seed material on a sidewall of a mandrel; forming a graphene field effect transistor (FET) on the seed material; and removing the seed material.

Owner:IBM CORP

Grapheme field effect transistor and preparation method thereof

InactiveCN103258849AImprove performanceImprove featuresSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPhonon

The invention provides a grapheme field effect transistor and a preparation method of the grapheme field effect transistor. According to the grapheme field effect transistor, h-BN is used as gate media and used for replacing oxides such as SiO2 and HfO2 in an existing grapheme field effect transistor, and therefore performance of the grapheme field effect transistor is improved. Due to the fact that energy of a surface optic phonon mode of the h-BN is two times larger than that of a similar mode of SiO2, characteristics of the grapheme field effect transistor with the h-BN as the gate media under high frequency and a strong electric field are better than characteristics of a typical grapheme field effect transistor with the SiO2 as the gate media.

Owner:XIDIAN UNIV

Ultralow ohmic contact resistance graphene transistor and preparation method thereof

ActiveCN103985762AReduce contact resistanceIncrease the maximum oscillation frequencyTransistorSemiconductor/solid-state device manufacturingOhmic contactGraphene

The invention discloses an ultralow ohmic contact resistance graphene transistor comprising a substrate, and a source and a drain which are located on the substrate. A channel region is formed between the source and the drain. The channel region comprises a graphene layer, a dielectric layer and a gate from down to up successively. The preparation method of the ultralow ohmic contact resistance graphene transistor comprises the following steps: (1) the graphene layer is formed; (2) the dielectric layer is deposited; (3) on the dielectric layer, the channel region is covered with a photoresist pattern; (4) the exposed dielectric layer is corroded; (5) the exposed graphene layer is etched; (6) a source-drain ohmic contact metal is evaporated to form an ohmic contact metal layer; (7) the required source and drain regions are covered with the photoresist pattern; (8) the source and the drain are formed; (9) and the gate is formed. According to the method of the invention, the one-dimensional linear contact between the source-drain ohmic contact metal and the graphene can be realized so as to greatly reduce the contact resistance between the graphene and the metal, so that the maximum oscillation frequencycan be increased, and the applications of the graphene field effect transistor can be facilitated.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

Double-graphene-layer tunneling field effect transistor and manufacturing method thereof

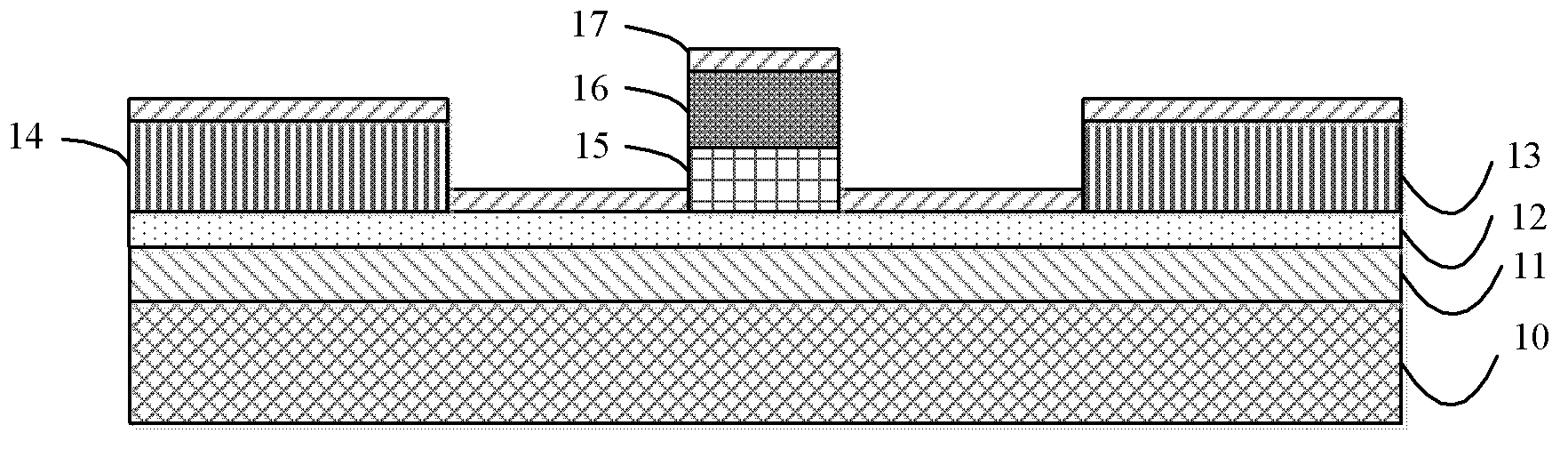

ActiveCN104241378AReduce off-state currentSimple preparation processSemiconductor/solid-state device manufacturingDiodeGate dielectricManufacturing technology

The invention provides a double-graphene-layer tunneling field effect transistor. A bottom gate dielectric layer is located on a bottom gate electrode. A double-graphene-layer active area is located on the bottom gate dielectric layer. A metal source electrode and a metal drain electrode are located at the two ends of the double-graphene-layer active area respectively and respectively cover a part of the double-graphene-layer active area. The metal source electrode and the metal drain electrode are made of different materials. For an n-type device, the work function of the metal source electrode is larger, the graphene in contact with the metal source electrode is in p-type doping, the work function of the metal drain electrode is small, and the graphene in contact with the metal drain electrode is in n-type doping. The electrodes of a p-type device are opposite to those of the n-type devices. The metal source electrode, the metal drain electrode and the graphene between the metal source electrode and the metal drain electrode are covered with a top gate dielectric layer. A top gate electrode is located on the top gate dielectric layer and overlaps the metal source electrode and the metal drain electrode. The manufacturing technology of the double-graphene-layer tunneling field effect transistor is simple. Compared with a traditional double-graphene-layer field effect transistor, the metal source electrode and the metal drain electrode of the double-graphene-layer tunneling field effect transistor are completed independently.

Owner:PEKING UNIV

Stepped gate-dielectric double-layer graphene field effect transistor and production method thereof

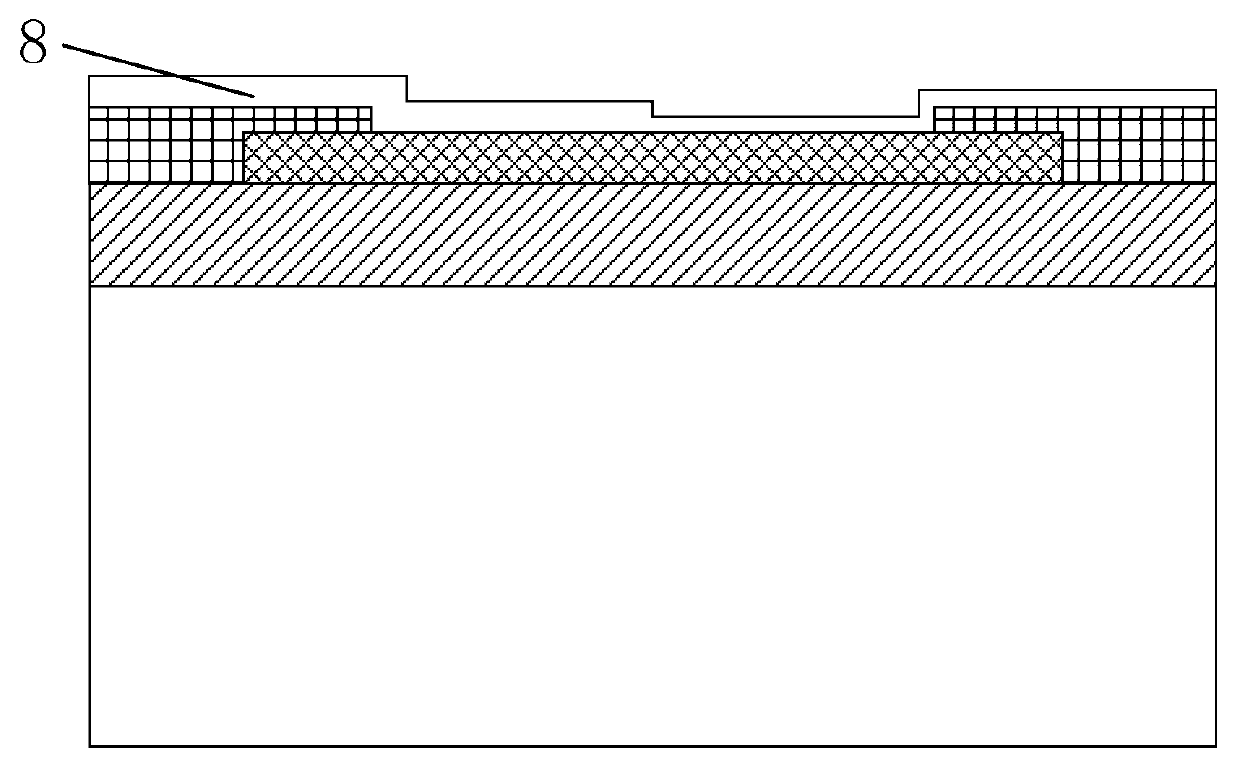

ActiveCN104218089AReduce the tunneling windowSuppresses off-state currentSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricBottom gate

A stepped gate-dielectric double-layer graphene field effect transistor comprises a bottom gate electrode, a bottom gate dielectric layer, a double-layer graphene active region, a metal source electrode, a metal drain electrode, a stepped top gate dielectric layer and a top gate electrode. The bottom gate dielectric layer is located on the bottom gate electrode, the double-layer graphene active region is located on the bottom gate dielectric layer, the metal source electrode and the metal drain electrode are located at two ends of the double-layer graphene active region respectively and cover the bottom gate dielectric layer and part of the double-layer graphene active region at the same time, the stepped top gate dielectric layer covers the metal source electrode, the metal drain electrode and graphene between the two electrodes, the top gate electrode only covers the top of the stepped top gate dielectric layer partially, and the distance between the top gate electrode and the edge of the metal source electrode is equal to that between the top gate electrode and the edge of the metal drain electrode. By introduction of the stepped top gate dielectric layer, a tunneling window between a source region and a gate-controlled trench under an off state is reduced effectively, so that small off-state current is obtained, and on-off ratio of a device is increased.

Owner:PEKING UNIV

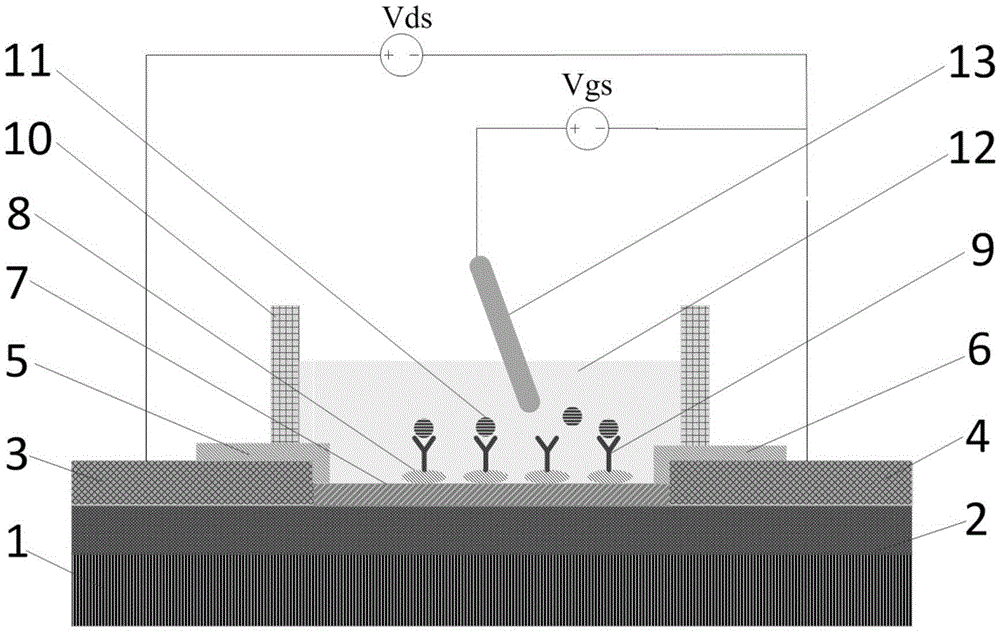

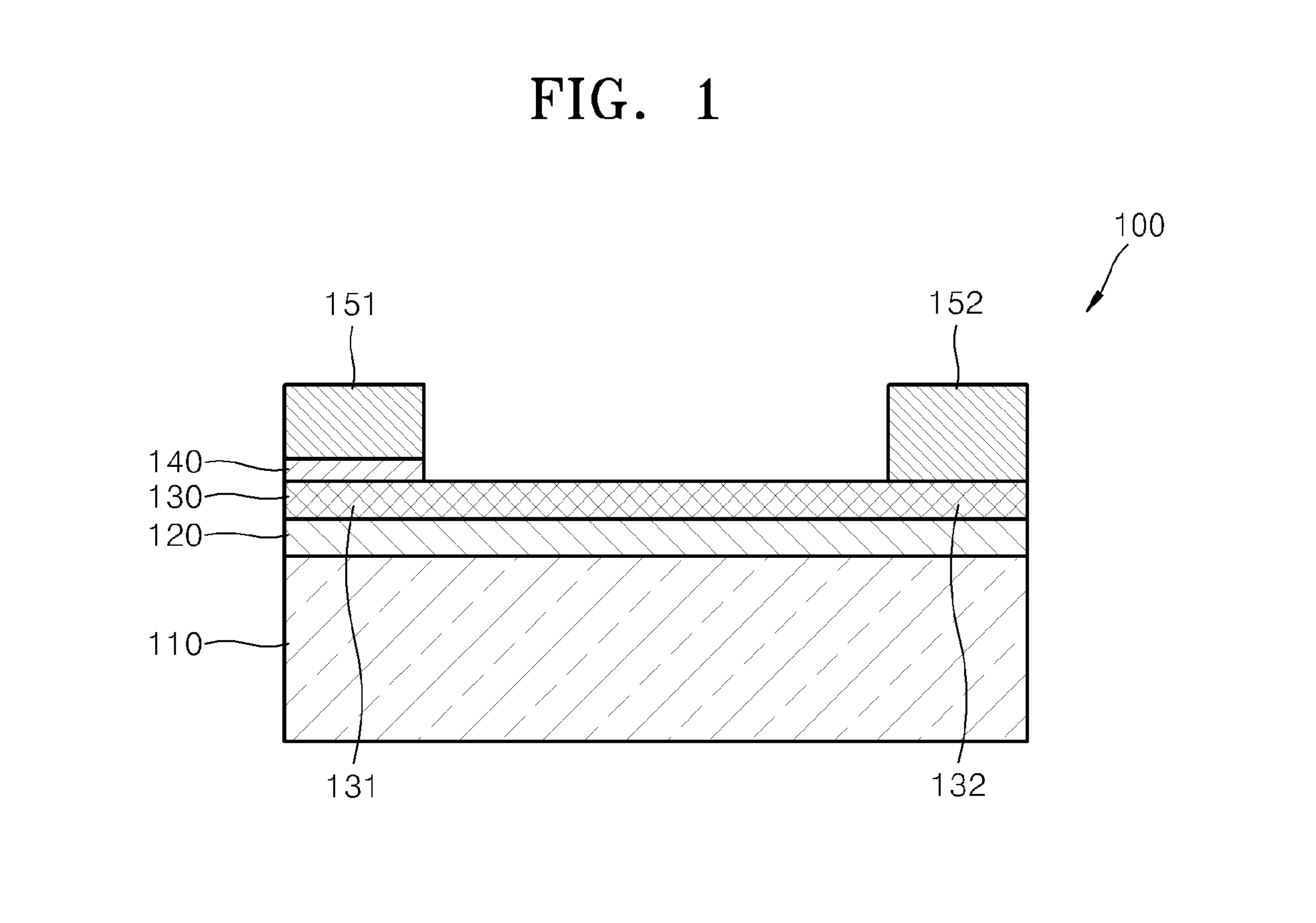

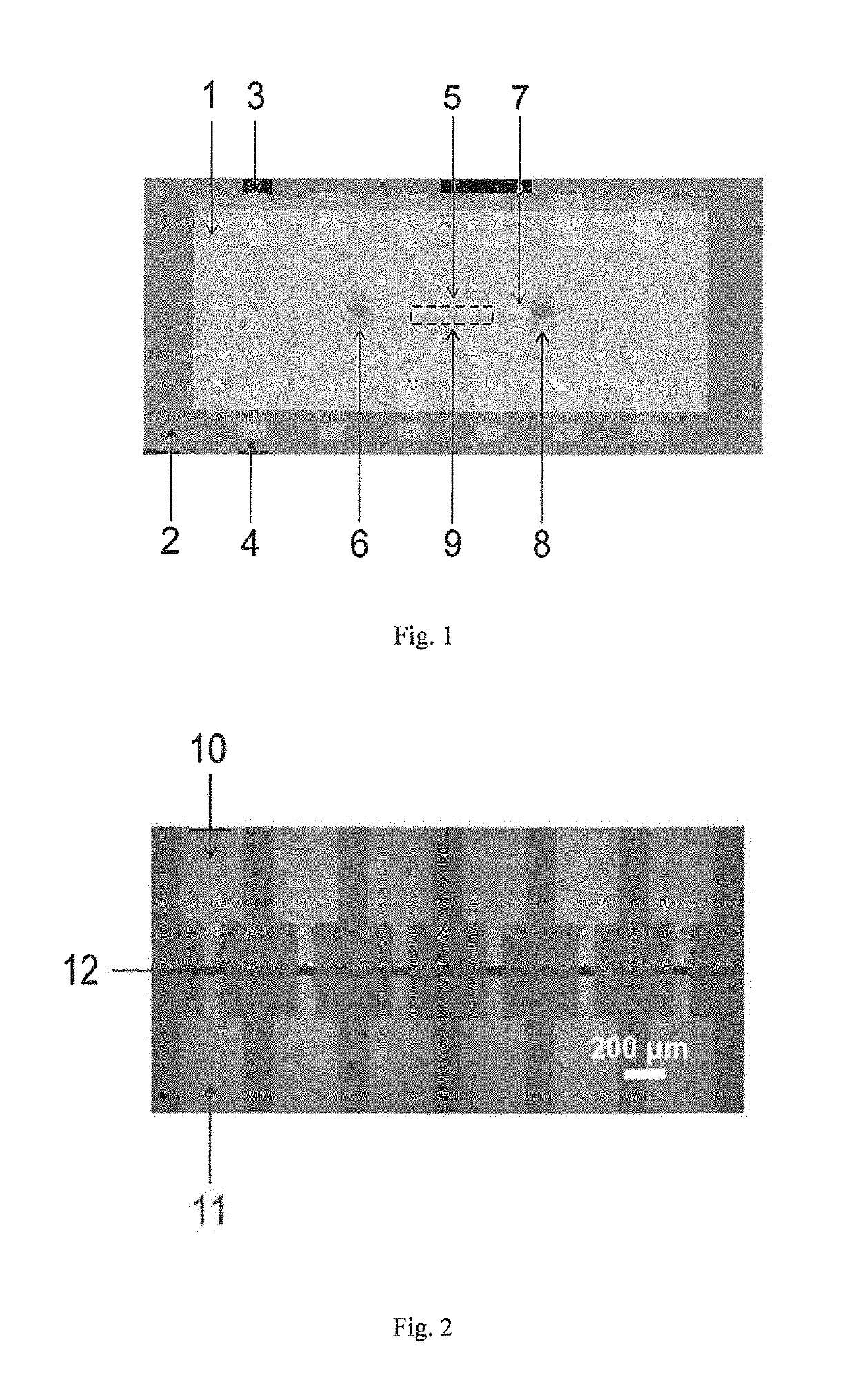

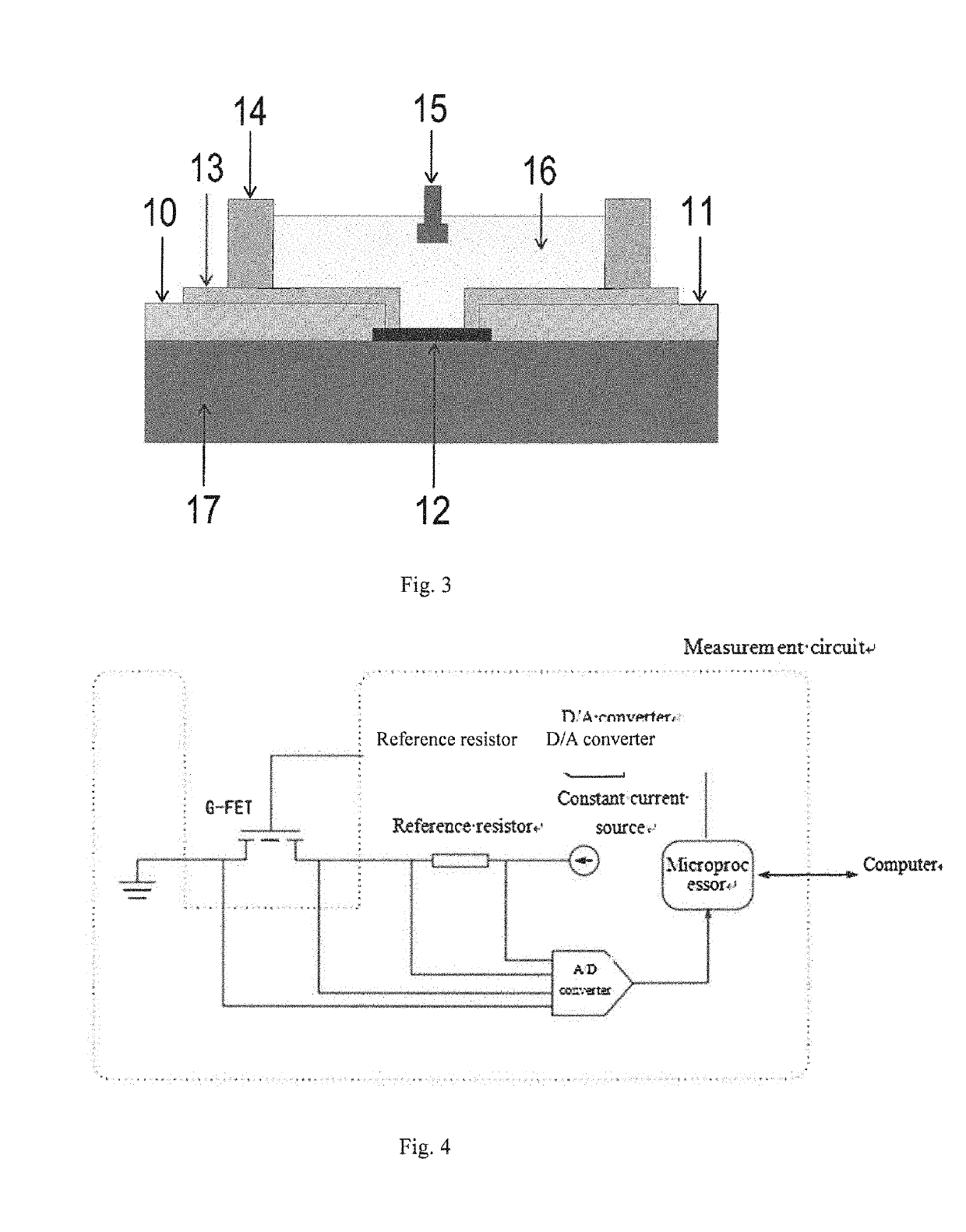

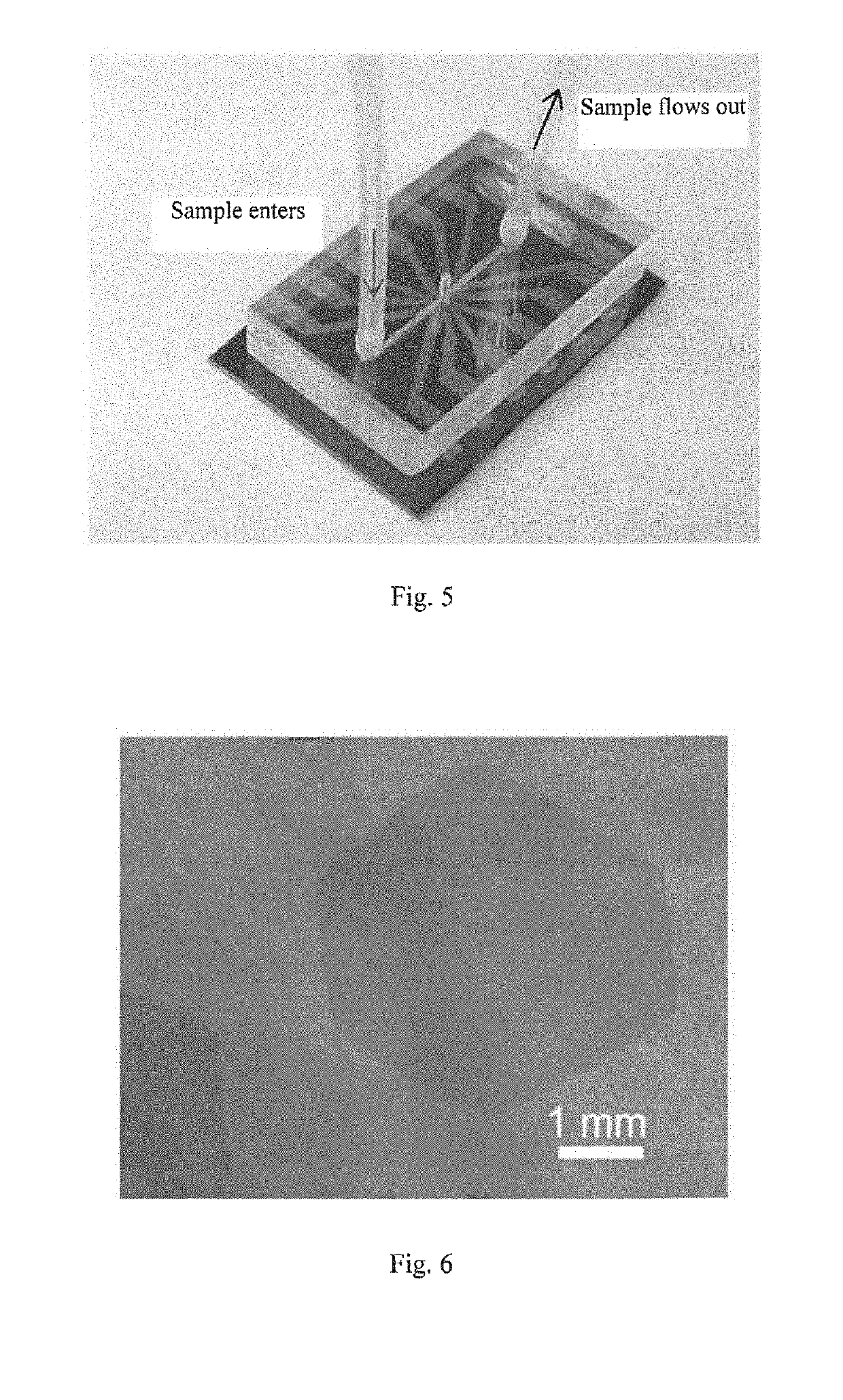

Sensing device and method in detecting binding affinity and binding kinetics between molecules

InactiveUS20190178837A1High sensitivityImprove stabilityMaterial analysis by electric/magnetic meansBinding energySignal-to-noise ratio (imaging)

A sensing device and method in detecting binding energy and binding kinetics between molecules; the sensing device has a sensor, a microfluidic chip and a measurement circuit. The sensor has multiple field effect transistors, and each field effect transistor adopts single-layer single crystal graphene as a conductive channel, thereby having extremely high sensitivity and stability; and the field effect transistors are arranged in an array and are provided with multichannel measurement circuits to detect the binding dynamics processes of different molecules or different copies of the same molecule in parallel so as to meet the high-throughput detection requirements. A compound that is non-covalently bound with the single-layer single crystal graphene as a medium to fix probe molecules on the surface of the conductive channel, thereby retaining the intrinsic structure of the graphene, and improving the signal-to-noise ratio and the sensitivity of the graphene field effect transistor.

Owner:DEZHOU UNIV

Process for preparing mesoporous graphene and field effect transistor biosensor based on mesoporous graphene

ActiveCN106198674AControl energy gapReduce manufacturing costMaterial analysis by electric/magnetic meansMicrosphereEvaporation

The invention relates to a process for preparing mesoporous graphene and a field effect transistor biosensor based on the mesoporous graphene. Periodically arranged nanometer microsphere arrays are assembled on the surface of graphene, evaporation of a metal film is performed, nanometer microspheres are removed, the metal film serves as a mask to prepare mesoporous graphene with different pore diameters is prepared, the mesoporous graphene having different hole pitches is obtained, and the goal of regulating energy gaps of the graphene is achieved; oxygen plasma is utilized to etch active oxygen-containing groups formed by the graphene, and bioactive molecules can be connected; use of common coupling agents such as AuNPs, glutaraldehyde, pyrenebutyric acid, 1-hydroxysuccinimide eater-1-pyrenebutyric acid is avoided, and the manufacturing cost of the biosensor is greatly reduced. According to the field effect transistor biosensor based on the mesoporous graphene, band gaps of the graphene are opened, the biosensor has a large current on / off ratio, a very small amount of biomolecules can make electric conductivity of a graphene conducting channel have a remarkable response, and the detection sensitivity is greatly improved.

Owner:GOLDEN SUN FUJIAN SOLAR TECHNIC

Semi-suspension graphene field effect transistor preparation method

ActiveCN105047562AAvoid damageAvoid contaminationSemiconductor/solid-state device manufacturingSemiconductor devicesGrapheneChemical vapor deposition

The invention discloses a semi-suspension graphene field effect transistor preparation method, and relates to the technical field of transistors. The semi-suspension graphene field effect transistor preparation method comprises the following steps that photoresist is coated on a substrate so that a photoresist pattern is formed; the photoresist pattern acts as a mask film to form a substrate structure with grooves; metal-based graphene is prepared via a chemical vapor deposition method; a metal layer is deposited on the upper surface of metal-based graphene; the metal base below metal-based graphene is corroded so that a graphene assembly is formed; the graphene assembly is transferred to the substrate structure with the grooves; a second photoresist pattern is formed on the upper surface of the metal layer; the second photoresist pattern acts as the mask film to form a drain electrode and a source electrode; and the second photoresist pattern acts as the mask film, and gate metal is deposited on an insulating medium. Damage and contamination of graphene can be avoided by the method. Interface scattering of the substrate is reduced by separation of graphene and the substrate so that high mobility of carriers in graphene is realized and high-frequency performance of a graphene transistor is enhanced.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

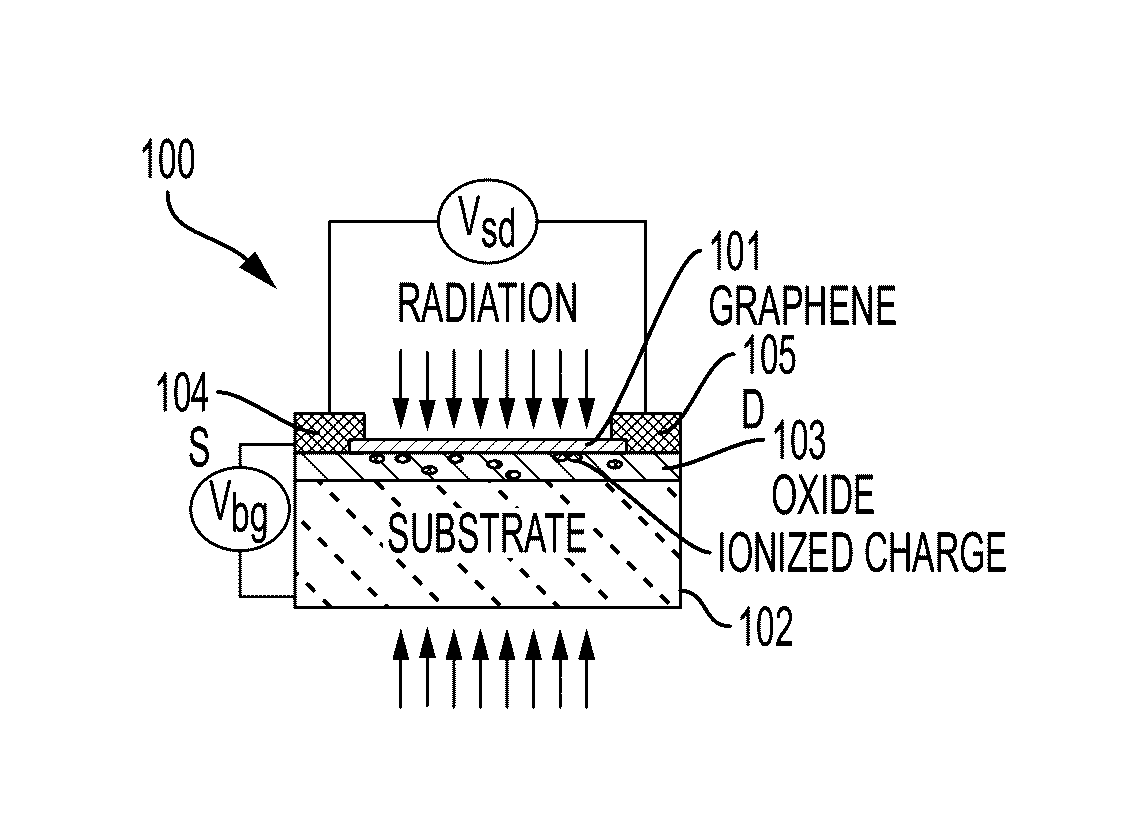

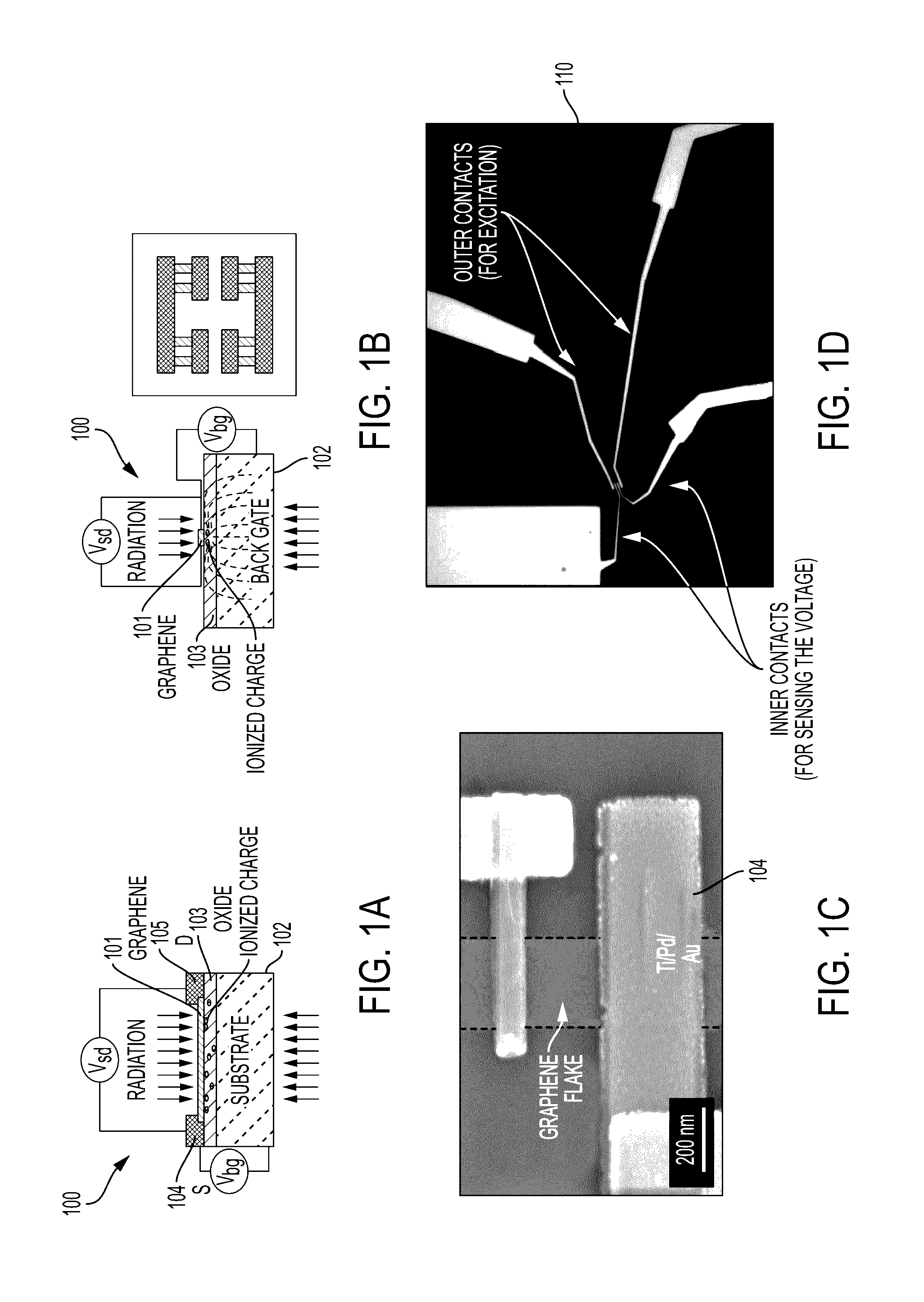

Graphene field effect transistor for radiation detection

ActiveUS9508885B1Low powerHigh sensitivityMaterial analysis by electric/magnetic meansPhotovoltaic energy generationRadiation sensorGraphene

The present invention relates to a graphene field effect transistor-based radiation sensor for use in a variety of radiation detection applications, including manned spaceflight missions. The sensing mechanism of the radiation sensor is based on the high sensitivity of graphene in the local change of electric field that can result from the interaction of ionizing radiation with a gated undoped silicon absorber serving as the supporting substrate in the graphene field effect transistor. The radiation sensor has low power and high sensitivity, a flexible structure, and a wide temperature range, and can be used in a variety of applications, particularly in space missions for human exploration.

Owner:NASA +1

Enhanced graphene field-effect transistor

InactiveCN102593159AAchieving Saturation CharacteristicsImplement featuresSemiconductor devicesRoom temperatureGraphene

At present, graphene has become a hot research topic among domestic and foreign scientists. The graphene is now mainly used as a channel material of a field-effect transistor. However, the graphene is a zero gap material, has a ballistic effect at room temperature, and is always in an open state, so that the application of the graphene in the electronic field is limited. In order to overcome the shortcoming, the invention provides an enhanced graphene field-effect transistor, which belongs to the fields of microelectronics and solid state electronics. The enhanced graphene field-effect transistor comprises a gate region, a source region, a drain region, a channel region and a source and drain semiconductor doped region, wherein the channel region is formed by a graphene layer and a channel semiconductor doped layer; a N-type device channel semiconductor layer is doped with P-type impurities; and a P-type device channel semiconductor layer is doped with N-type impurities. By adoption of the device structure, the switching characteristic and saturation characteristic of the device can be realized, so that the graphene device can be well applied in an integrated circuit.

Owner:SICHUAN UNIV

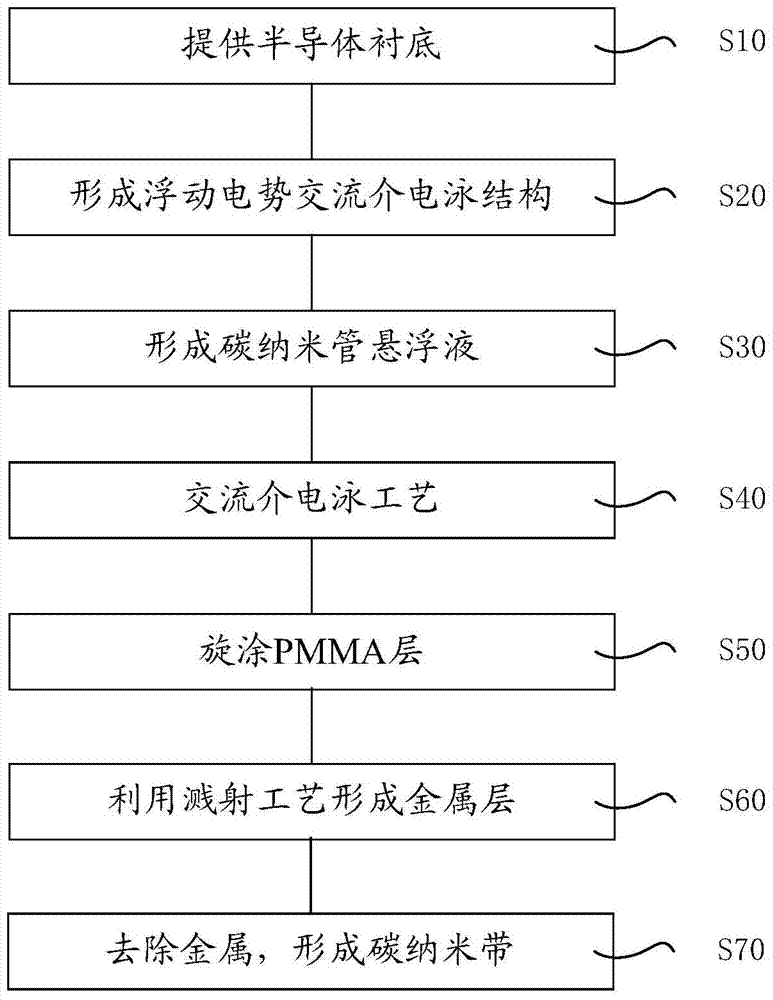

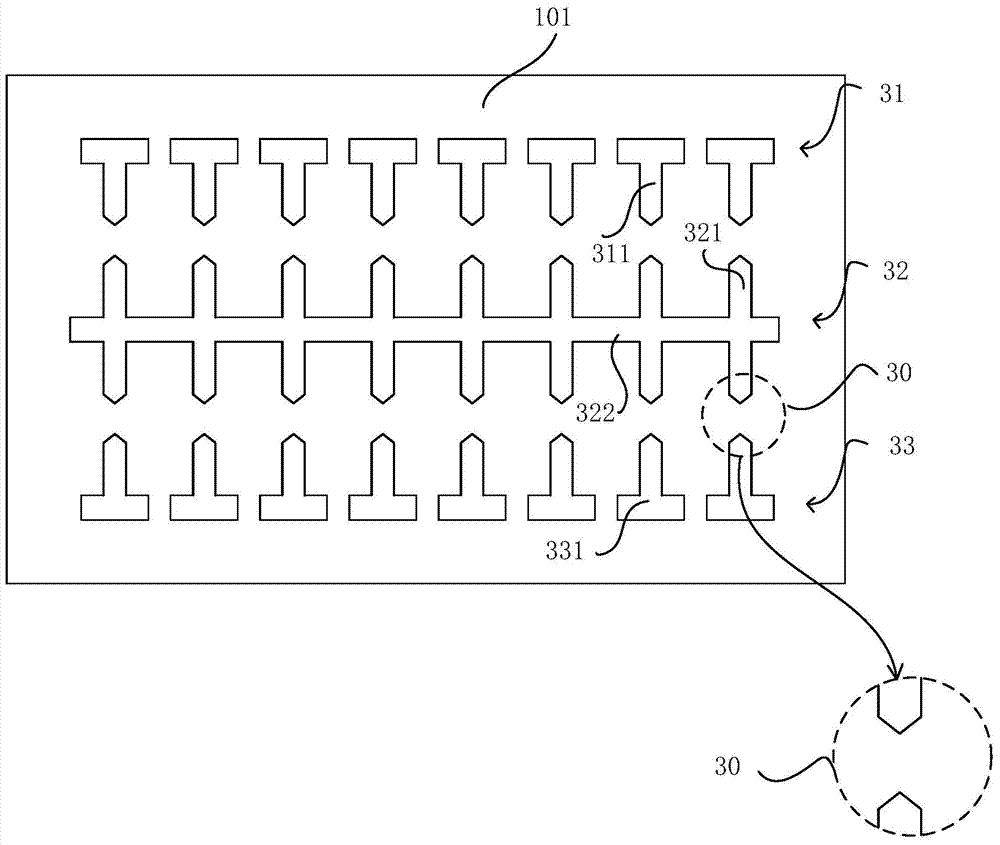

Production method of graphene field-effect transistor

ActiveCN103531482AAchieve separationPrecise alignmentTransistorSemiconductor/solid-state device manufacturingElectricityGraphene nanoribbons

The invention provides a production method of a graphene field-effect transistor. The production method comprises the steps as follows: a semiconductor substrate with a silicon dioxide layer formed on the surface is provided; a floating potential alternating current dielectrophoresis structure is formed and comprises a first electrode part, a second electrode part and a third electrode part, wherein the first electrode part at least comprises a first sub-electrode, the second electrode part at least comprises a second sub-electrode and a sub-electrode connecting wire, the third electrode part at least comprises a third sub-electrode, the sub-electrode connecting wire is connected with each second sub-electrode in a penetrating manner, and top ends of each second sub-electrode and each third sub-electrode are in one-to-one correspondence; a carbon nanotube suspension is formed; a carbon nanotube is connected between each second sub-electrode and each third sub-electrode which are opposite to each other by utilizing an alternating current dielectrophoresis technology; each carbon nanotube is fixed; metal layers are formed by utilizing a sputtering technology; and metal is removed and graphene nanoribbons are formed. According to the production method, the perfect alignment of single carbon nanotubes is realized in a batch manner, and single-walled carbon nanotubes are cut into graphene nanoribbons, so that the graphene nanoribbons can present typical semiconductor characteristics.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

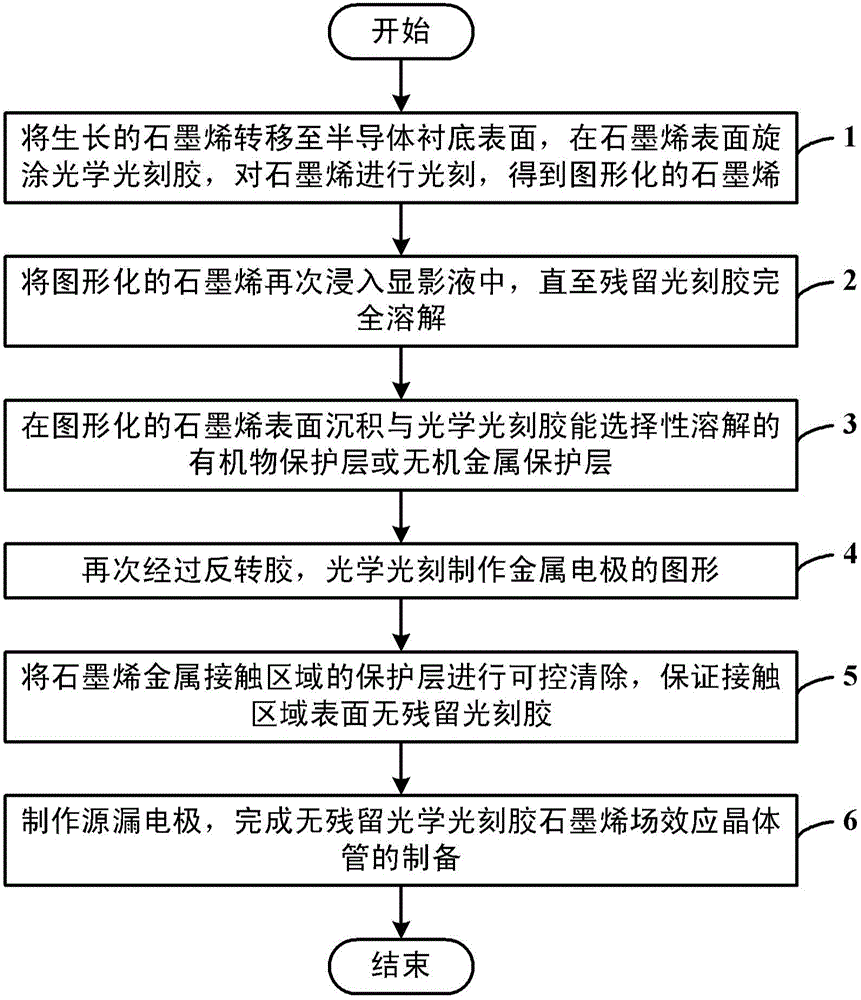

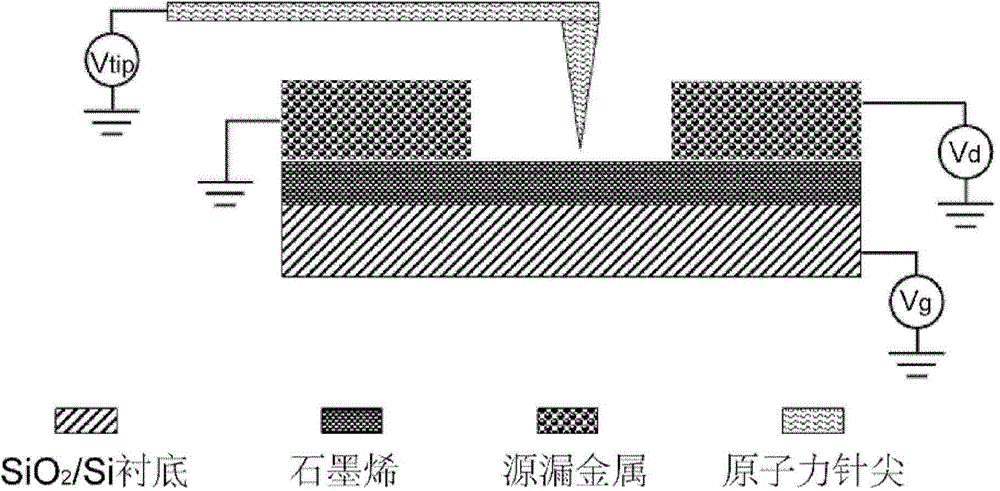

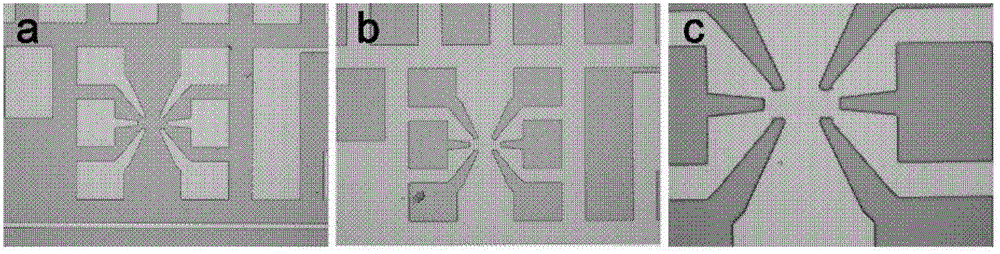

Manufacturing method and in-situ characterizing method for graphene field effect transistor free of residual optical photoresist

ActiveCN104465400AWon't hurtReduce the degree of dopingSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingAtomic force microscopyLithographic artist

The invention discloses a manufacturing method and an in-situ characterizing method for a graphene field effect transistor free of residual optical photoresist. The manufacturing method includes the following steps that growing graphene is transferred to the surface of a semiconductor substrate, the surface of the graphene is coated with optical photoresist in a spinning mode, photoetching is conducted on the graphene, and patterned graphene is obtained; the patterned graphene is immersed into a developing solution again until the residual optical photoresist is dissolved completely; an organic matter protecting layer or an inorganic metal protecting layer capable of being selectively dissolved with the optical photoresist is deposited on the surface of the patterned graphene; patterns of a metal electrode are made again through inversion photoresist in an optical lithography mode; the protecting layer of the graphene-metal contact region is cleared away controllably, and it is guaranteed that no photoresist remains on the surface of the contact region; source and drain electrodes are made, and manufacturing of the graphene field effect transistor free of the residual optical photoresist is completed. Influences of the residual optical photoresist on the carrier mobility of the graphene are characterized by means of the technologies such as atomic force microscopy and electrostatic force microscopy.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

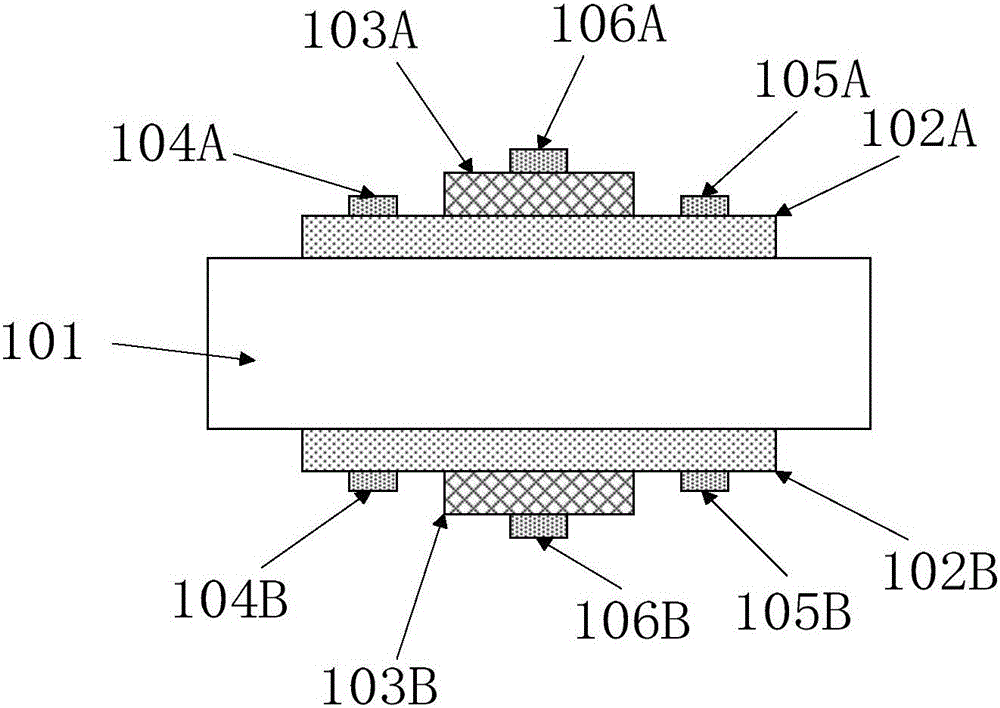

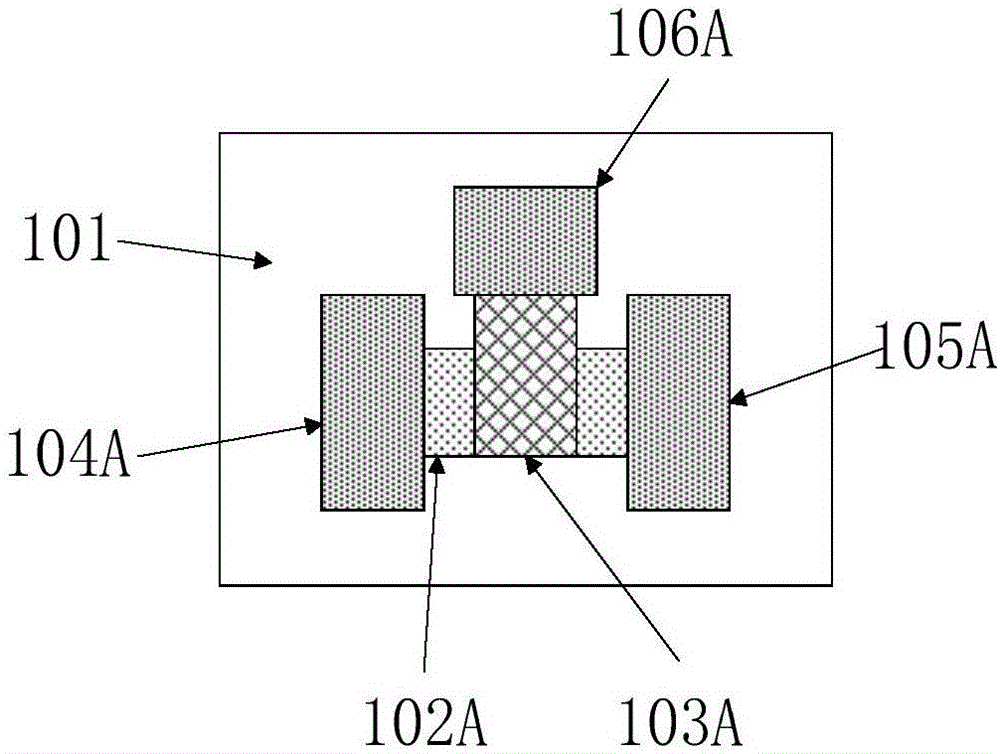

Multi-stage terahertz modulator based on flexible graphene field effect transistor structure

ActiveCN106646930AImprove permeabilityModulate transmission amplitudeNon-linear opticsGrapheneCondensed matter physics

The invention belongs to the technical field of terahertz wave application, and provides a multi-stage terahertz modulator based on a flexible graphene field effect transistor structure. The multi-stage terahertz modulator is used for overcoming the defects that an existing graphene transistor terahertz modulator is small in modulation depth and only the switch-on state and the switch-off state can be achieved. The terahertz modulator is of an up-and-down-symmetry structure, and comprises a substrate, graphene films, ionic gum, source electrodes, drain electrodes and gate electrodes, wherein the graphene films, the ionic gum, the source electrodes, the drain electrodes and the gate electrodes are symmetrically arranged on the upper surface and the lower surface of the substrate, the graphene films are arranged on the surfaces of the substrate, the source electrodes, the ionic gum and the drain electrodes are arranged on the surfaces of the graphene films, and the gate electrodes are arranged on the surfaces of the ionic gum. According to the terahertz modulator, two flexible graphene field effect transistors are arranged on the two sides of the same flexible substrate, the modulation depth of the modulator can be increased by 37% or above, and meanwhile four-stage modulation of the amplitude of terahertz waves can be achieved through cascade controlling.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Graphene field effect transistor structure and large-scale manufacturing process thereof

ActiveCN104538449AEnable mass manufacturingOvercome difficultySemiconductor/solid-state device manufacturingSemiconductor devicesCatalytic metalCvd graphene

The invention discloses a graphene field effect transistor structure and a large-scale manufacturing process of the graphene field effect transistor structure. The manufacturing process comprises the steps that firstly, selective growing is carried out on a bottom h-BN dielectric layer and a graphene layer on a catalytic metal thin film layer according to the characteristic of the catalytic metal thin film layer, then photoetching is carried out on the catalytic metal thin film layer, the shape of the bottom h-BN dielectric layer and the graphene layer growing epitaxially is controlled, and finally two-time photoetching on the catalytic metal thin film layer and growing of a top grid h-BN dielectric layer are achieved through structure inversion and connection of two times. The structure comprises the bottom h-BN dielectric layer, the graphene layer and the top grid h-BN dielectric layer, the bottom h-BN dielectric layer, the graphene layer and the top grid h-BN dielectric layer are sequentially arranged from bottom to top, a grid electrode is arranged on the top grid h-BN dielectric layer, and a source electrode and a drain electrode are guided out of the two sides of the graphene layer. According to the graphene field effect transistor structure and the manufacturing process, the problem that an existing process is high in difficulty, low in rate of finished products and poor in product performance is solved, and a good foundation is laid for manufacturing of a graphene-based integrated circuit.

Owner:广西北部湾粮油技术研究有限公司

Low-power-consumption thin back gate graphene field effect transistor manufacturing method

InactiveCN103943511AReduce power consumptionReduce carrier concentrationTransistorSemiconductor/solid-state device manufacturingAlloyCvd graphene

The invention discloses a low-power-consumption thin back gate graphene field effect transistor manufacturing method. A SiO2 dielectric layer is grown on the surface of an n-type Si substrate through heat, the SiO2 dielectric layer is subjected to photoetching, the SiO2 dielectric layer is etched with reactive ions after development, grooves are formed, graphene is transferred to the etched SiO2 dielectric layer, graphene channels are formed, TiW alloy with the thickness of 5 nm and Au with the thickness of 100 nm are sequentially arranged on the surfaces of the graphene channels in a sputtering mode, then, photoetching is performed, the TiW / Au is corroded to form a linear Au connecting wire and an Au electrode plate after development, a source electrode and a drain electrode are formed, and the purpose of low power consumption and the purpose of high performance are effectively achieved.

Owner:JIANGSU UNIV

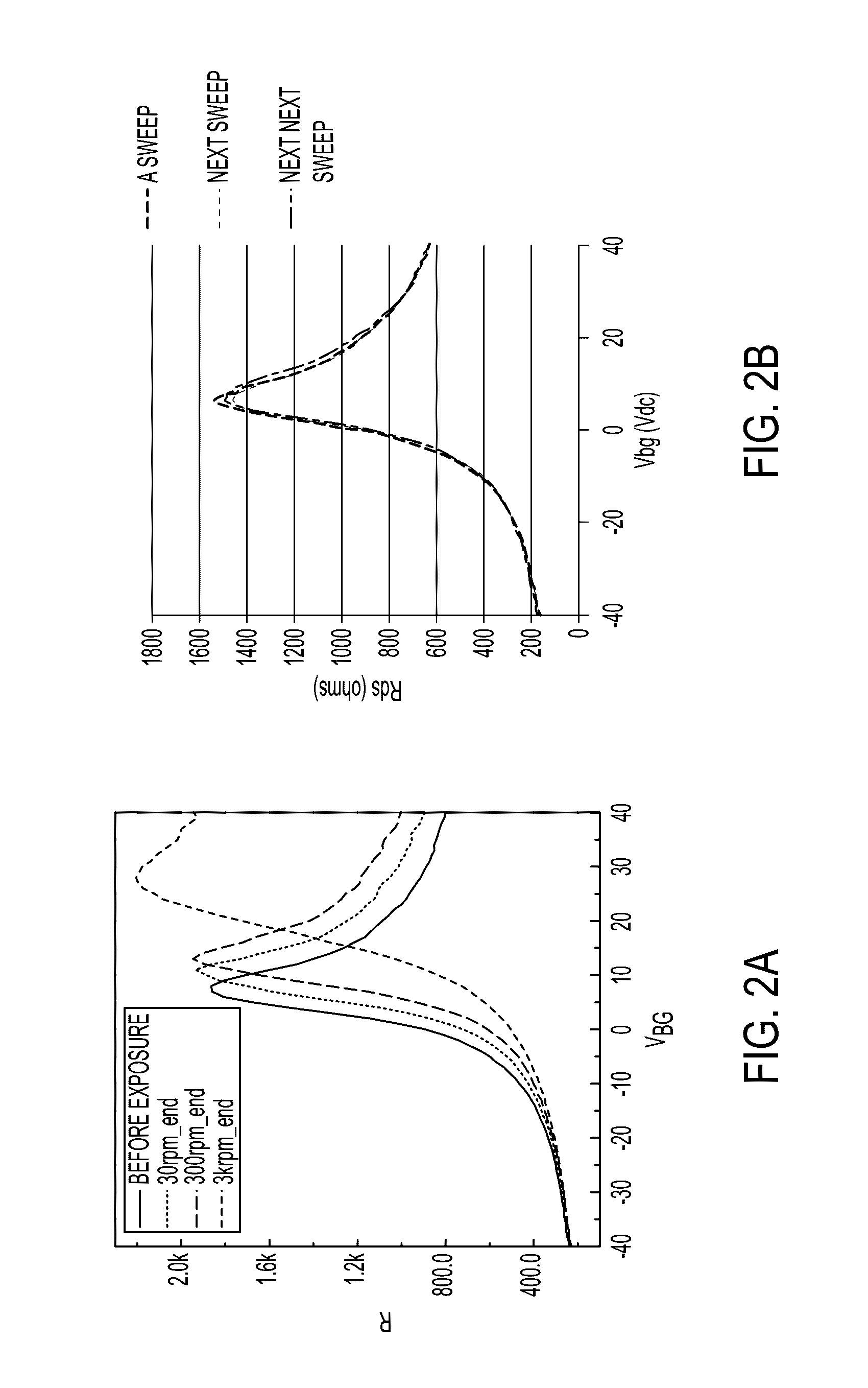

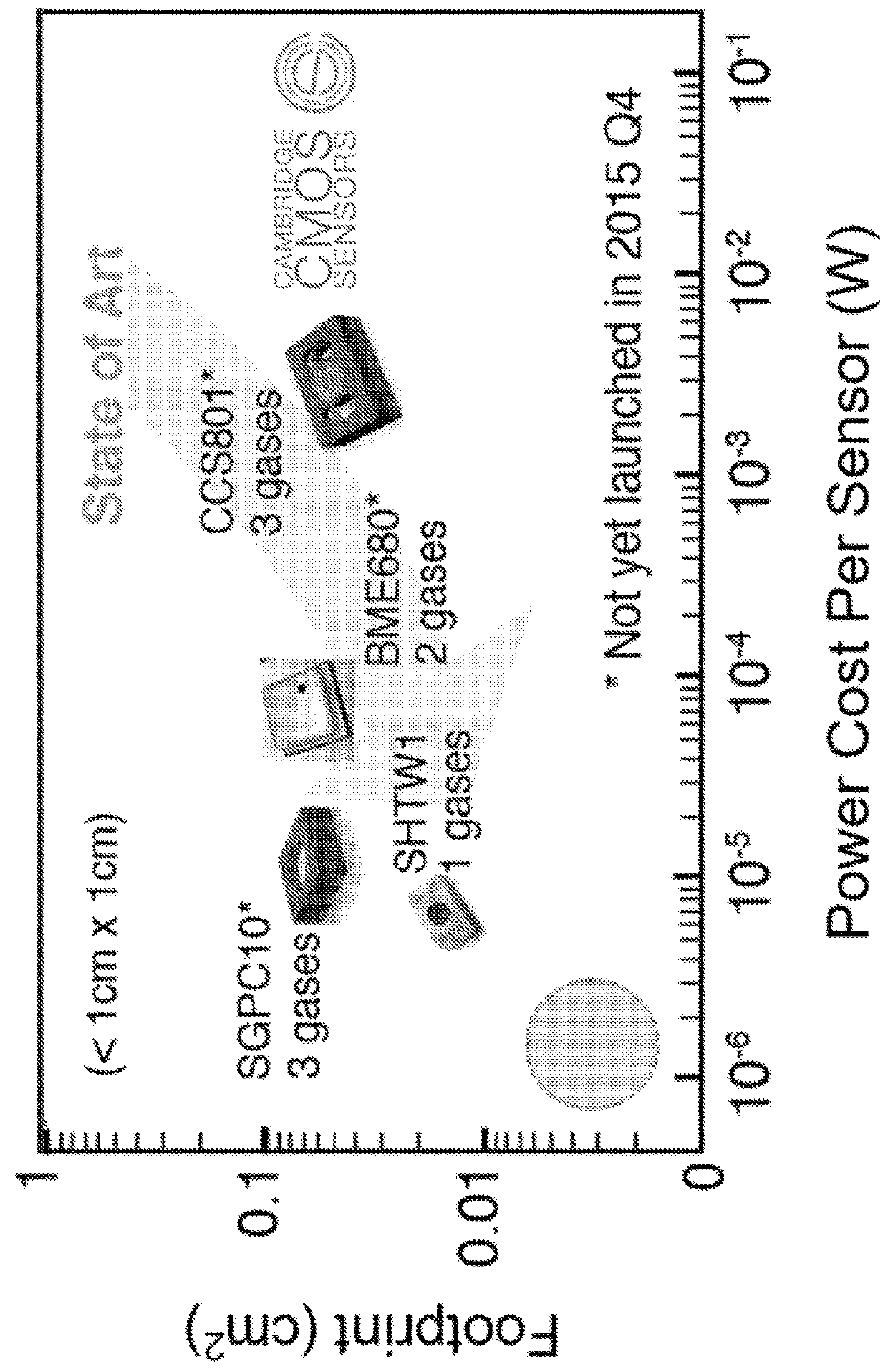

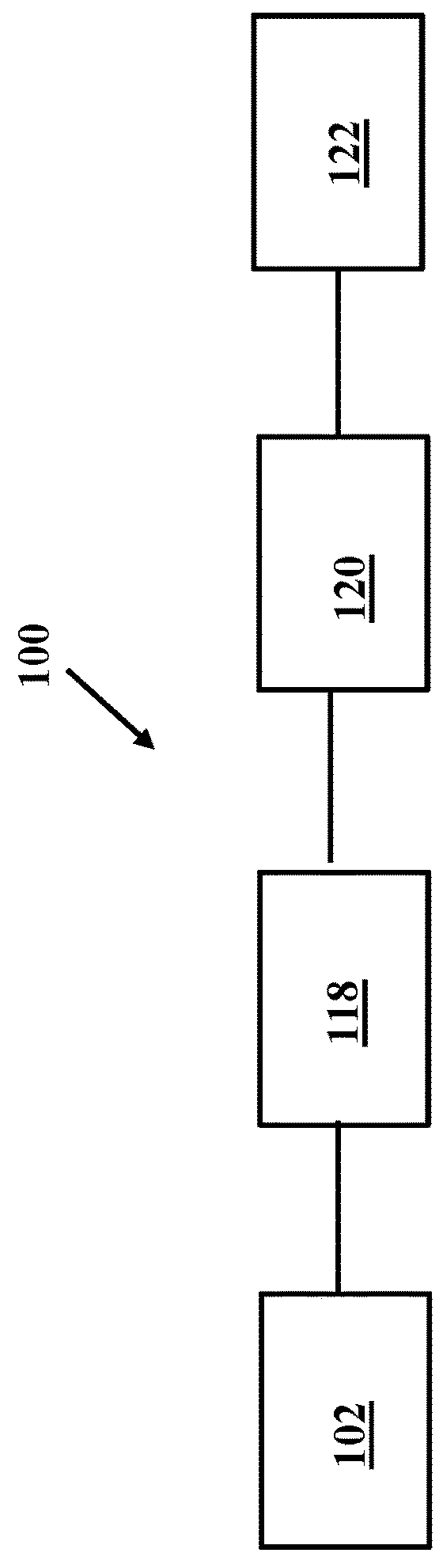

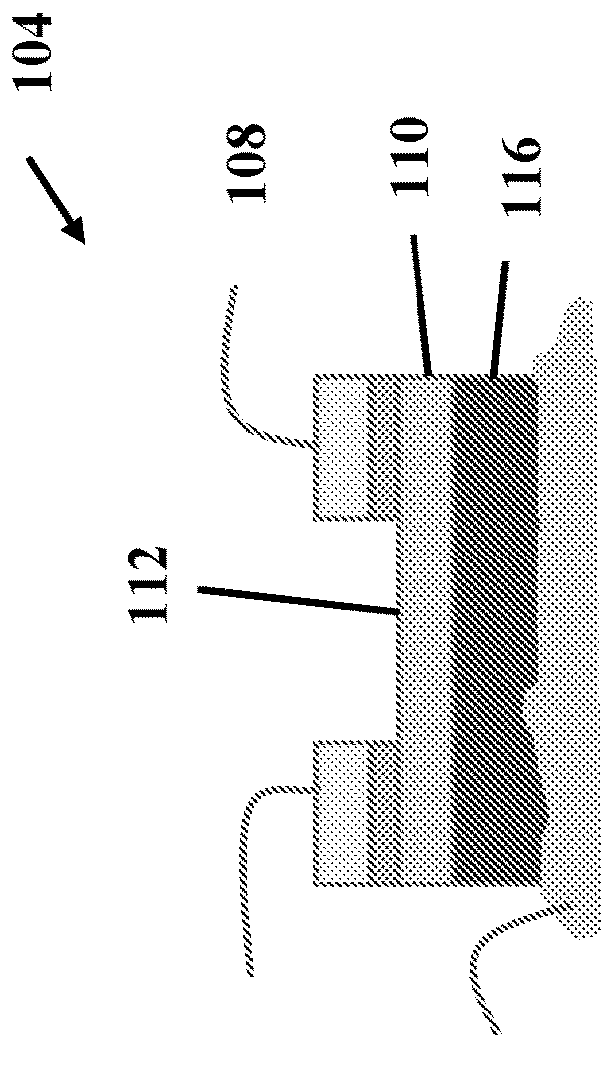

Gas detection systems and methods using graphene field effect transistors

InactiveUS20180180573A1Modulate responseTransistorMaterial analysis by electric/magnetic meansElectricityGraphene

A gas detection system for selectively detecting one or more gases from a mixture of gases includes a gas sensor that includes at least one graphene field effect transistor (GFET). The GFET includes a source electrode, a drain electrode, a graphene channel layer, a gate electrode arranged proximate the graphene channel layer, and a dielectric layer between the graphene channel layer and the gate electrode. The gas detection system also includes a modulation system electrically connected to the gate electrode to modulate a response of the GFET to the gas sample, a detector electrically connected to the source electrode and the drain electrode to detect a modulated signal containing information concerning a response of the GFET to the gas sample during modulation by the modulation system, and a signal processor configured to communicate with the detector to receive the modulated signal. The signal processor is further configured to selectively determine a concentration of at least one gas in the gas sample based at least on the modulated signal.

Owner:RGT UNIV OF CALIFORNIA

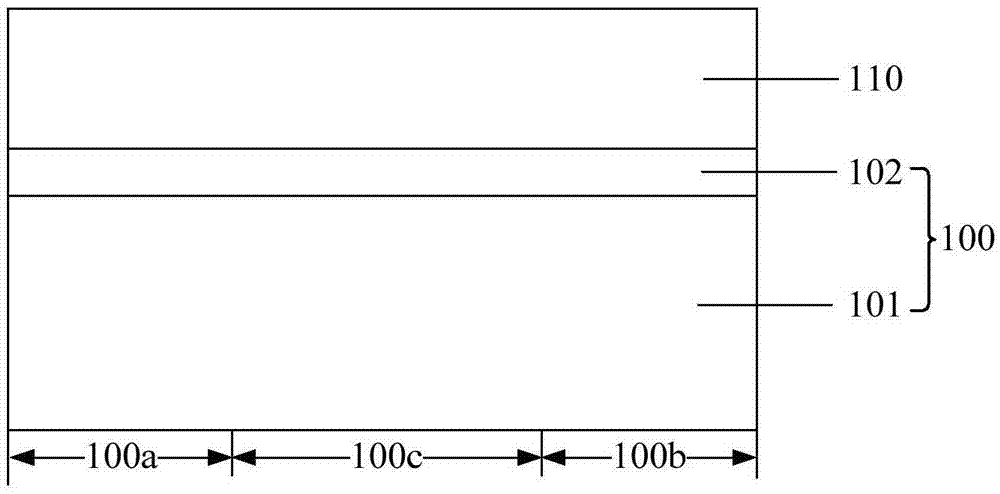

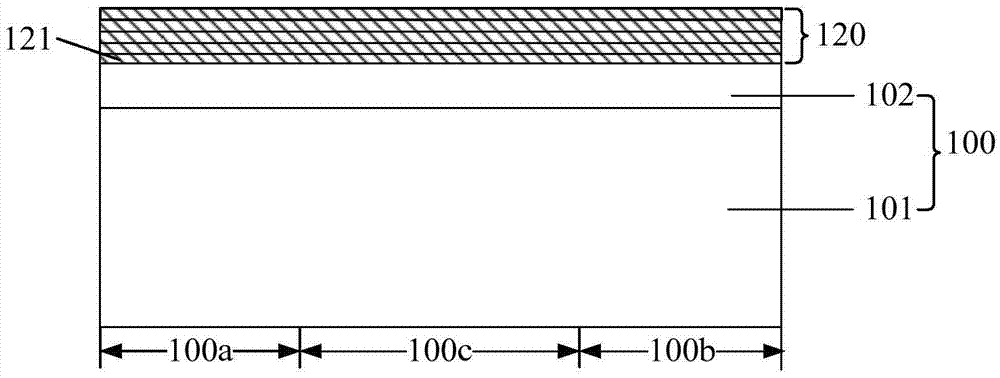

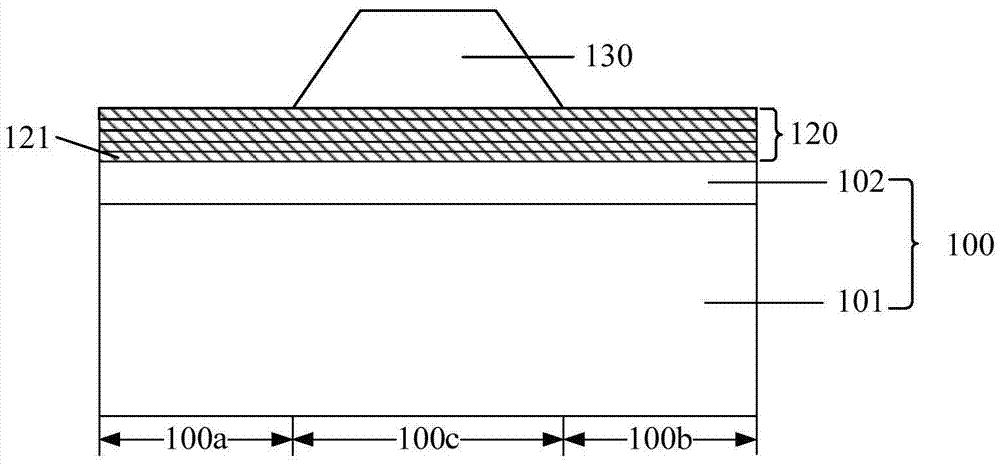

Graphene field-effect transistor and formation method thereof

ActiveCN106952949AIn situ growthAvoid destructionSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricGraphite

The invention relates to a graphene field-effect transistor and a formation method thereof. The formation method of the graphene field-effect transistor comprises the steps of providing a substrate, wherein the substrate comprises a first region, a second region and a third region, and the third region is arranged between the first region and the second region; forming a graphite material layer on the substrate; processing the graphite material layer to form multi-layer graphene; removing a part of multi-layer graphene on the first region and the second region from a thickness direction to form single-layer graphene or dual-layer graphene; forming a gate dielectric layer on a surface of the multi-layer graphene on the third region; removing a part of the single-layer graphene or the dual-layer graphene on the first region and the second region to respectively form a source region and a drain region; and respectively forming electrodes on the source region, the drain region and the gate dielectric layer. With the formation method disclosed by the embodiment of the invention, the in-situ growth of the graphene is achieved, a graphene preparation method from top to bottom is employed, the process is simplified, and the process is easy to control.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1