Low-power-consumption thin back gate graphene field effect transistor manufacturing method

A technology of field effect transistors and graphene, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of high power consumption and large input voltage, and achieve low power consumption, reduce power consumption, and promote development. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

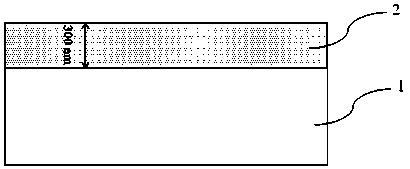

[0016] When the gate oxide of the field effect transistor is 300 nm, the gate voltage range required for its transfer characteristics is about -150~150 V, which is a very large span, which is not suitable for the power consumption of general micro-nano electronic devices. For sensors based on graphene field-effect transistors, it is desirable to control the input voltage within the range of 5 V, which is conducive to the application of portable graphene devices. In order to ensure the performance of the graphene field effect transistor and provide sufficient current drive when the gate voltage is reduced, it is necessary to reduce the thickness of the gate oxide, so reactive ion etching technology is used to obtain a thin gate oxide.

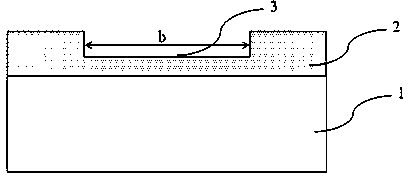

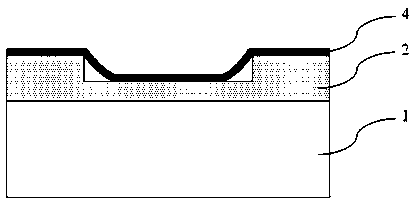

[0017] see figure 1 , thermally grow 300 nm thick SiO on the surface of n-type Si substrate 1 with a resistivity of 1~10 Ωcm 2 Medium layer 2. see figure 2 , using mask No. 1 for SiO 2 Dielectric layer 2 is subjected to photolithography, an...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Resistivity | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More