Nanowire based vertical circular grating transistor and preparation method thereof

A nanowire and transistor technology, applied in the field of nanoelectronics, achieves the effects of improving transconductance, suppressing short-channel effect, and reducing parasitic resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] In the following, the present invention will be further described in detail by taking a vertical gate-around transistor based on InAs nanowires as an example in conjunction with the accompanying drawings.

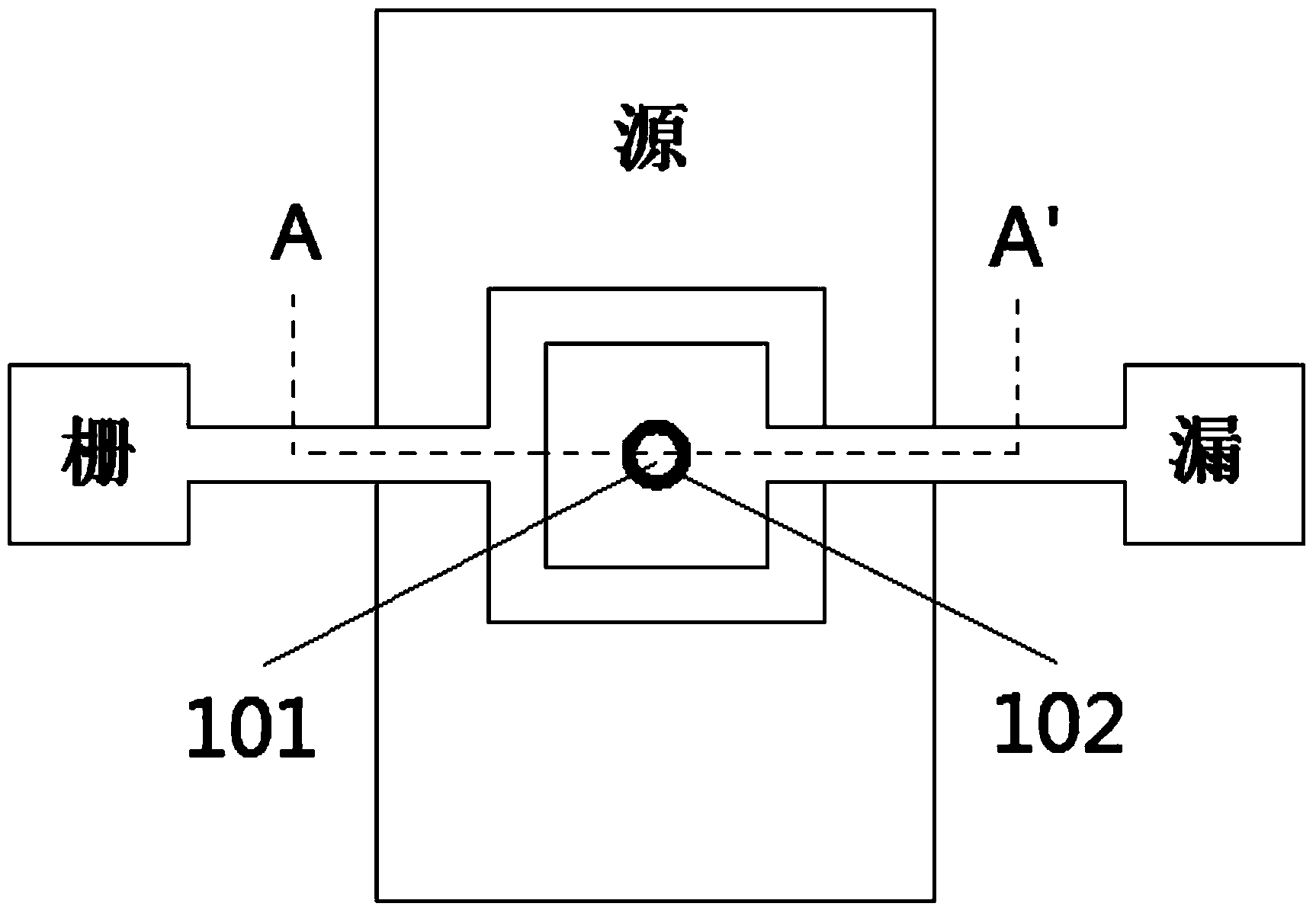

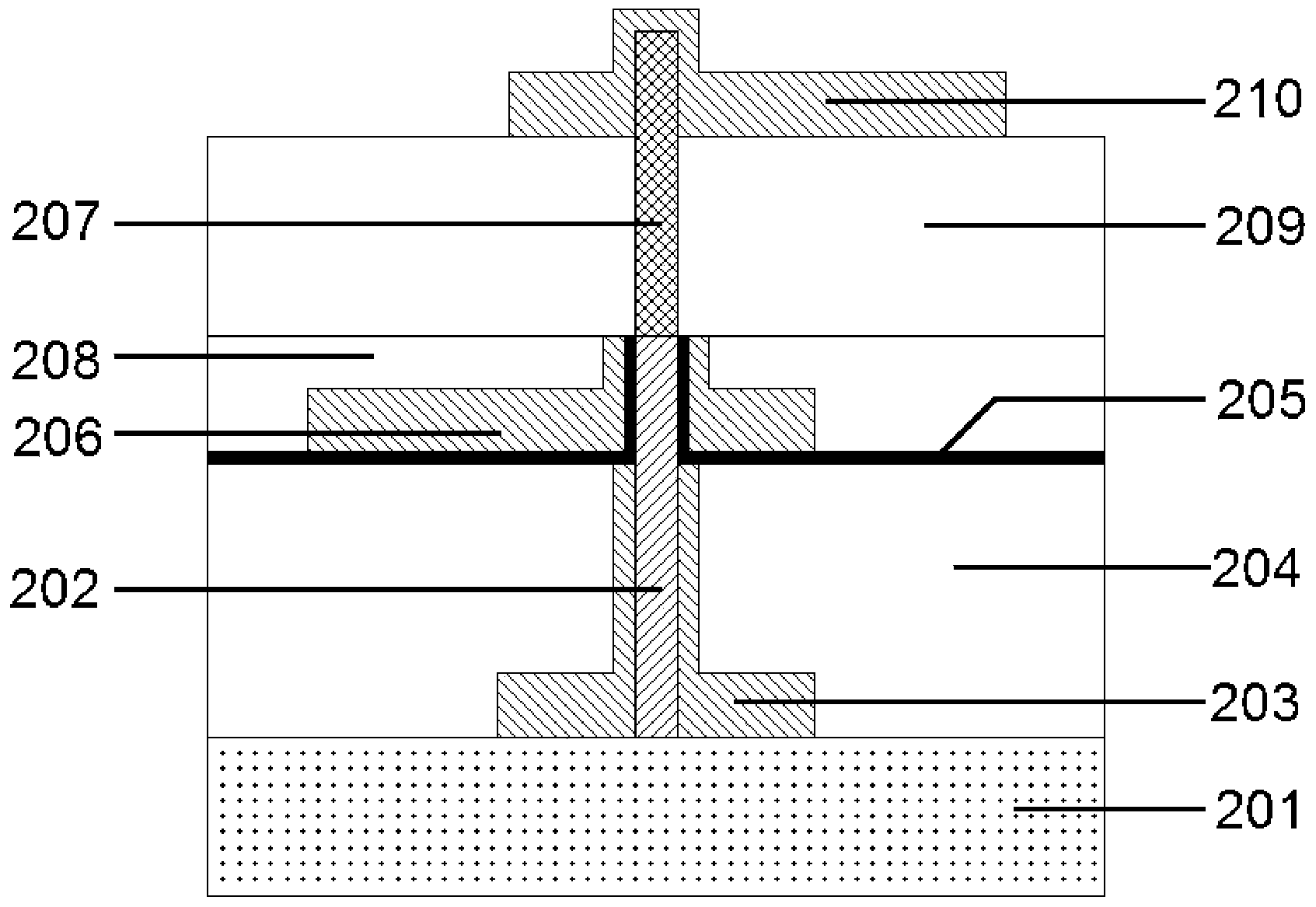

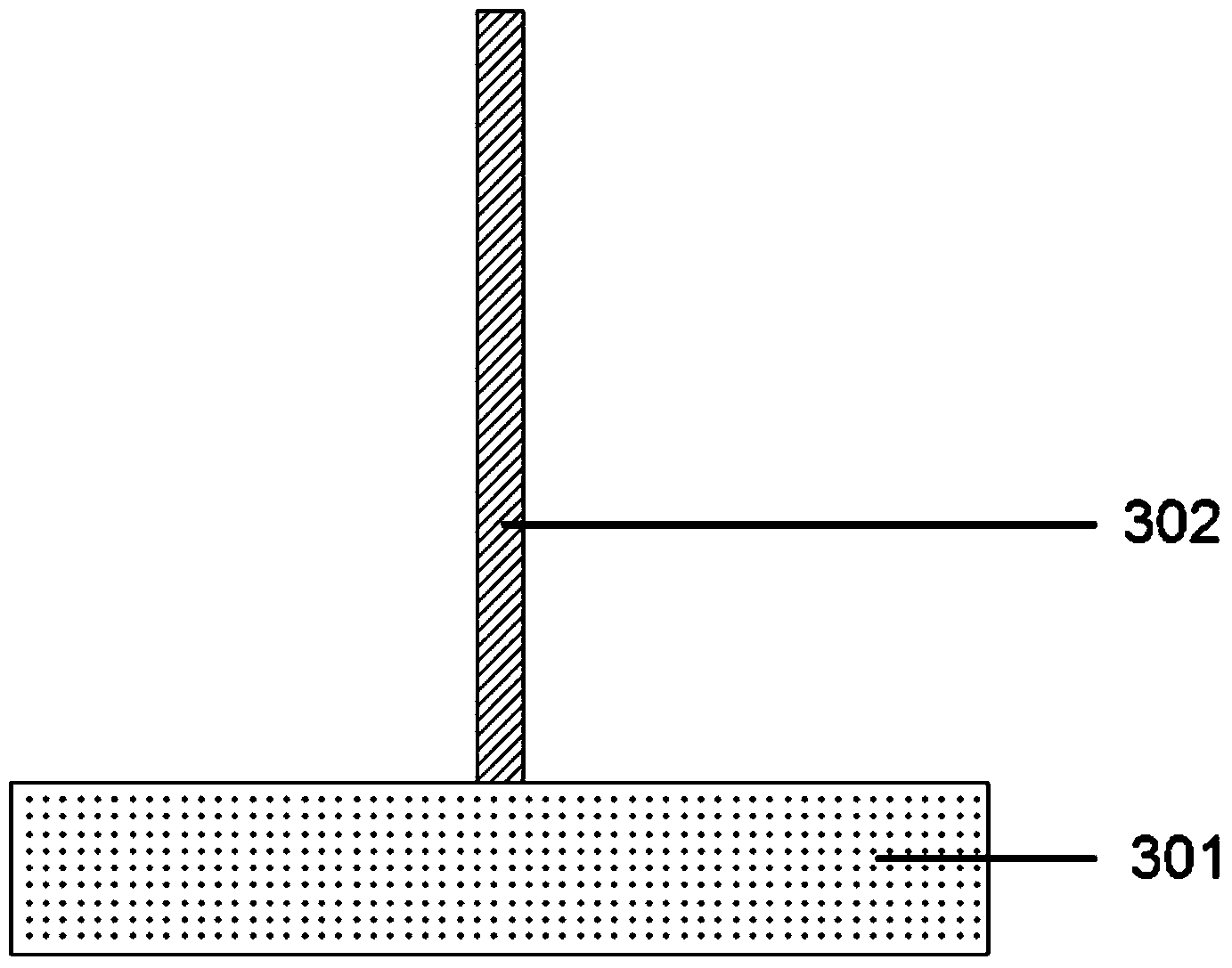

[0047] figure 1 is a schematic top view of the embodiment transistor, figure 2 is along figure 1 The cross-sectional schematic diagram of A-A' direction in the figure. The substrate can be single crystal silicon or single crystal silicon covered with a layer of silicon oxide, the intrinsic or low-doped InAs nanowires are perpendicular to the substrate surface, and there is no gap on the intrinsic or low-doped InAs nanowires The low-resistance nanowires are connected. The low-resistance nanowires can be heavily doped InAs nanowires or InAs-metal alloy nanowires. The intrinsic or low-doped InAs nanowires are respectively source electrodes, The gate dielectric and the gate electrode are surrounded by the low-resistance nanowire from bottom to top and are respectivel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More