A shifting register unit, a grid electrode driving circuit, and a display

A shift register and driving voltage technology, applied in static memory, static indicators, digital memory information, etc., can solve the problems of large layout area, increase of peripheral circuit load and total power consumption, occupation, etc., and achieve a small layout occupation area , reduced rise and fall times, and reduced complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

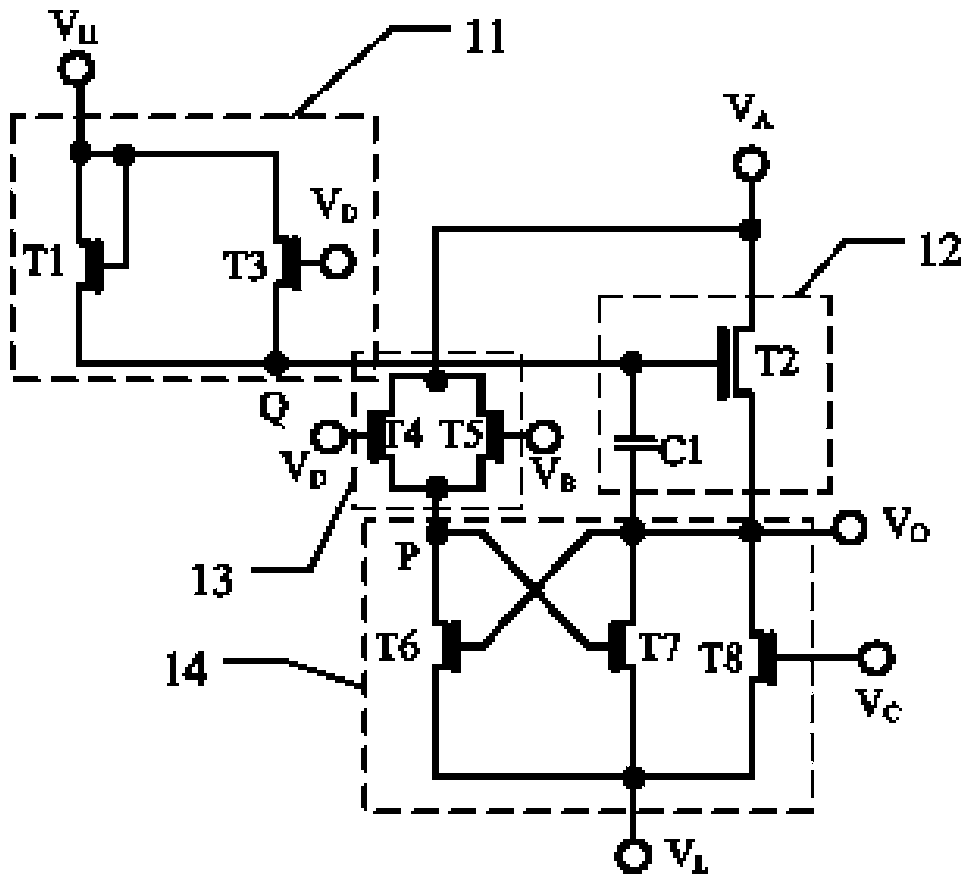

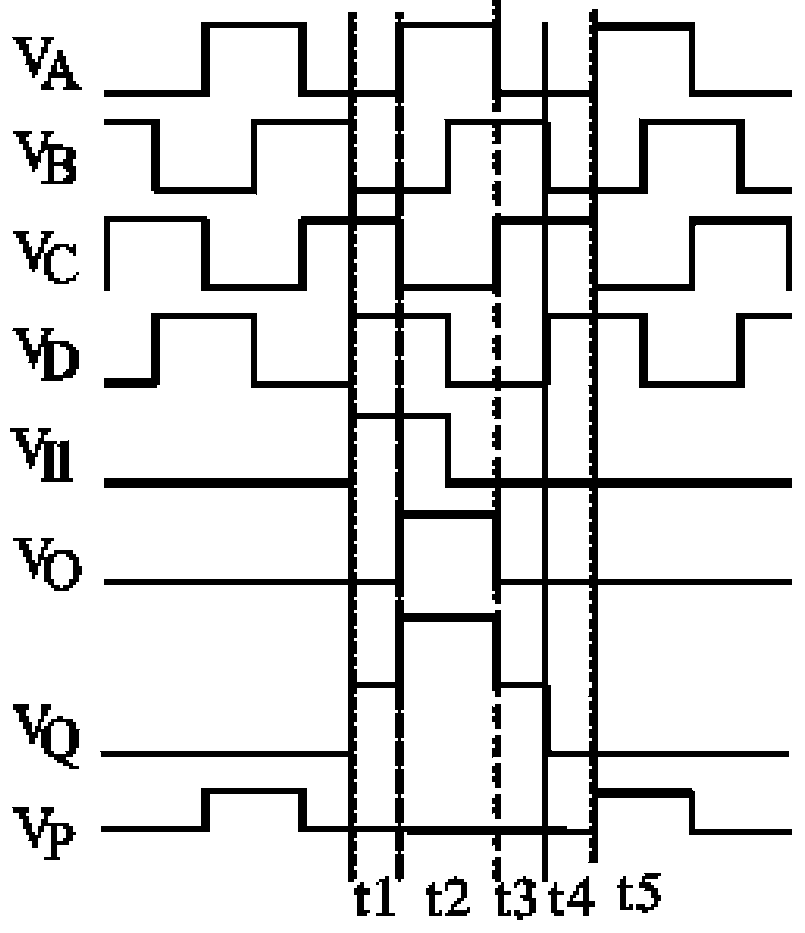

[0056] The shift register unit is a very important unit circuit to realize the gate drive circuit, such as figure 1 with figure 2 As shown, the shift register unit of this embodiment includes a charging and discharging module 11 , a driving module 12 , a low-level maintaining enabling module 13 and a low-level maintaining module 14 .

[0057] The signal input terminals of the charging and discharging module 11 are respectively connected to the pulse signal input terminal and the fourth clock signal input terminal for inputting the pulse signal V I1 and the fourth clock signal V D ; The clock input end of the drive module 12 is connected to the first clock signal input end, and the first clock signal V is input A , the drive module 12 has a drive enabling control terminal Q, the output terminal of the charging and discharging module 11 is connected to the driving enabling control terminal Q of the driving module 12, and the charging and discharging module 11 is used to input...

Embodiment 2

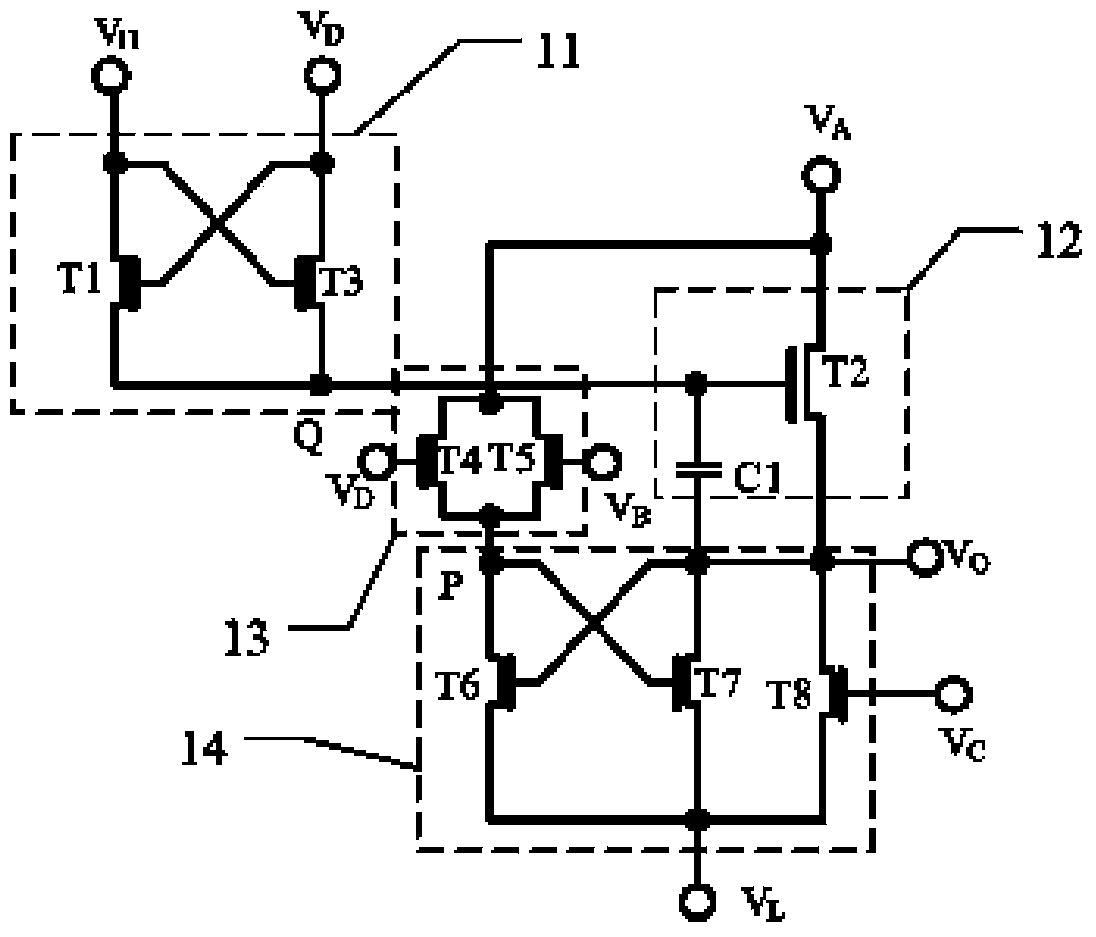

[0095] As shown in Fig. 4, it is the circuit diagram of the embodiment of the second shift register unit, the shift register unit of this embodiment includes a pair of subunit circuits, wherein one subunit circuit is as Figure 4-a As shown, it includes: drive module A12, charge and discharge module A11, low level maintenance module A14 and low level maintenance enabling module A13; another subunit circuit such as Figure 4-b As shown, it includes: a driving module B12, a charging and discharging module B11, a low level maintaining module B14 and a low level maintaining enabling module B13. The only difference between the two is that the signal input of the low-level maintenance enabling module A13 includes the first extended clock signal ECK1, while the signal input of the corresponding port of the low-level maintenance enabling module B13 is the same as the first extended clock signal ECK1. Complementary second extended clock signal ECK2.

[0096] The signal input terminals...

Embodiment 3

[0109] Such as Figure 5 Shown is a structural block diagram of a gate drive circuit disclosed in the present invention. The gate drive circuit includes a shift register, and the shift register uses N+1 stages of shift register units in series as described in the above-mentioned embodiment 1. Where N is a positive integer. The gate drive circuit also includes a first clock line line1, a second clock line line2, a third clock line line3, a fourth clock line line4, and a general common ground line L-V L and a start signal line STV. Wherein, the signal output terminals of the driving circuit units of the first level to the Nth level provide the gate driving signal V for the pixel array. G 1 ~V G N , and V G 1 ~V G N They are respectively coupled to the pulse signal input terminals of their own next-stage shift register units, and are used to start the next-stage shift register units; the N+1th stage is an additional stage, V G N+1 Return the pulse signal input end of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More