Packaging structure and forming method thereof

A packaging structure, dry deglue technology, applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the problems of reliability failure, low reliability of packaging structure stability, etc., to achieve improved stability, improved mechanical strength, Good adhesion effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

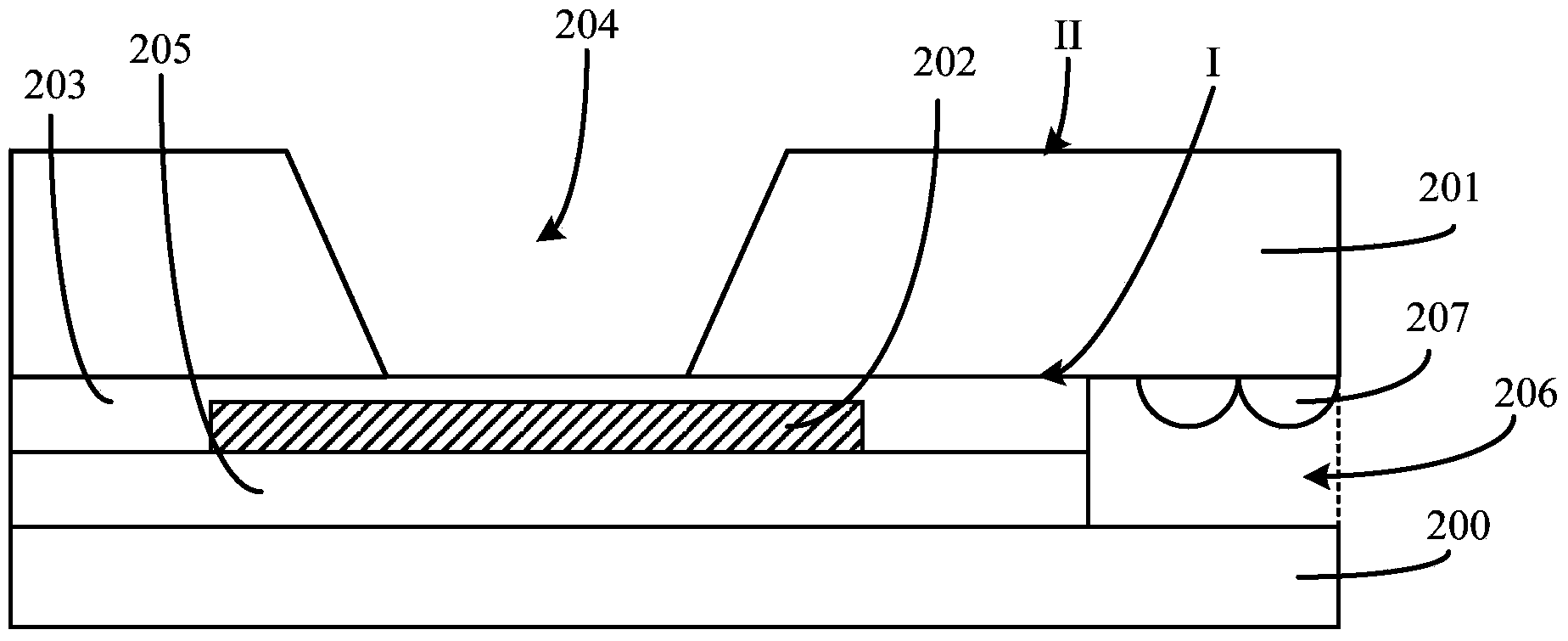

[0043] Figure 3 to Figure 8 is a schematic cross-sectional structure diagram of the forming process of the package structure in the first embodiment of the present invention.

[0044] Please refer to image 3 , providing a chip layer 201, the first surface 1 of the chip layer 201 has a protection layer 203, the surface of the protection layer 203 has a pad layer 202, the surface of the protection layer 203 and the pad layer 202 has a substrate 200, the The second surface II of the chip layer 201 has several grooves 204 exposing the protective layer 203, the second surface II of the chip layer 201 is opposite to the first surface I, and the position of the grooves 204 is the same as that of the pad layer 202. correspond.

[0045] The chip layer 201 is a substrate on which semiconductor devices are formed, and the substrate is a silicon substrate, a silicon-germanium substrate, a silicon carbide substrate, a silicon-on-insulator substrate, a germanium-on-insulator substrate, ...

no. 2 example

[0084] Figure 9 is a schematic cross-sectional structure diagram during the formation process of the package structure of the second embodiment of the present invention.

[0085] In the first embodiment Figure 5 Based on that, please continue to refer to Figure 9 , using a plasma etching process to remove part of the first insulating layer 208 around the through hole 209 (such as Figure 5 shown) and protection layer 203 (as Figure 5 As shown), the first insulating layer 208b and the protective layer 203b are formed, and part of the pad layer 202 at the bottom of the trench 204 is exposed, so that the thickness of the first insulating layer 208b and the protective layer 203b becomes thinner as it gets closer to the through hole 209 , and the surface of the passivation layer 203 b at the bottom of the trench 204 is inclined relative to the surface of the pad layer 202 .

[0086] The process of removing part of the first insulating layer 208 and the protective layer 203 ...

no. 3 example

[0100] Figure 10 is a schematic cross-sectional structure diagram during the formation process of the packaging structure of the third embodiment of the present invention.

[0101] In the first embodiment Figure 6 Based on that, please continue to refer to Figure 10 , using the plasma dry deglue process to remove part of the first insulating layer 208 around the through hole 209 (such as Figure 5 After that, part of the first insulating layer 208 and the protective layer 209 around the through hole 209 are removed by plasma etching process, forming the first insulating layer 208c and the protective layer 209c, and exposing the part of the bottom of the trench 204 For the pad layer 202 , the protection layer 209 c becomes thinner as it gets closer to the through hole 209 , and the surface of the protection layer 209 c at the bottom of the trench 204 is inclined relative to the surface of the pad layer 202 .

[0102] In this embodiment, first, a part of the first insulati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More