Silicide Formation Method

A technology of silicide and chemical vapor deposition, which is applied in the manufacture of electrical components, semiconductor/solid-state devices, circuits, etc., can solve the problems of increased contact resistance and sheet resistance, decreased operating speed of semiconductor devices, and small contact areas, etc., to achieve uniform width , improve performance, uniform deposition thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

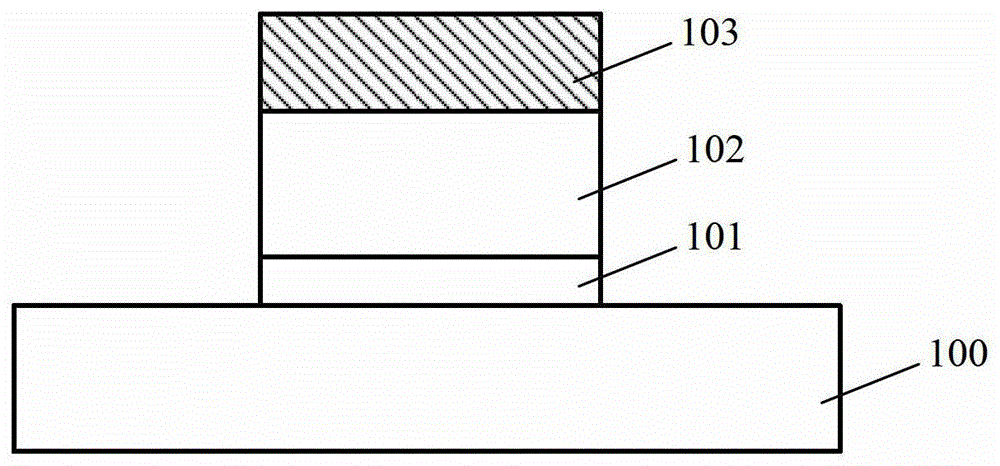

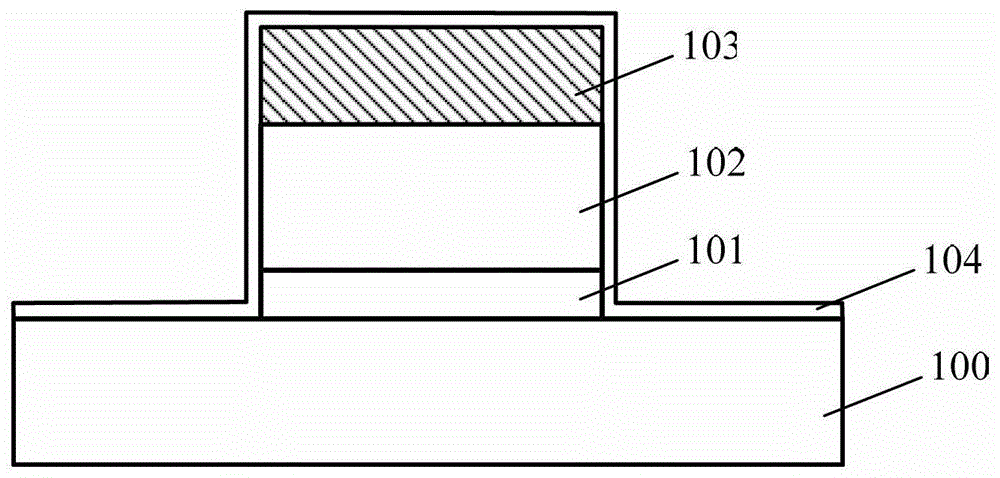

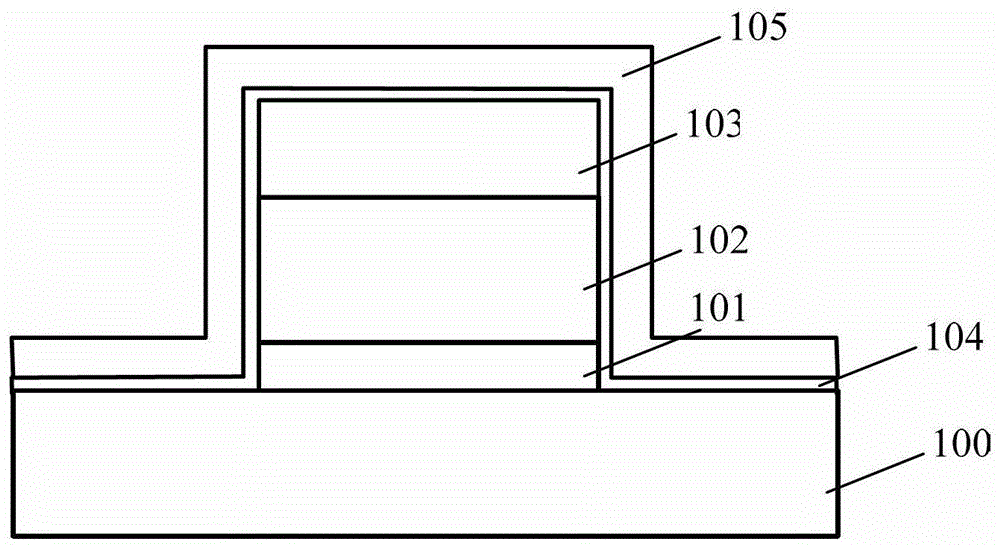

[0031] As described in the background art, in the prior art, forming silicide on the gate electrode layer can reduce the resistance of the gate electrode to a certain extent, but as the size of the gate electrode layer is further reduced, the resistance of the gate electrode layer further increases.

[0032] It was found that the gate electrode layer resistance increases with decreasing device size as the gate length becomes shorter and narrower gate lines have higher sheet resistance than wider gate lines due to edge effects. And increasing the surface area of the gate electrode layer can reduce the resistance of the gate electrode layer.

[0033] To this end, embodiments of the present invention disclose a method for forming a silicide. The method for forming a silicide increases the area of a gate electrode layer, and then forms a silicide layer on this basis, thereby effectively reducing the resistance of the gate electrode layer. .

[0034] The technical solutions of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com