A Programmable Interconnect Network Based on Programmable Cell Configuration

A technology of programming units and interconnection lines, applied to logic circuits using basic logic circuit components, logic circuits using specific components, etc., can solve the problems of easy loss or serial modification of configuration data, low data security and reliability, and data retention Time is not long and other problems, to achieve the effect of strong anti-radiation and anti-interference ability, easy encryption, high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] Reference symbol marks:

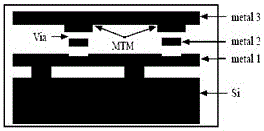

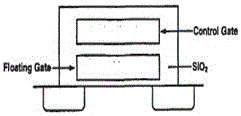

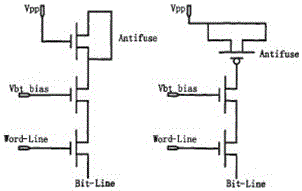

[0035] Figure 4 It shows the programmable interconnection network based on the programmable unit configuration provided by the present invention, the programmable interconnection network includes various types of interconnections, switch boxes, connection boxes and several programmable logic blocks. The signal connection between the programmable logic blocks is realized through the interconnection wire, the switch box and the connection box. The programming unit stores configuration data for the interconnect network. It can be realized based on a standard CMOS process without special process support. Strong anti-radiation and anti-interference ability, no soft error will occur when it is disturbed by external environments such as ultraviolet light, high-energy particles, microwaves, etc., will not cause data loss, and the data reliability is very good; the gate oxide breakdown type in the interconnection structure The anti-fuse unit has...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More