Polycrystalline-ferroelectric-film-based ferroelectric resistive random access memory

A ferro-resistance change and polycrystalline iron technology, applied in the field of information storage, can solve problems such as small switch resistance, insufficient reliability of memory data retention and fatigue resistance, large data fluctuations, etc., to reduce drift and diffusion, reduce Defects and their control difficulty, the effect of inhibiting the diffusion of elements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

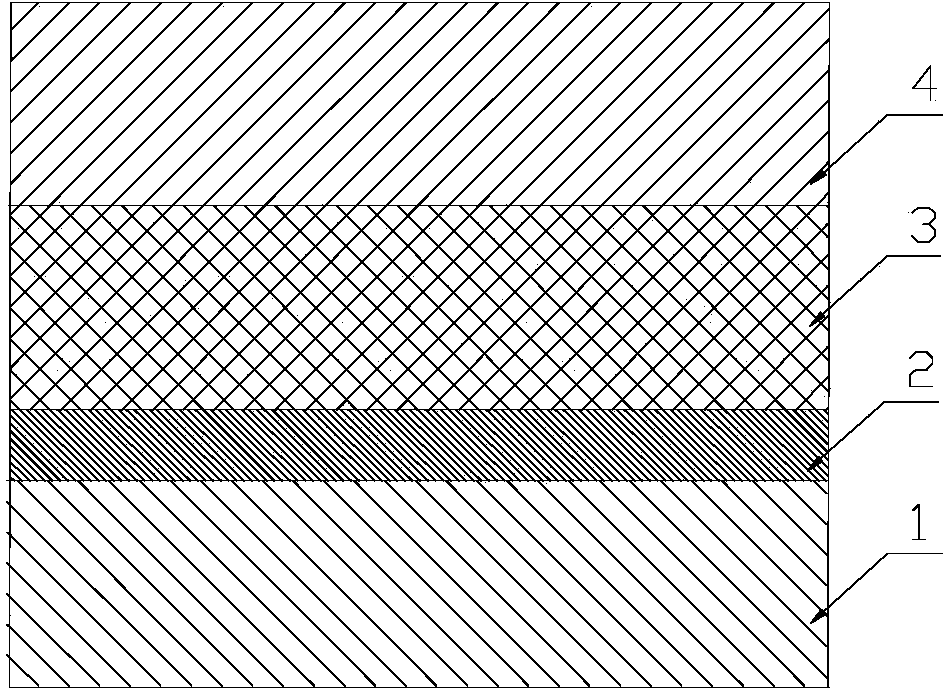

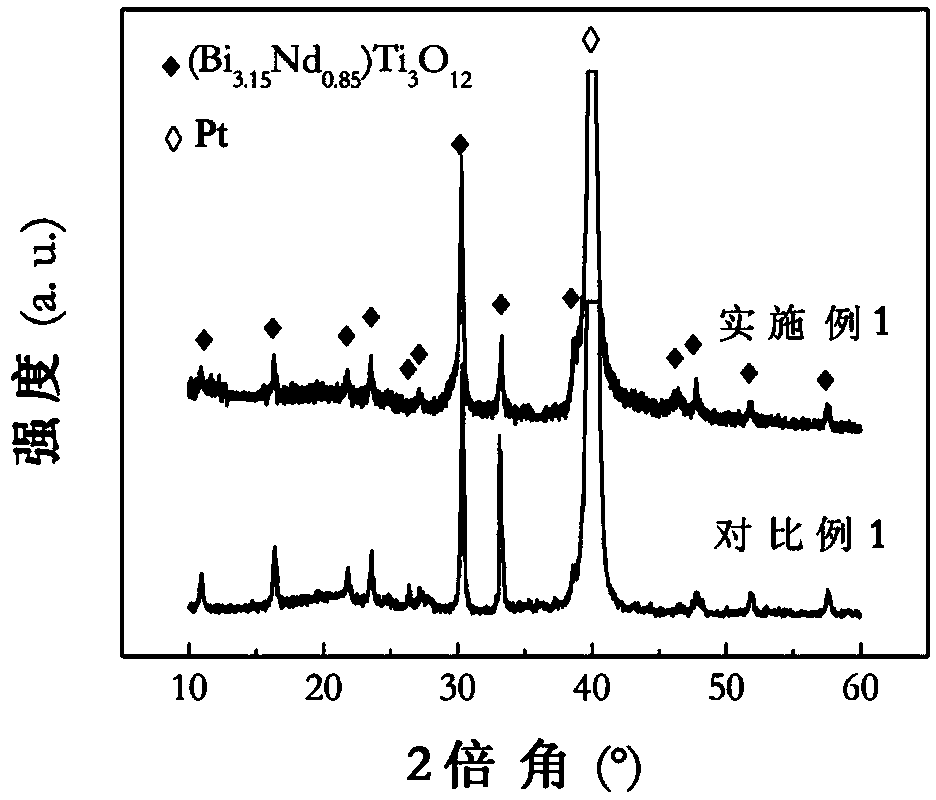

[0033] Preparation of "Pt / (Bi 3.15 Nd 0.85 ) Ti 3 o 12 / HfO 2 / Pt / Ti / SiO 2 / Si substrate" storage unit, the specific preparation process is as follows:

[0034] [1] In growing SiO 2 The single crystal Si substrate (i.e. SiO 2 / Si substrate) to grow the Pt bottom electrode layer. For enhanced Pt bottom electrode and SiO 2 / Si substrate adhesion, under Pt bottom electrode and SiO 2 A 10-20nm Ti adhesion layer is grown between the / Si substrates.

[0035] [2] Growth of HfO on the Pt lower electrode layer2 Defect control layer.

[0036] [3] In HfO 2 Growth on the defect-regulating layer (Bi 3.15 Nd 0.85 ) Ti 3 o 12 Polycrystalline ferroelectric thin film layer.

[0037] [4] in (Bi 3.15 Nd 0.85 ) Ti 3 o 12 A Pt upper electrode layer is grown on the polycrystalline ferroelectric thin film layer.

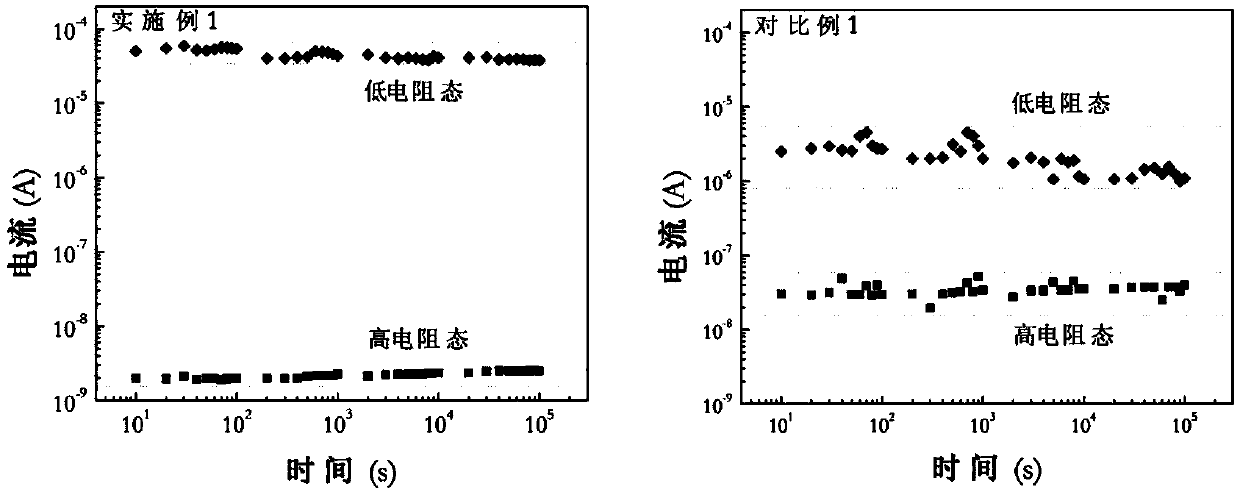

[0038] The thicknesses of the Pt lower electrode layer 1 and the Pt upper electrode layer 4 are 150 and 100 nm, respectively. The Pt upper electrode is a dot electrod...

Embodiment 2

[0043] In order to illustrate the beneficial effect of the defect control layer between the polycrystalline ferroelectric thin film layer and the upper electrode layer, a "Pt / HfO 2 / (Bi 3.15 Nd 0.85 ) Ti 3 o 12 / Pt / Ti / SiO 2 / Si substrate" memory cell. Except for the HfO 2 layer placed on the Pt upper electrode layer and (Bi 3.15 Nd 0.85 ) Ti 3 o 12 Except for the polycrystalline ferroelectric thin film layer, the others are consistent with the embodiment 1.

[0044] "Pt / HfO 2 / (Bi 3.15 Nd 0.85 ) Ti 3 o 12 / Pt / Ti / SiO 2 / Si substrate "memory cell memory characteristics similar to embodiment 1, high and low resistance ratio higher than 10 4 ; data hold 10 5 After s, the high and low resistance ratio is still 10 4 left and right; cycle 10 4 After the second time, the high and low resistance ratio is still 10 4 around; the fluctuation of the stored data is small, and the high resistance state current is 9.5×10 -10 ~5.9×10 -9 A, low resistance state current is 1...

Embodiment 3

[0046] In order to illustrate the beneficial effect of having a defect control layer between the lower electrode layer and the polycrystalline ferroelectric thin film layer or between the polycrystalline ferroelectric thin film layer and the upper electrode layer, a "Pt / HfO 2 / (Bi 3.15 Nd 0.85 ) Ti 3 o 12 / HfO 2 / Pt / Ti / SiO 2 / Si substrate "memory cell. Its preparation process except the Pt upper electrode layer and (Bi 3.15 Nd 0.85 ) Ti 3 o 12 Polycrystalline ferroelectric thin film layer has one more step to prepare HfO 2 Except for the defect control layer, the others are the same as those in Example 1. The preparation method, process parameters and the thickness of each layer are consistent with Example 1.

[0047] "Pt / HfO 2 / (Bi 3.15 Nd 0.85 ) Ti 3 o 12 / HfO 2 / Pt / Ti / SiO 2 / Si substrate" memory cells have a high-to-low resistance ratio higher than 10 4 ; data hold 10 5 After s, the high and low resistance ratio is still 10 4 left and right; cycle 10 4 ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More