SiC MOS (metal oxide semiconductor) capacitor and manufacturing method

A manufacturing method and capacitor technology, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve the problems of large gate leakage current and cannot effectively reduce the interface state density of the device, so as to reduce the gate leakage current and improve the The effect of withstand voltage and reliability improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

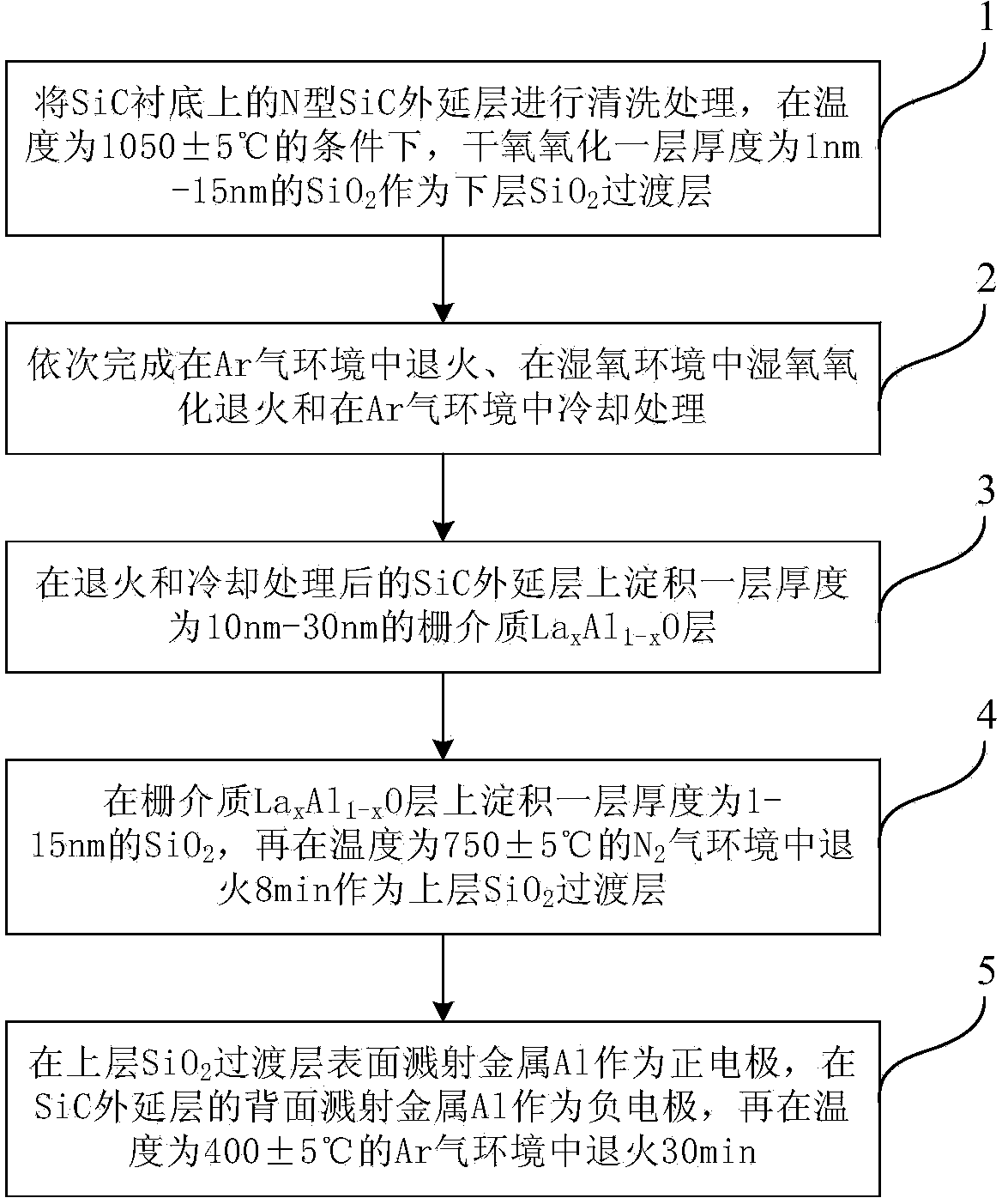

[0028] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

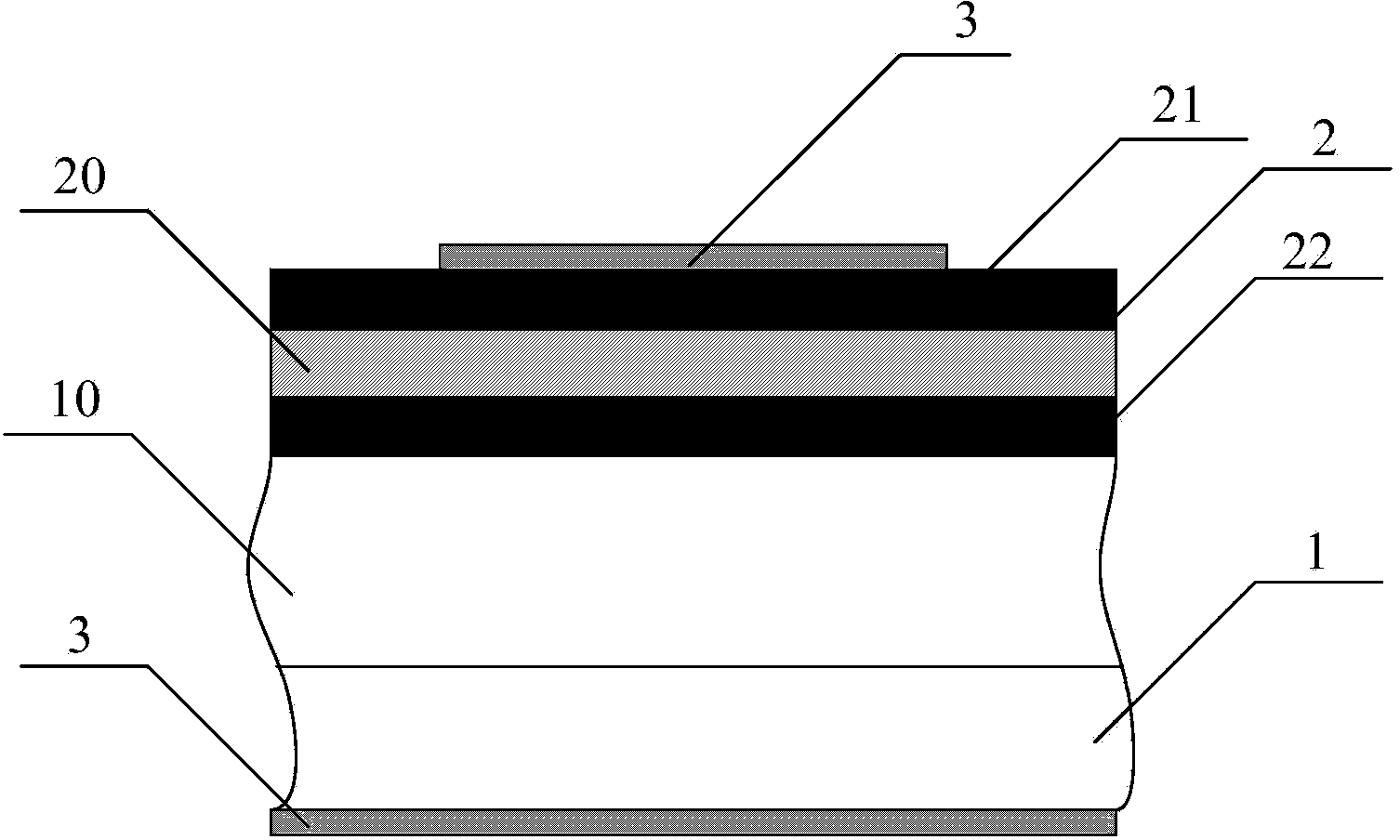

[0029] figure 1 It is a schematic diagram of a SiC MOS capacitor of the present invention. As shown in the figure, the present invention includes: a SiC substrate 1 , a gate dielectric layer 2 and positive and negative electrodes 3 .

[0030] Specifically, a SiC extension layer 10 is provided on the SiC substrate layer 1;

[0031] The gate dielectric layer 2 includes an upper layer of SiO 2 Transition layer 21, La x al 1-x O layer 20 and the underlying SiO 2 Transition layer 22; SiC epitaxial layer 10 is provided with lower layer SiO 2 Transition layer 22, lower layer SiO 2 The transition layer 22 is provided with La x al 1-x O layer 20, La x al 1-x O layer 20 is provided with upper layer SiO 2 Transition layer 21.

[0032] The positive and negative electrodes 3 are respectively connected with the upper lay...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Doping concentration | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More