Polysilicon resistor integration production method in silicon-germanium HBT (Heterojunction Bipolar Transistor) process

A technology of polysilicon resistors and manufacturing methods, which is applied in the direction of resistors, circuits, electrical components, etc., can solve problems affecting the uniformity of polysilicon resistance, base polysilicon residues, defects, etc., to reduce the possibility of polysilicon residues, prevent damage or The effect of falling off and increasing the slope

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

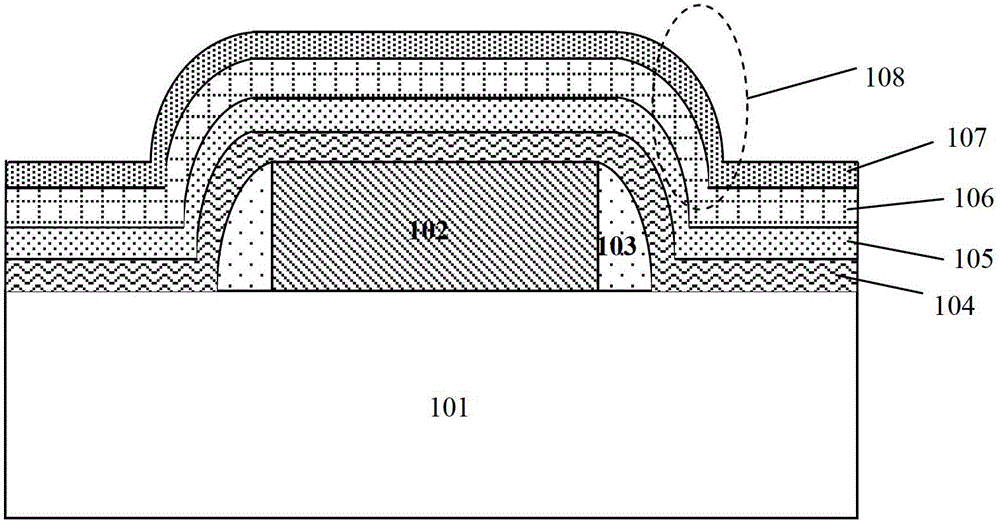

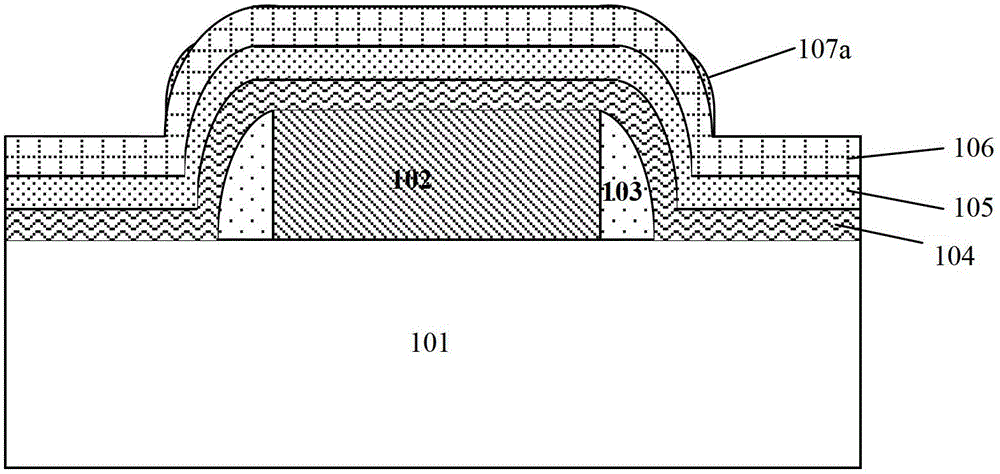

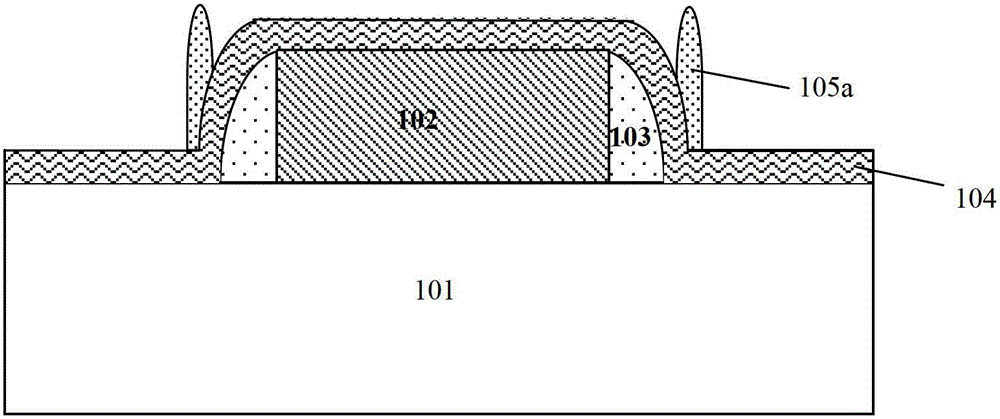

[0036] like figure 2 Shown is the flow chart of the method of the embodiment of the present invention; Figure 3A to Figure 3E Shown is a schematic diagram of the device structure in each step of the method of the embodiment of the present invention. The polysilicon resistance integrated manufacturing method in the silicon germanium HBT process of the embodiment of the present invention is used to realize the integrated production of the polysilicon resistance 2 and the silicon germanium HBT, including the following steps:

[0037] Step 1, such as Figure 3A As shown, a silicon substrate with a field oxygen 1 isolation structure is provided, and an active region of the silicon substrate is isolated by the field oxygen 1 . The field oxygen 1 is local field oxygen (LOCOS) or shallow trench oxygen (STI). Figure 3A The structure diagram of the formation region of the polysilicon resistor 2 is only shown in the figure, and the structure diagram of the formation region of the sil...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com