IGBT chip and preparation method thereof

A chip and control area technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of increased difficulty in IGBT device design, achieve the effects of shortening extraction time, increasing switching speed, and alleviating conflicting relationships

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

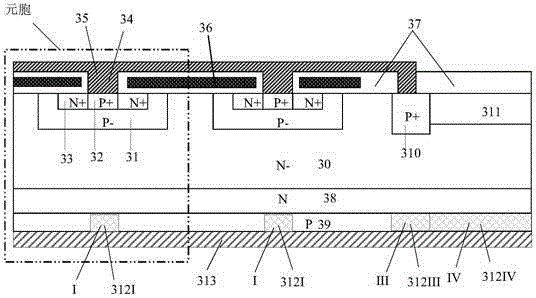

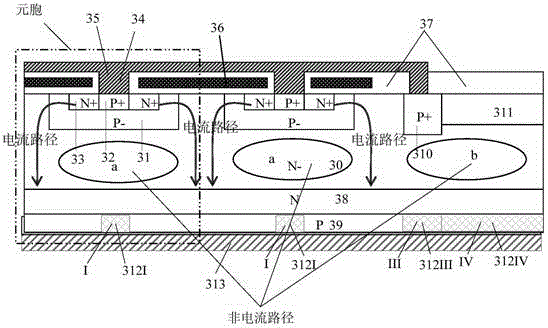

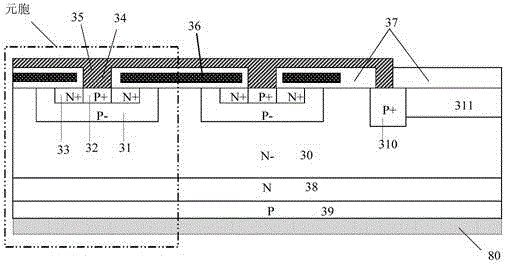

[0051] It should be noted that the structure of the IGBT chip provided by the present invention is based on the existing IGBT chip structure with a local minority carrier injection efficiency control area added. Therefore, the structure of the IGBT chip provided by the present invention is basically the same as that of the existing IGBT chip. The IGBT chip described in the embodiment of the present invention may have a planar gate structure or a trench gate structure, and the embodiment of the present invention takes the IGBT chip with a planar gate structure as an example for illustration. The specific structure of the IGBT chip with a planar gate structure is as follows: figure 2 with image 3 shown. figure 2 is a schematic top view structure diagram of an IGBT chip according to an embodiment of the present invention, image 3 is a sch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More