Low-power-consumption 12-bit assembly line successive approximation analog-digital converter

An analog-to-digital converter, successive approximation technology, applied in the direction of analog/digital conversion, code conversion, instruments, etc., can solve the problems of 128 times amplifier difficulty, circuit power consumption can not be effectively reduced, high output accuracy, etc., to achieve Break through the performance bottleneck, reduce the output range, and improve the overall performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

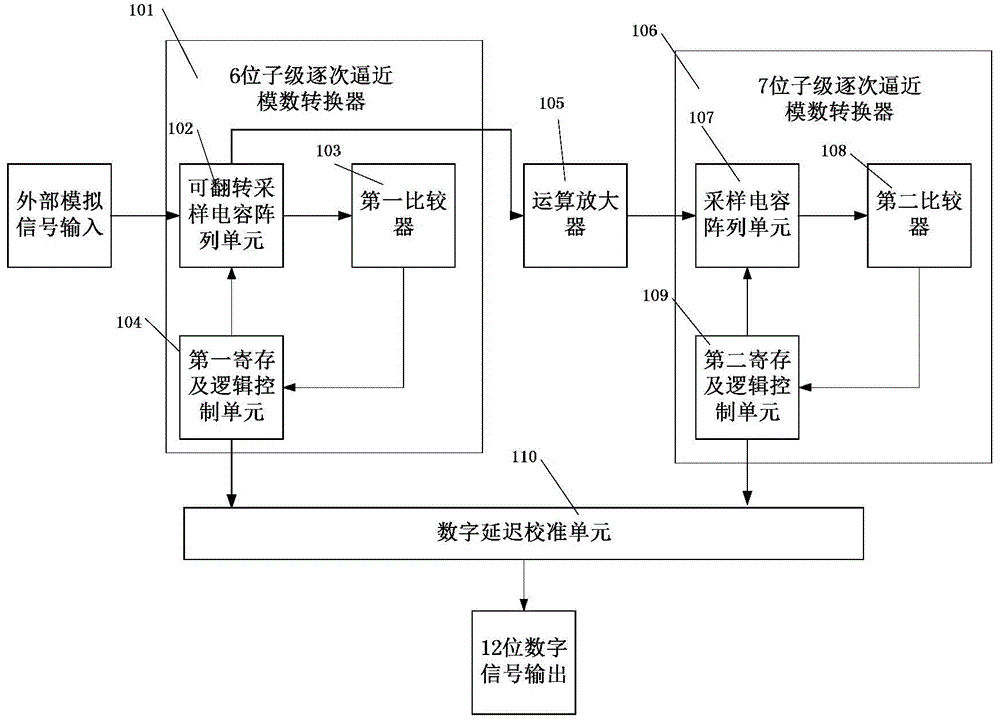

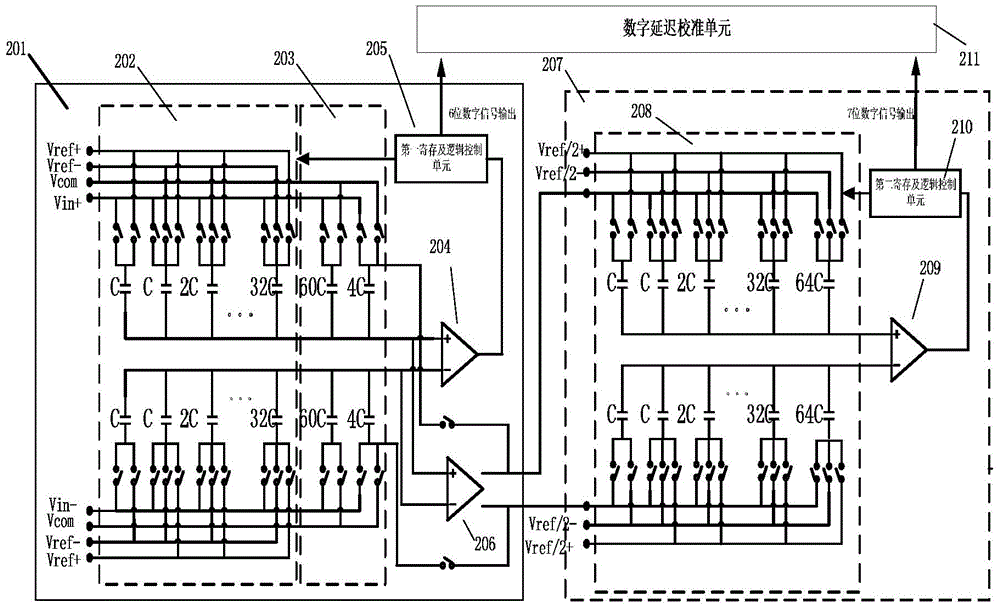

[0026] refer to figure 1 , a low-power 12-bit pipelined successive approximation analog-to-digital converter of the present invention, comprising a 6-bit sub-level successive approximation analog-to-digital converter 101, an operational amplifier 105, a 7-bit sub-level successive approximation analog-to-digital converter 106 and a digital delay calibration unit 110, the residual signal output of the 6-bit sub-stage successive approximation analog-to-digital converter 101 is connected to the input terminal of the operational amplifier 105, and the digital signal of the 6-bit sub-stage successive approximation analog-to-digital converter 101 is output to the digital delay calibration unit 110 The high six-bit input terminal of the operational amplifier 105 is connected to the input terminal of the 7-bit sub-stage successive approximation analog-to-digital converter 106, and the digital signal output of the 7-bit sub-stage successive approximation analog-to-digital converter 106 i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More