Semiconductor device formation method

A semiconductor and device technology, applied in the field of semiconductor device formation, can solve problems such as poor performance of NMOS metal transistors, and achieve the effect of improving performance and improving performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

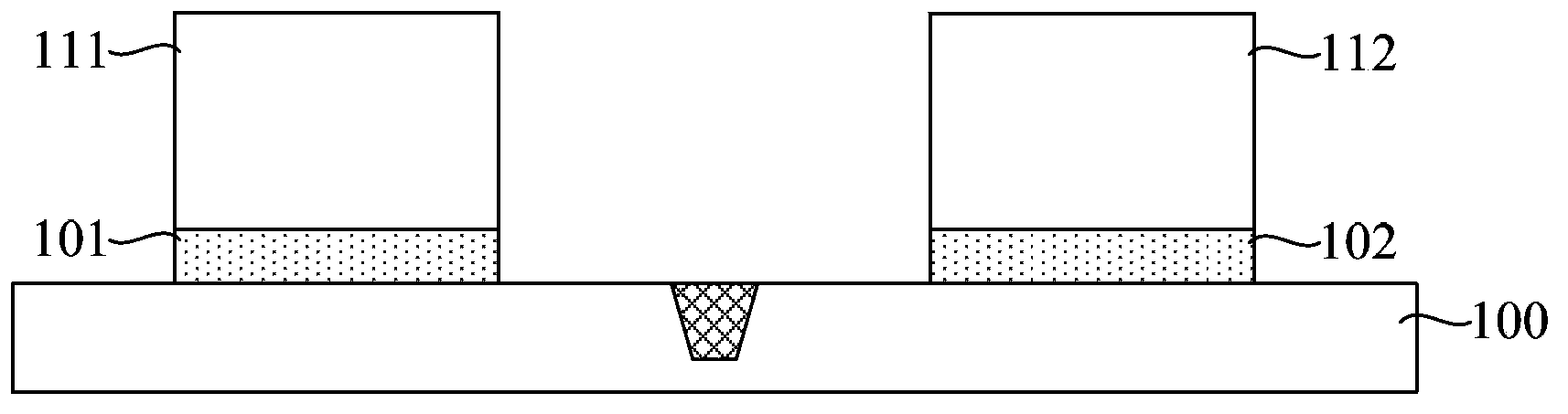

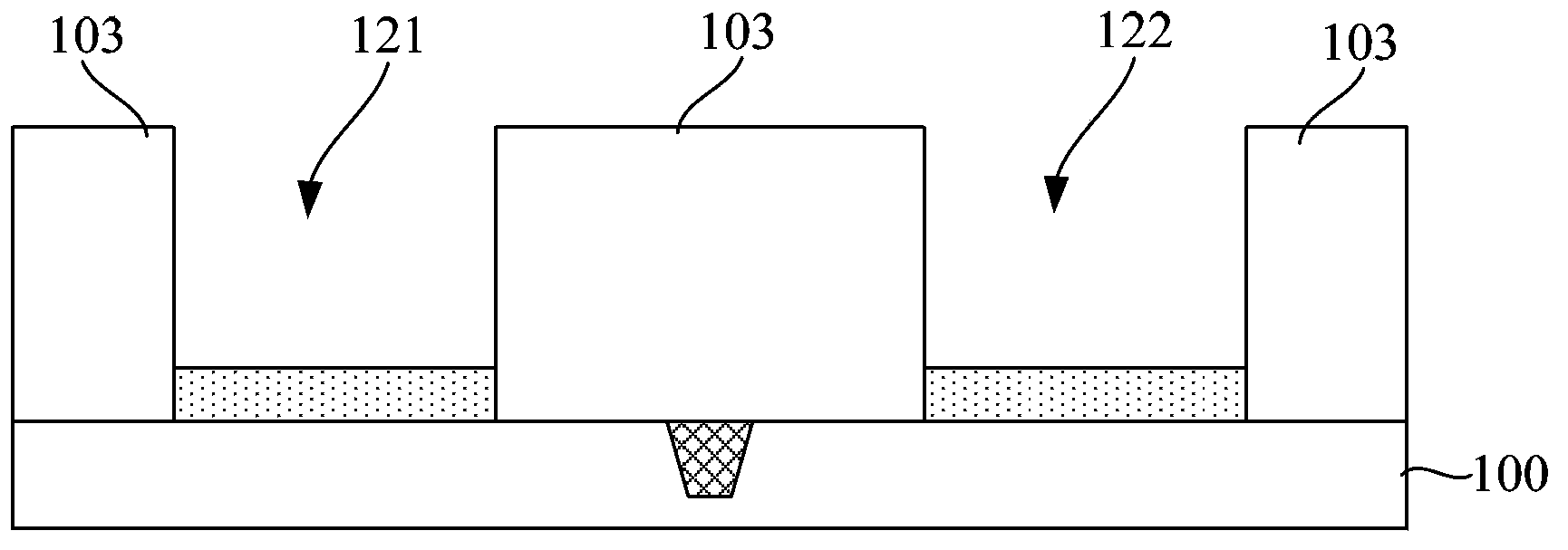

[0048] refer to Figure 4 , providing a substrate 300, the substrate 300 includes a first active region I and a second active region II, the types of the first active region I and the second active region II are opposite.

[0049] In this embodiment, the first active region I is a P-type active region, the second active region II is an N-type active region, and the first active region I and the second active region II are shallow trench isolation structure (not numbered). A PMOS transistor is formed in the first active region I, and an NMOS transistor is formed in the second active region II.

[0050] In this embodiment, the substrate 300 is a silicon substrate, a germanium substrate, or a silicon-on-insulator substrate, etc.; or it may also include other materials, such as III-V group compounds such as gallium arsenide. Those skilled in the art can select the substrate according to the type of transistors formed on the substrate 300 , so the type of the substrate should not l...

no. 2 example

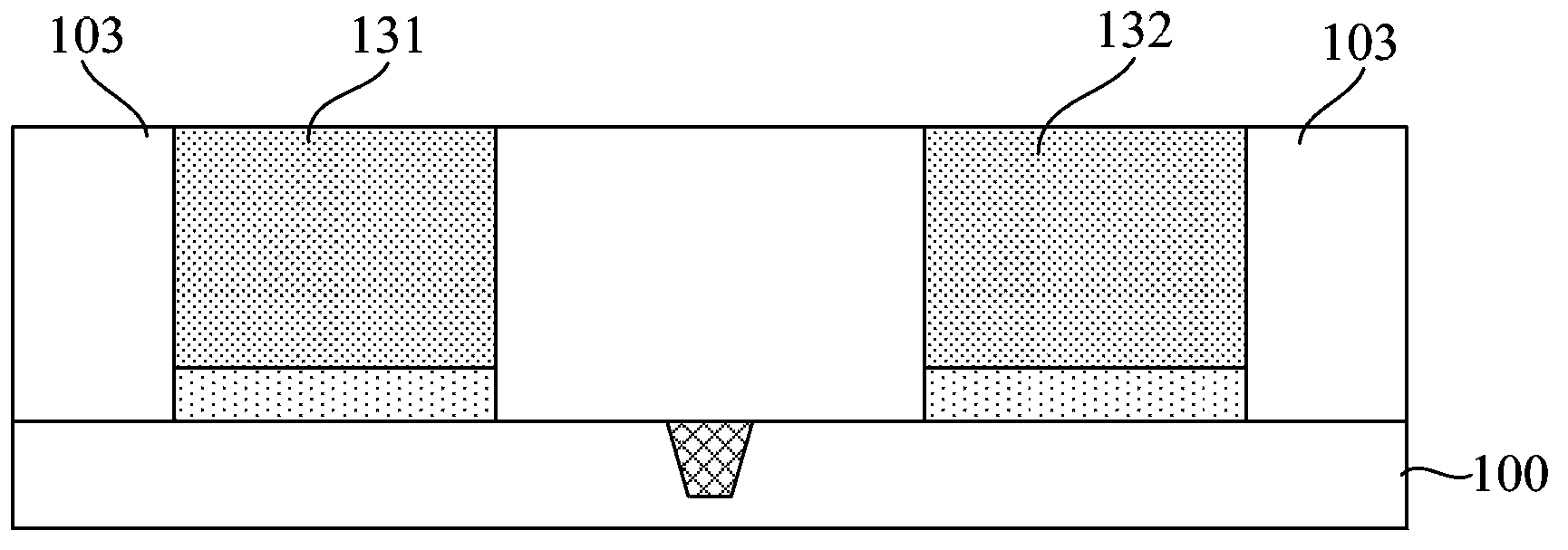

[0087] The difference between the second embodiment and the first embodiment is that after the interlayer dielectric layer is formed, the second dummy gate is removed to form a second dummy gate trench, and a second dummy gate trench is formed on the bottom and side walls of the second dummy gate trench. a third gate dielectric layer;

[0088] After forming the third gate dielectric layer, the first dummy gate is removed to form a first dummy gate trench.

[0089] In another embodiment, it may also be: removing the second dummy gate structure to form a second dummy gate trench;

[0090] After forming the second dummy gate trench, removing the first dummy gate to form the first dummy gate trench;

[0091] Afterwards, a third gate dielectric layer is formed on the sidewall and bottom of the second dummy gate trench.

[0092] Wherein, parameters such as the thickness of the first gate dielectric layer and the third gate dielectric layer, and the mass concentration of chromium c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More