Semiconductor contact hole etching method

A contact hole and semiconductor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of excessive lithography overlay deviation, affecting breakdown voltage and contact resistance, device failure, etc., to achieve etching Accurate, improve electrical performance, reduce loss effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments, but not as a limitation of the present invention.

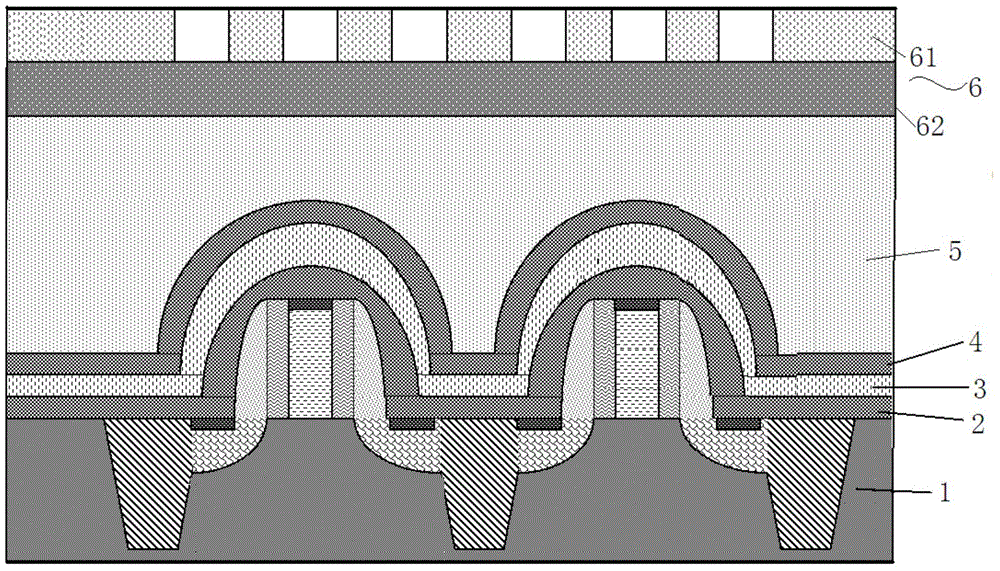

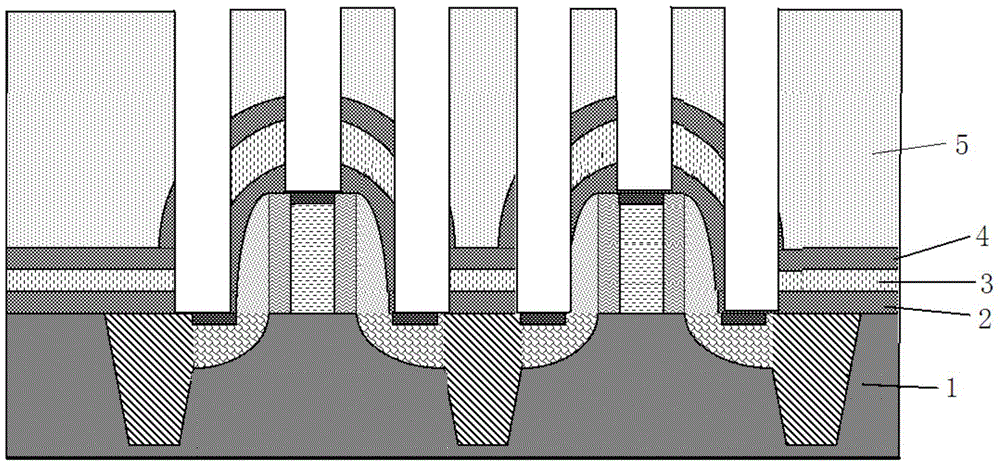

[0031] Such as figure 1 , 2 As shown, a semiconductor contact hole etching method is characterized in that: comprising the following steps

[0032] Step 1, providing a substrate 1 on which a plurality of conductive structures are formed. In the semiconductor field, the base 1 is a semiconductor substrate, on which gates and sidewalls are formed; AA (active area, active area) regions are defined in the substrate, and shallow trenches pass between adjacent AA regions. Isolation area (STI) for isolation,. A source and a drain are respectively formed in the substrate on both sides of the bottom of the gate, and metal silicon oxide is formed on the top of the gate and the top of the source / drain.

[0033] Step 2, forming a first SiN layer covering the substrate and the conductive structure on the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More