Embedded silicon substrate fan-out type packaging structure and manufacturing method thereof

A packaging structure, fan-out technology, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve problems such as high cost, complex structure and manufacturing process, and achieve low cost, small wiring line width, and improved The effect of heat dissipation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

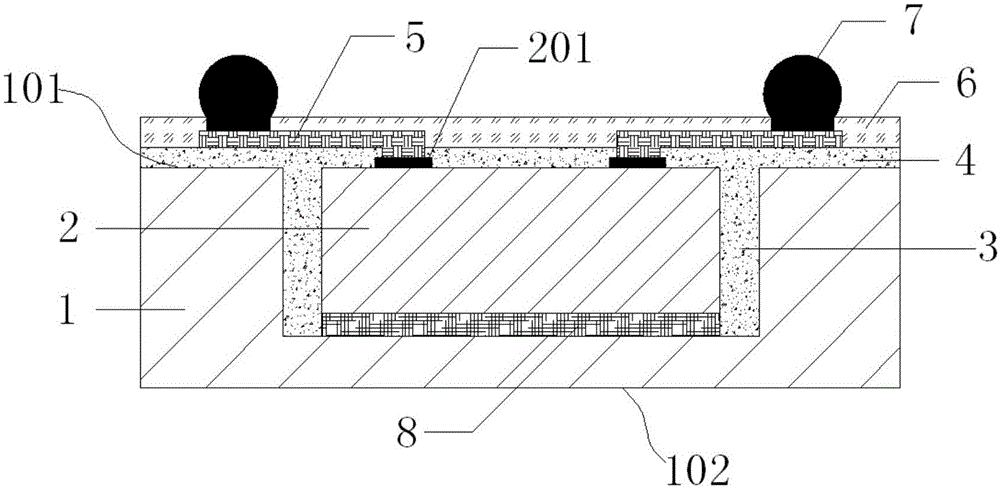

[0045] Such as figure 1 As shown, a fan-out packaging structure embedded in a silicon substrate includes a silicon substrate 1, the silicon substrate has a first surface 101 and a second surface 102 opposite to it, and a direction to the silicon substrate is formed on the first surface. The groove extending from the second surface is preferably a straight groove or an inclined groove with an angle between the side wall and the bottom surface of 80 degrees to 120 degrees, which is not limited here. The schematic diagram of this embodiment is in the shape of a straight groove. A chip 2 is placed in the groove, the pads of the chip face up, and the pads of the chip are close to the first surface; there is adhesion between the chip and the groove bottom of the groove. Layer 8, the chip is bonded to the bottom of the groove through the adhesive layer, which can better fix the chip and prevent the chip from shifting.

[0046] There is a gap between the chip and the sidewall of the...

Embodiment 2

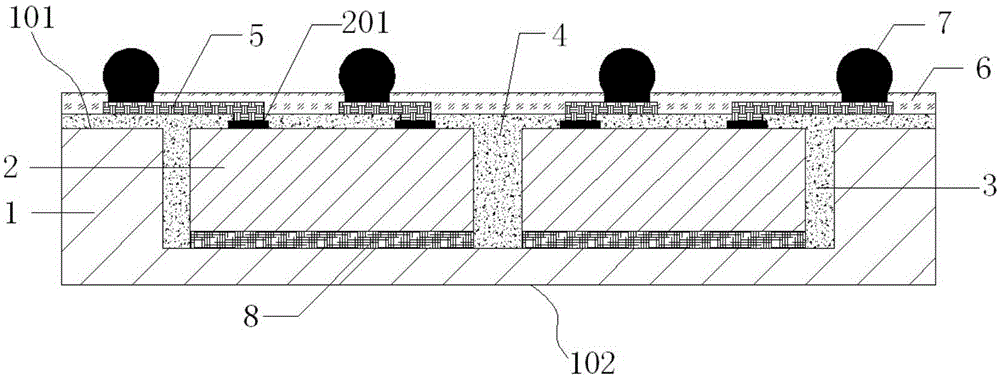

[0069] Such as figure 2 As shown, this embodiment 2 includes all the technical features of embodiment 1, the difference is that two chips 2 are embedded in a groove on the first surface of the silicon substrate, and the size and function of the two chips can be the same or different . This embodiment can expand the functionality of the package.

Embodiment 3

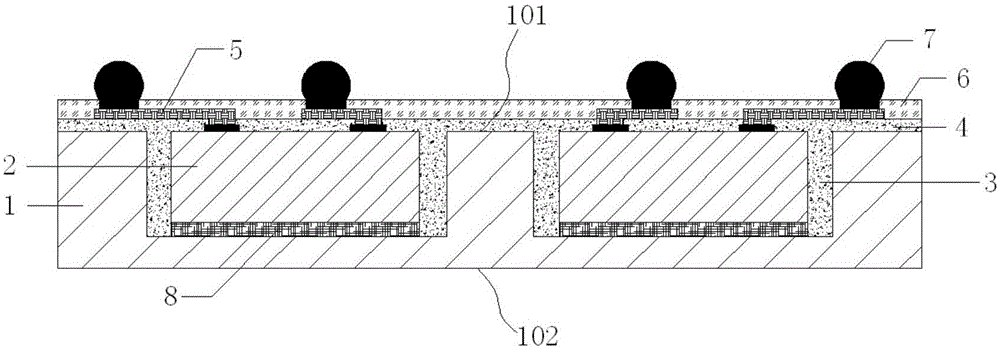

[0071] Such as image 3 As shown, this embodiment 3 includes all the technical features of embodiment 1, and the difference is that two grooves are formed on the first surface of the silicon substrate, and a chip 2 is respectively embedded in each groove, and the two chips The size and function can be the same or different. This embodiment can expand the function of the package body, and at the same time reduce the signal interference between the two chips.

[0072] The invention provides a fan-out packaging structure embedded in a silicon substrate and a manufacturing method thereof. A silicon substrate is used instead of a molding compound as a fan-out substrate, and the advantage of the silicon substrate is fully utilized to produce fine wiring. Utilizing the mature silicon etching process, structures such as holes and grooves can be precisely etched. By embedding the chip in the groove on the silicon substrate, the chip is bonded to the bottom of the groove through the a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More