Image sensor and manufacturing method thereof

A graphic sensor and manufacturing method technology, applied in the direction of electric solid-state devices, semiconductor devices, radiation control devices, etc., can solve the problems of reducing the performance of image sensors, reducing the fill factor of silicon photodiodes, and reducing device performance, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

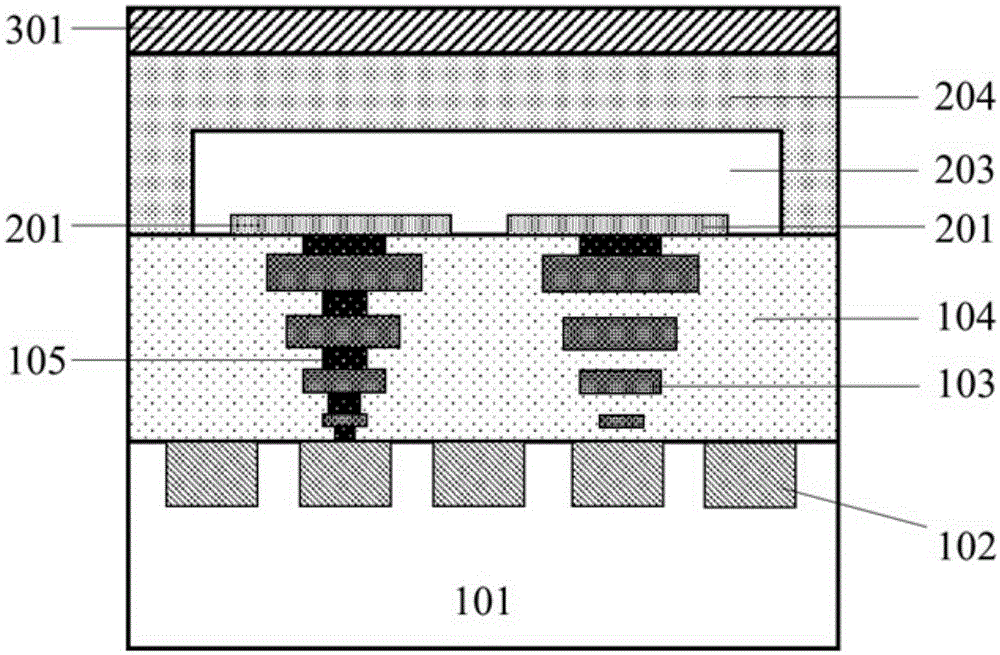

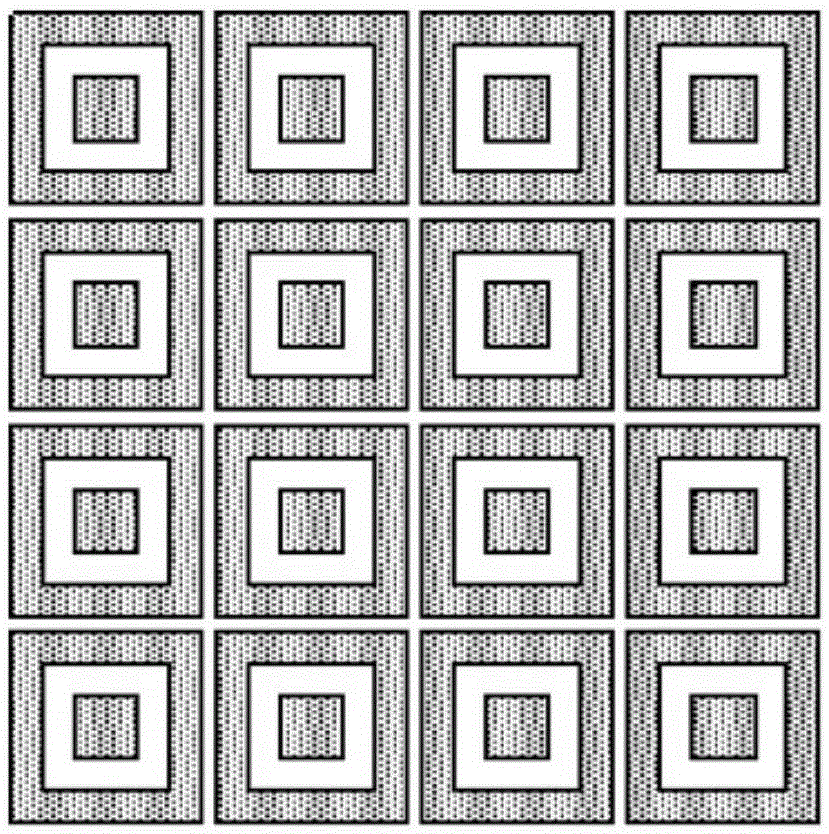

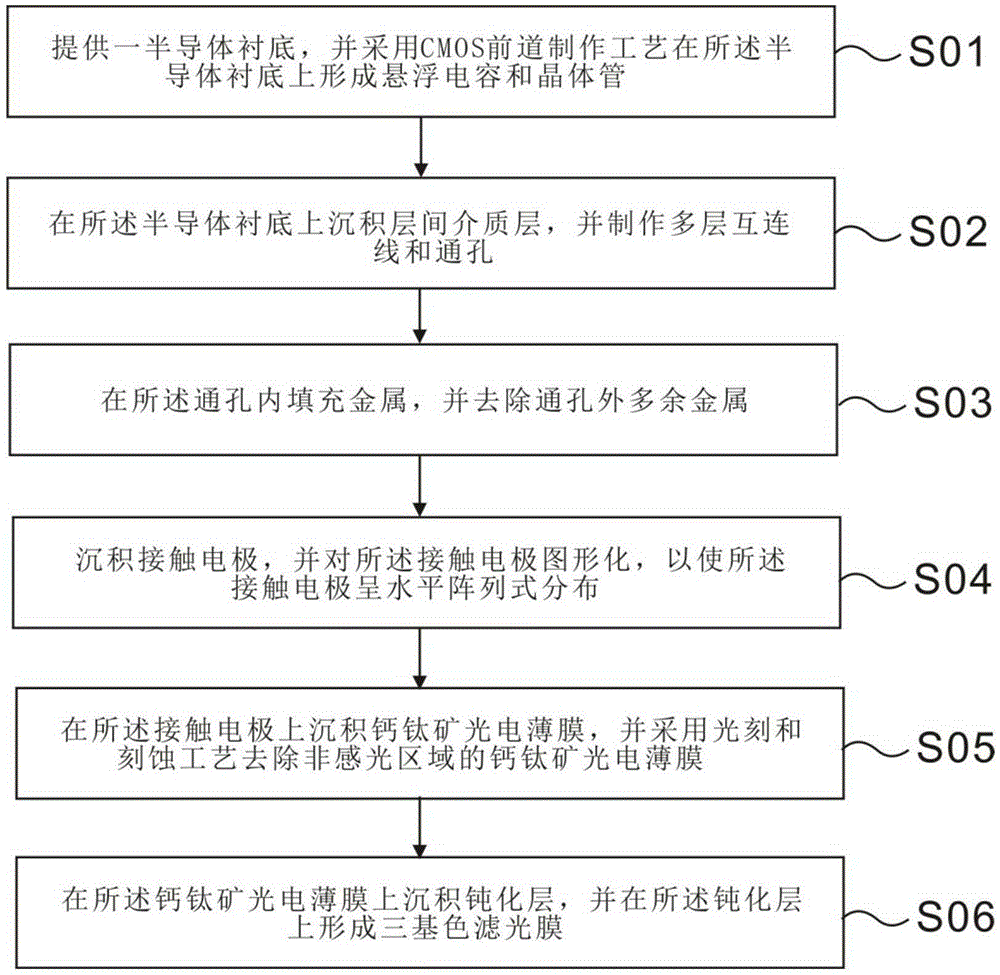

[0061] Such as figure 1 As shown, the present invention provides a kind of pattern sensor, and it comprises semiconductor substrate 101, interlayer dielectric layer 104, interconnection line 103, through hole 105, contact electrode 201, perovskite photoelectric thin film 203, passivation layer 204 and Three-color filter film 301, wherein the semiconductor substrate 101 has floating capacitors and transistors 102, the interlayer dielectric layer 104 is arranged on the upper surface of the semiconductor substrate 101, and the interlayer dielectric layer 104 has multi-layer interconnection lines 103 and 105 vias filled with metal, see figure 2 , the contact electrodes 201 are distributed in an array in the horizontal direction on the interlayer dielectric layer 104, and there is a preset width between adjacent contact electrodes, and the perovskite photoelectric thin film 203 covers the contact electrodes 201 to form In the photosensitive area of the image sensor, the passiva...

Embodiment 2

[0078] Such as Figure 4 As shown, the present invention provides a kind of image sensor, and it comprises semiconductor substrate 101, interlayer dielectric layer 104, multilayer interconnection line 103, first through hole 105, contact electrode 201, perovskite photoelectric thin film 203, medium Thin film layer 205, top electrode 202, passivation layer 204, and three primary color filter films 301; wherein, there are floating capacitors and transistors 102 on the semiconductor substrate 101, and the interlayer dielectric layer 104 is arranged on the upper surface of the semiconductor substrate 101, and The interlayer dielectric layer 104 has a multilayer interconnection line 103 and a first through hole 105 filled with metal, please refer to Figure 5 , the contact electrodes 201 are distributed in an array in the vertical direction on the interlayer dielectric layer, and there is a preset width between adjacent contact electrodes 201; the perovskite photoelectric thin film...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More