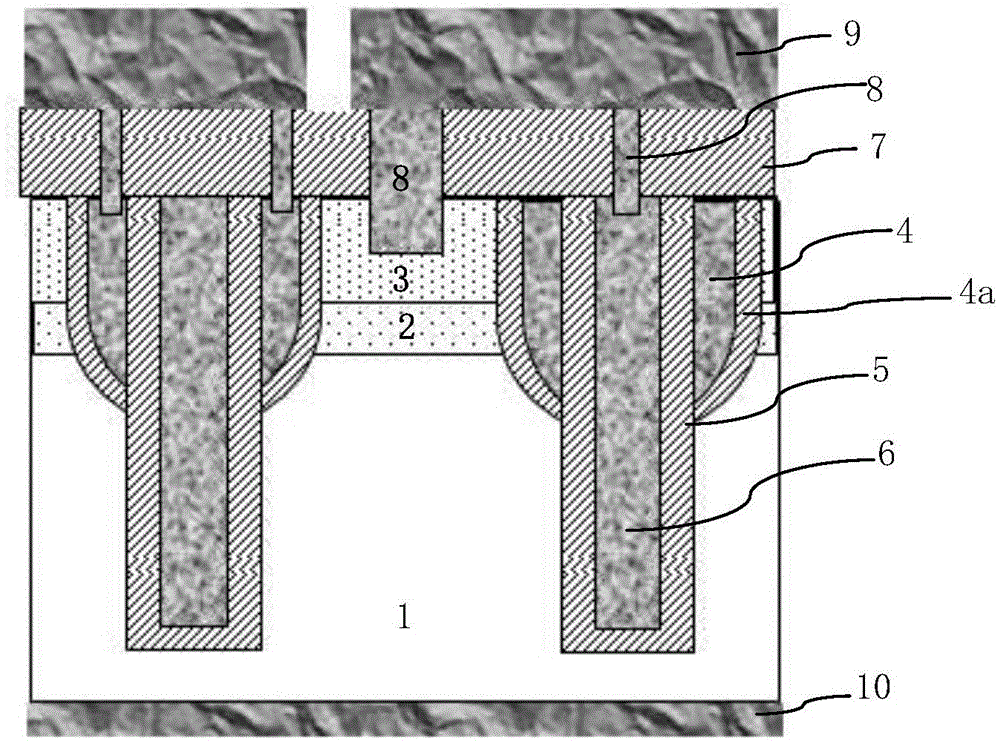

Manufacturing method for MOSFET adopting separated trench side gate structure with shield gate

A manufacturing method and shielding gate technology, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, circuits, etc., can solve the problems of large gate-source leakage, reduce gate resistance, and ineffective bonding, so as to eliminate gate-drain capacitance, Effect of reducing gate resistance and reducing parasitic resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

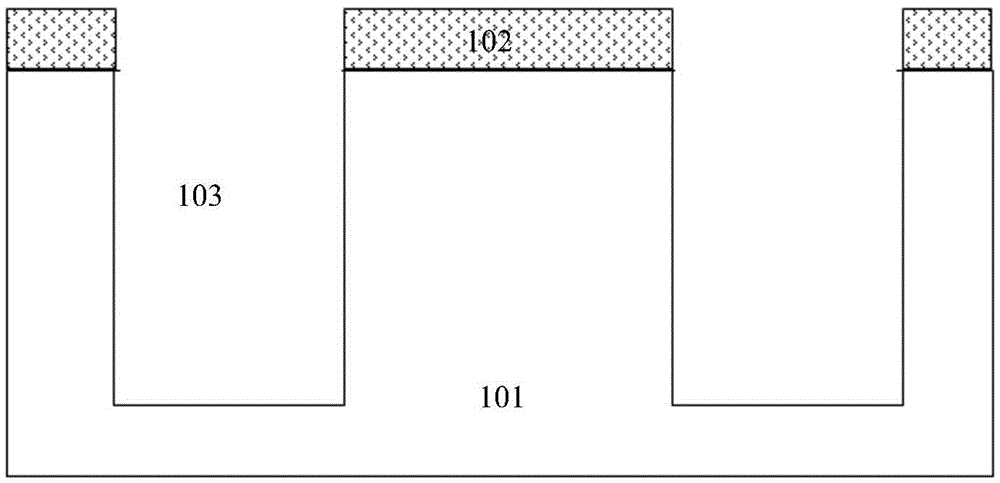

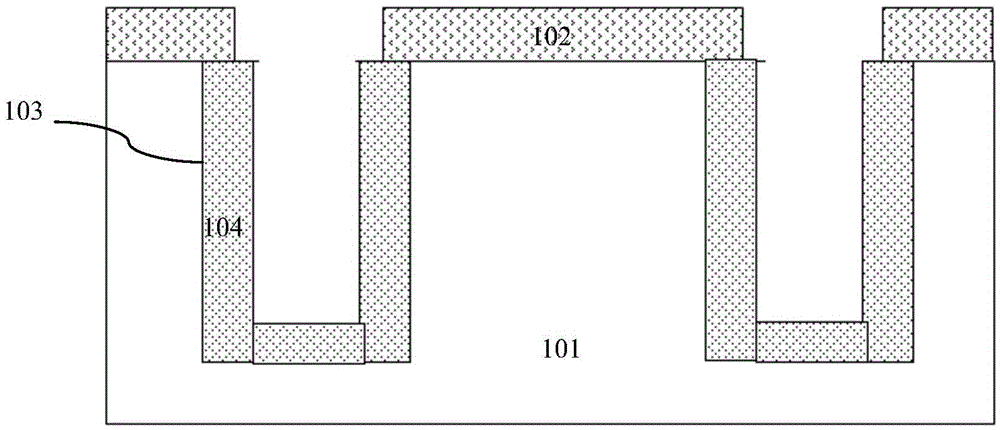

[0045] Such as figure 2 Shown is the flow chart of the method of the embodiment of the present invention; Figure 3A to Figure 3Q Shown is a schematic diagram of the device structure in each step of the method of the embodiment of the present invention. A method for manufacturing a trench-separated side-gate MOSFET with a shield gate in an embodiment of the present invention includes the following steps:

[0046] Step 1, such as Figure 3A As shown, a semiconductor substrate 1 is provided, and ion implantation is performed to form a well region 2 in the semiconductor substrate 1; heavily doped source implantation is performed to form a source region 3 on the surface of the well region 2; 2 and the source region 3 undergo a thermal annealing process. Preferably, the step of forming a shielding oxide layer 201 on the surface of the semiconductor substrate 1 is also included before the ion implantation of the well region 2 and the source region 3, and ions pass through the sh...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More