Circuit structure and manufacturing method thereof

A technology of circuit structure and manufacturing method, which is applied in the direction of circuit, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of delamination between the circuit layer 21 and the passivation layer 22, and yield reduction, so as to improve the delamination phenomenon, The effect of improving product yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

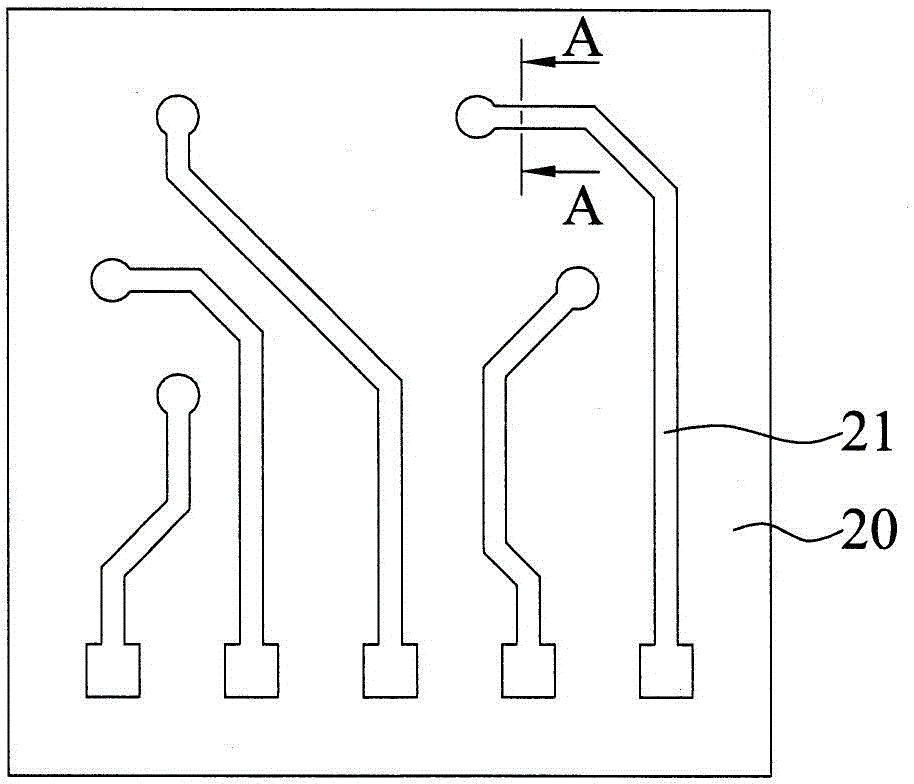

[0060] see Figure 2A and Figure 2D It is a schematic diagram showing the manufacturing method of the circuit structure 3 of the present invention.

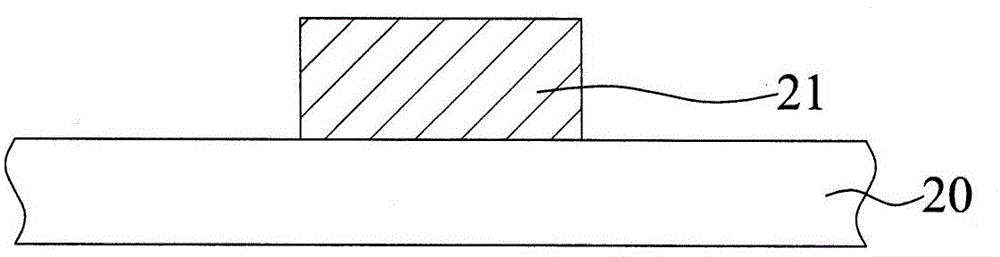

[0061] Such as Figure 2A As shown, a substrate 30 with a circuit layer 31 formed on the surface is provided, and the circuit layer 31 has a first surface 31a and a second surface 31b opposite to each other, and a side surface 31c connecting the first surface 31a and the second surface 31b, wherein , the circuit layer 31 contacts the substrate 30 through the second surface 31b.

[0062] In this embodiment, the substrate 30 is a circuit board, chip, wafer, redistribution structure or silicon interposer. In addition, the substrate may already have at least one circuit layer, and the circuit layer 31 refers to the circuit formed on the outermost layer of the substrate. Furthermore, the material forming the wiring layer 31 is copper.

[0063] Such as Figure 2B As shown, a first dielectric layer 32 is formed on the first surfa...

no. 2 example

[0068] Such as Figure 2D As shown, on the second dielectric layer 33 , a third dielectric layer 34 is formed by chemical vapor deposition, and the reflection index of the third dielectric layer 34 is smaller than the reflection index of the first dielectric layer 32 .

[0069] In this embodiment, the material forming the second dielectric layer is a general deposition rate (approximately ) deposited under silicon oxide, the material forming the third dielectric layer is a general deposition rate (approximately ) Silicon nitride deposited under.

[0070] see Figure 2C , the circuit structure of the present invention includes: a substrate 30; a circuit layer 31 formed on the surface of the substrate 30, the circuit layer 31 has an opposite first surface 31a and a second surface 31b, and connects the first surface 31a and the second surface The side 31c of the surface 31b, wherein the circuit layer 31 contacts the substrate 30 through the second surface 31b; the first diel...

no. 3 example

[0075] see image 3 Compared with the previous embodiment, in the circuit structure 4 of this embodiment, the first dielectric layer 32 is also only formed on the first surface 31a and the side surface 31c of the circuit layer 31, and is not formed on the substrate 30. On the surface, however, the second dielectric layer 33 is not only formed on the first dielectric layer 32, the second dielectric layer 33 also extends to cover the surface of the substrate 30 where the circuit layer 31 is not formed. , that is, the second dielectric layer 33 is formed on the surface of the substrate 30 . In this embodiment, the circuit structure 4 has a third dielectric layer 34 formed on the second dielectric layer 33 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More