Method to improve sonos memory read operation capability

A technology for reading operation and memory, which is applied in the field of improving SONOS memory reading operation ability, can solve problems such as adverse effects of SONOS transistor and transmission transistor current, adverse effects of circuit reading operation, and decline in reading operation ability, so as to improve reading Operation capability, good protection, effect of increasing read current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

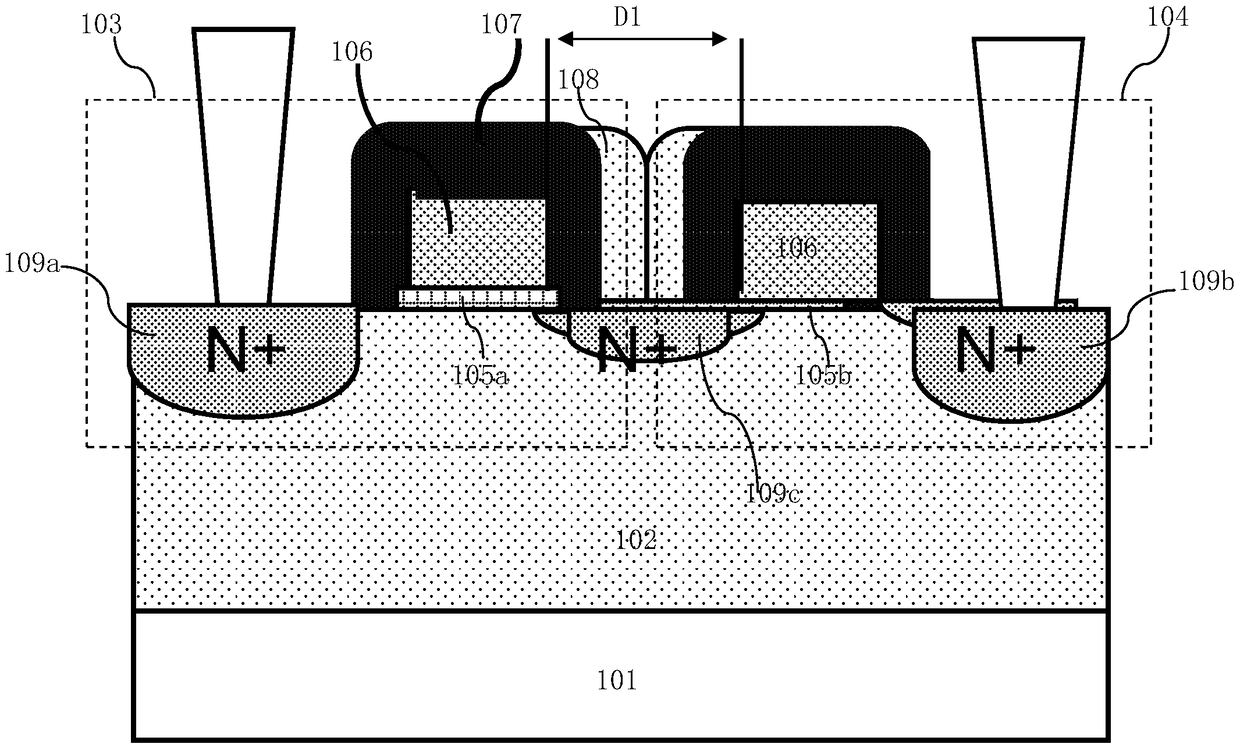

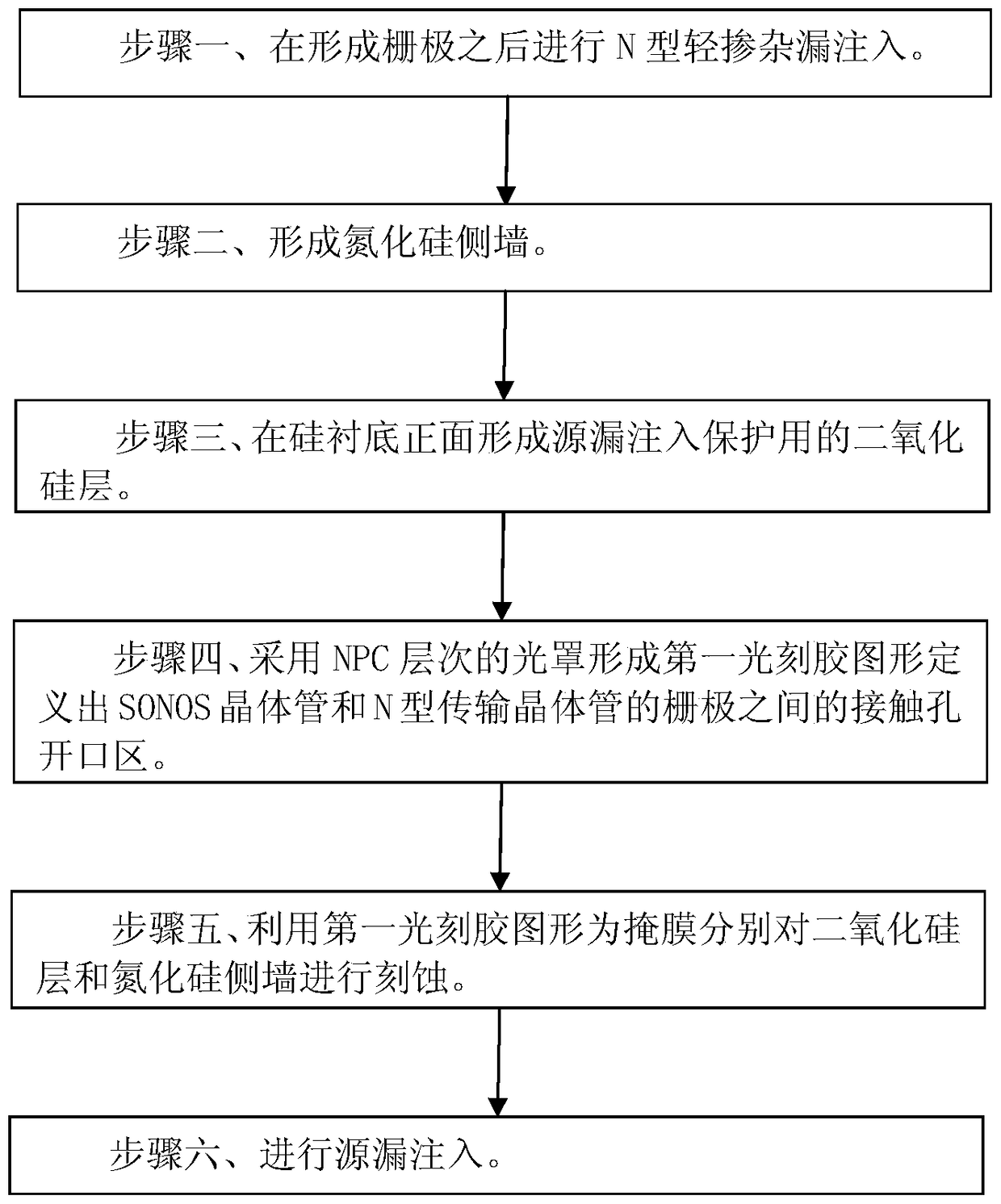

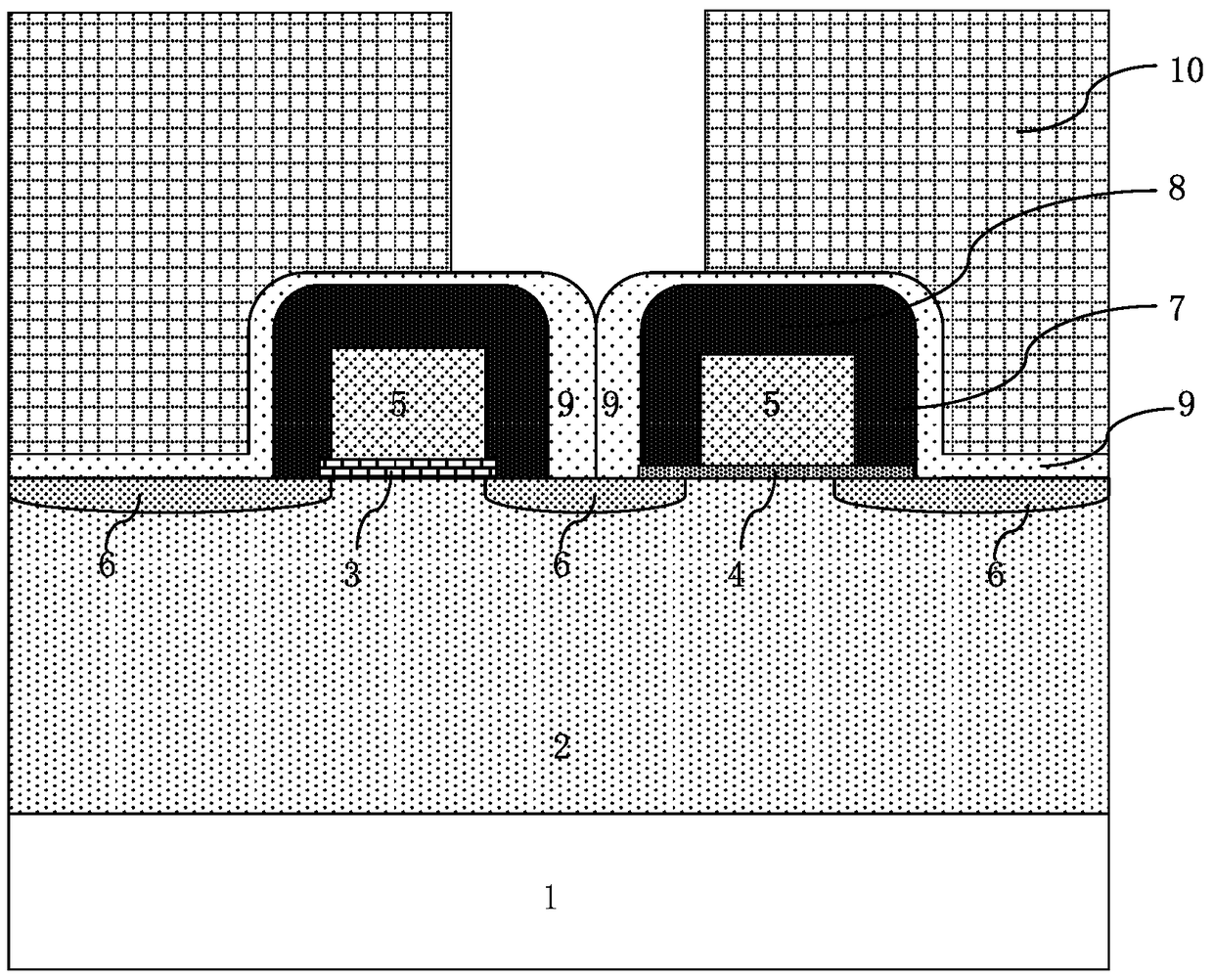

[0032] Such as figure 2 Shown is the flow chart of the method of the embodiment of the present invention; Figure 3A to Figure 3B Shown is a schematic diagram of the SONOS memory cell structure in each step of the method of the embodiment of the present invention. The cell structure of the SONOS memory of the method for improving the read operation capability of the SONOS memory in the embodiment of the present invention is composed of a SONOS transistor and an N-type transfer transistor, and the following steps are used to manufacture the cell structure of the SONOS memory:

[0033] Step 1, such as Figure 3A As shown, at first, forming the gate of the SONOS transistor and the N-type transfer transistor includes steps:

[0034] Step 11, forming a P well 2 on the silicon substrate 1, performing a turn-on voltage ion implantation in the P well 2 of the SONOS transistor region, and the formed turn-on ion implantation region is used to adjust the turn-on voltage of the SONOS tra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More