Formation method of CMOS (Complementary Metal Oxide Semiconductor) transistor

A technology of transistors and semiconductors, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of low selectivity of PMOS work function layer, affecting the quality of other material layers, and low etching rate of PMOS work function layer, etc. Achieve the effect of high etching selectivity, avoiding damage, and high etching efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

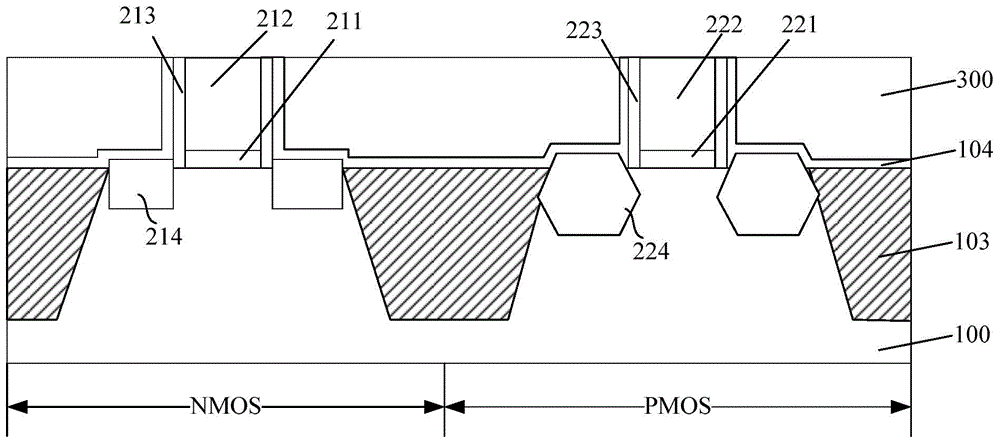

[0031] As mentioned in the background art, the performance of the CMOS transistors formed in the prior art needs to be further improved.

[0032] Currently, the material of the PMOS work function layer commonly used is TiN, and the material of the stop layer below the PMOS work function is generally TaN. The PMOS work function layer is usually removed by a wet etching process, and the etching solution used in the wet etching process is generally a mixed solution of ammonia and hydrogen peroxide (SC-1) or a mixed solution of hydrogen chloride and hydrogen peroxide ( SC-2), but the etching selectivity of the SC-1 solution for TiN is low, which is easy to cause over-etching, while the etching rate of the SC-2 solution for TiN is low, and when the thickness of the TiN layer is large, the etching less efficient.

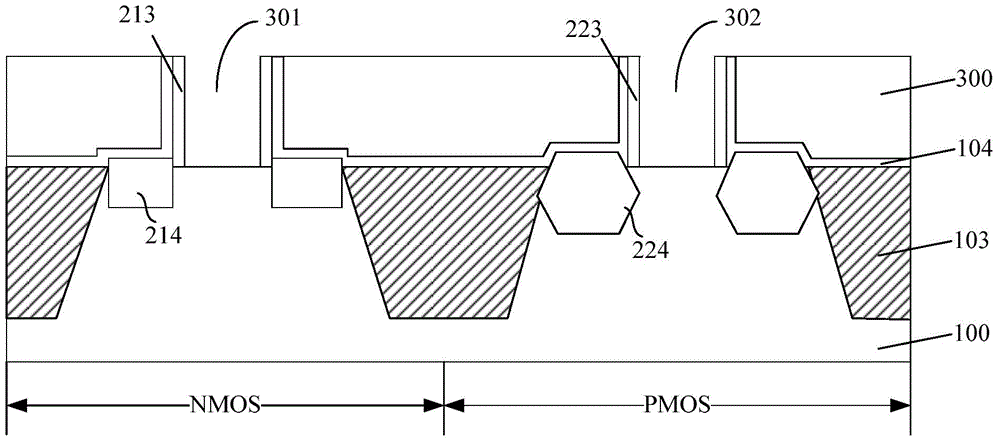

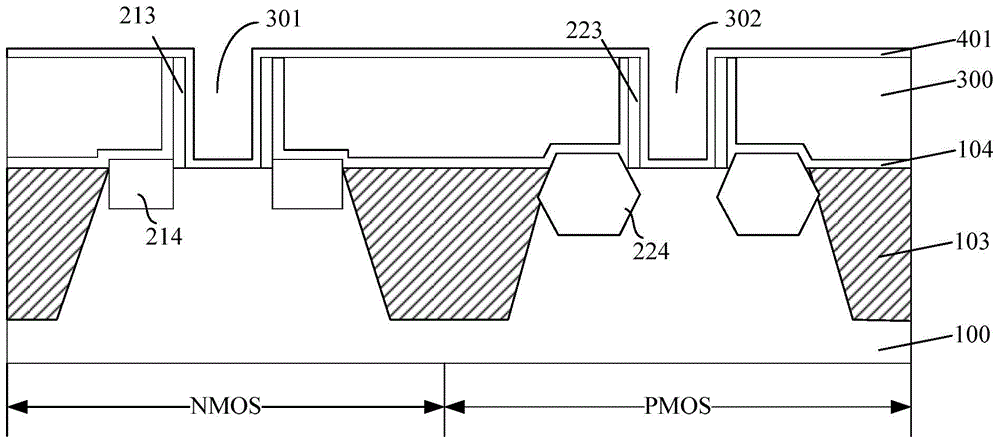

[0033] In the embodiment of the invention, an etching solution with higher etching efficiency and selectivity is used to etch the PMOS work function layer.

[0034] In ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| quality score | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More