Hole current shunting type power transistor with high avalanche tolerance and preparation method thereof

A power transistor and avalanche tolerance technology, which is applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve the problems of increased base resistance of parasitic triodes, increased device manufacturing costs, and low device avalanche tolerance of parasitic triodes. Achieve the effects of small leakage current, increased doping concentration, and low on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

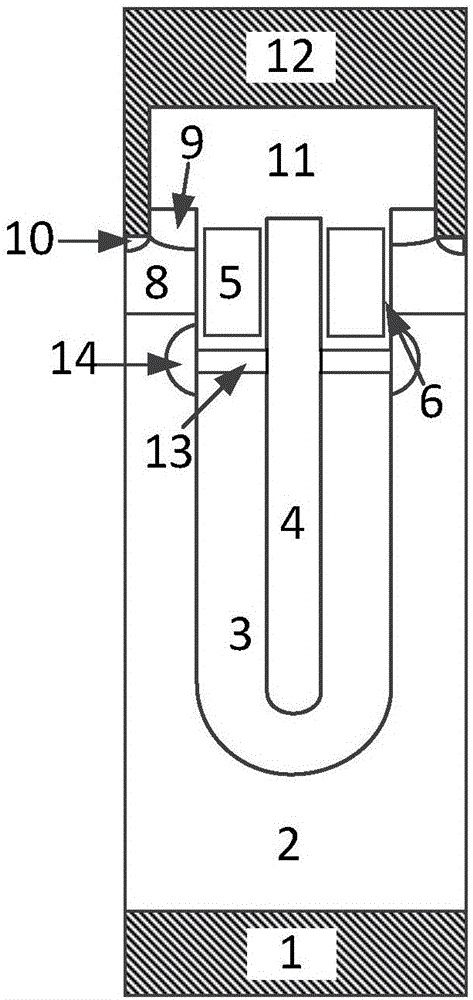

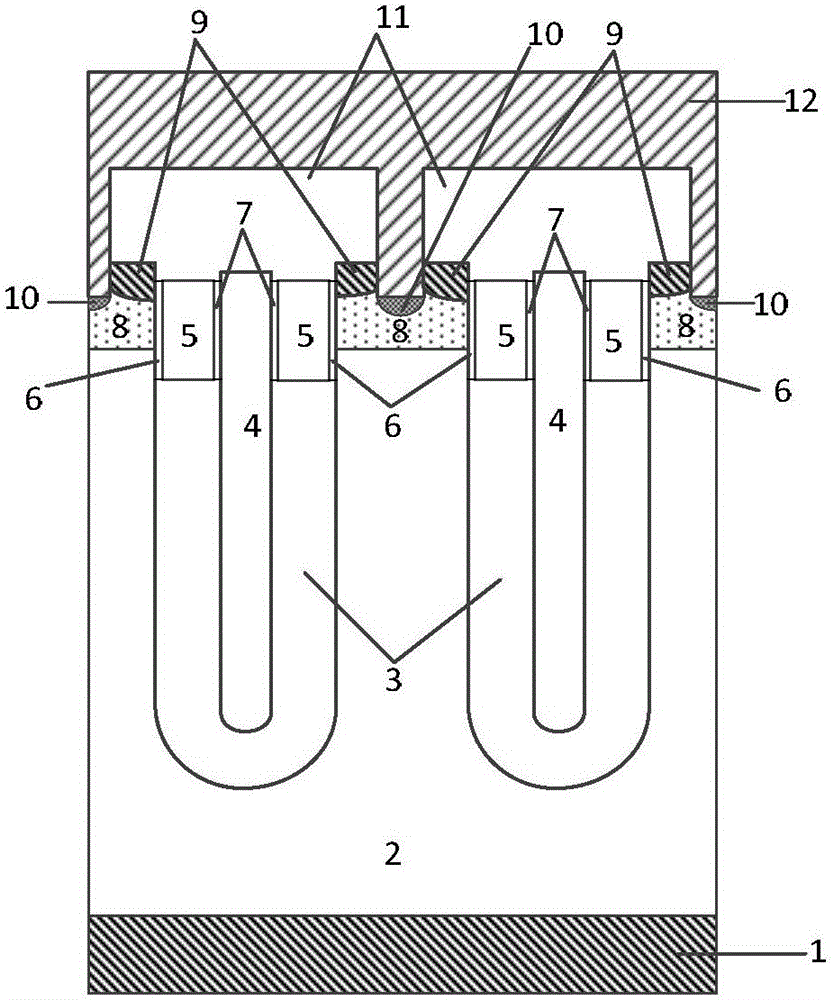

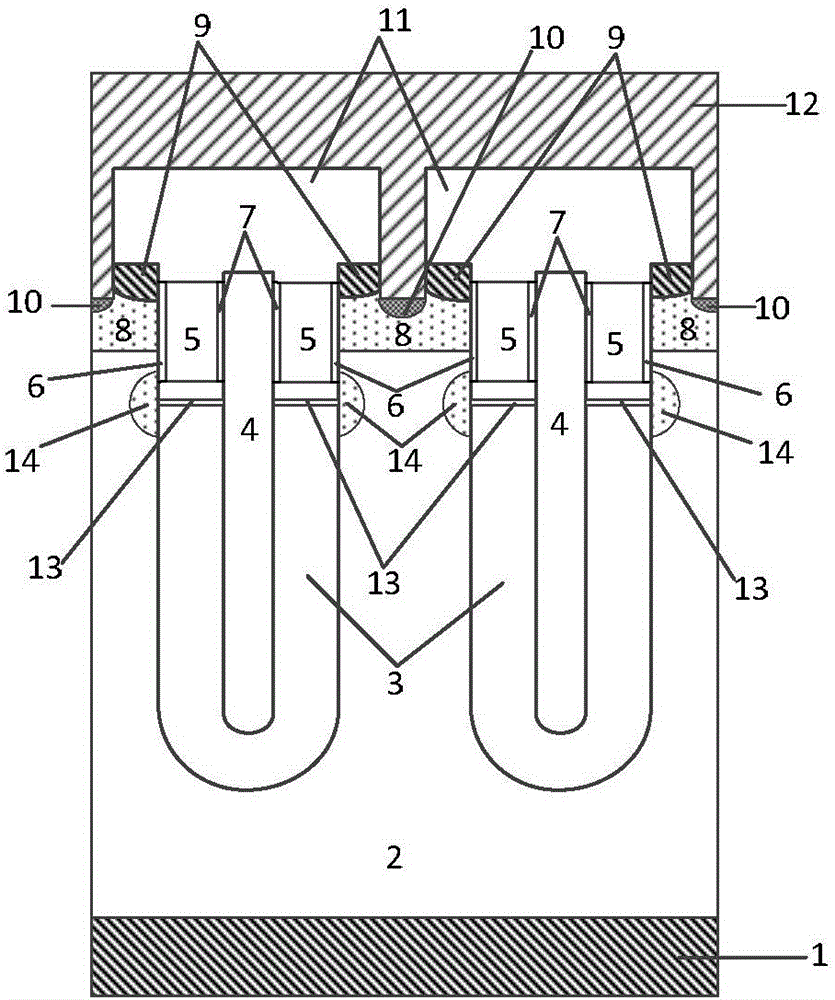

[0039] A hole current shunting power transistor with high avalanche tolerance, comprising: an N-type doped silicon substrate 1 also serving as a drain region, and an N-type doped silicon epitaxial layer 2 is arranged on the N-type doped silicon substrate 1 A trench is provided on the N-type doped silicon epitaxial layer 2, a field oxygen layer 3 is provided in the trench, a shield gate 4 and a gate 5 formed of polysilicon are provided in the field oxygen layer 3, and the gate 5 is located on both sides of the shield gate 4 and on the top of the field oxide layer 3, an insulating dielectric layer 7 is provided between the gate 5 and the shield gate 4, and at the same time, a gate oxide layer is provided between the gate 5 and the epitaxial layer 2 Layer 6, the surface of the epitaxial layer 2 between two adjacent trenches is provided with a P-type body region 8, and a P-type source region 10 and a heavily doped N-type source region 9 are arranged in the P-type body region 8 and ...

Embodiment 2

[0042] The present invention will be further described below in conjunction with specific drawings.

[0043] A preparation method of a hole current shunt power transistor with high avalanche tolerance is as follows:

[0044] Step 1: first select an N-type silicon material as an N-type doped silicon substrate 1 and epitaxially grow an N-type doped silicon epitaxial layer 2, and then etch a groove on the N-type doped silicon epitaxial layer 2, And grow out the field oxygen layer 3, forming Figure 10A structure shown;

[0045] The second step: depositing P-type polysilicon, the concentration range of the P-type impurities is 1e14 / cm3 to 1e20 / cm3, and then etching the P-type polysilicon to form the shield gate 4, forming Figure 10B structure shown;

[0046] The third step: etching part of the field oxygen layer 3 to form Figure 10C structure shown;

[0047] Step 4: Deposit P-type polysilicon, the concentration range of P-type impurities is 0 / cm3 to 1e20 / cm3, and the curren...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More