High efficiency silicon-based heterojunction double-sided battery and its preparation method

A double-sided cell and heterojunction technology, applied in the field of solar cells, can solve the problems of reducing the photoelectric conversion efficiency of the cell, that is, the output power, and reducing the short-circuit current of the cell, so as to increase the photoelectric conversion efficiency, improve the electrical performance, and reduce the recombination Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

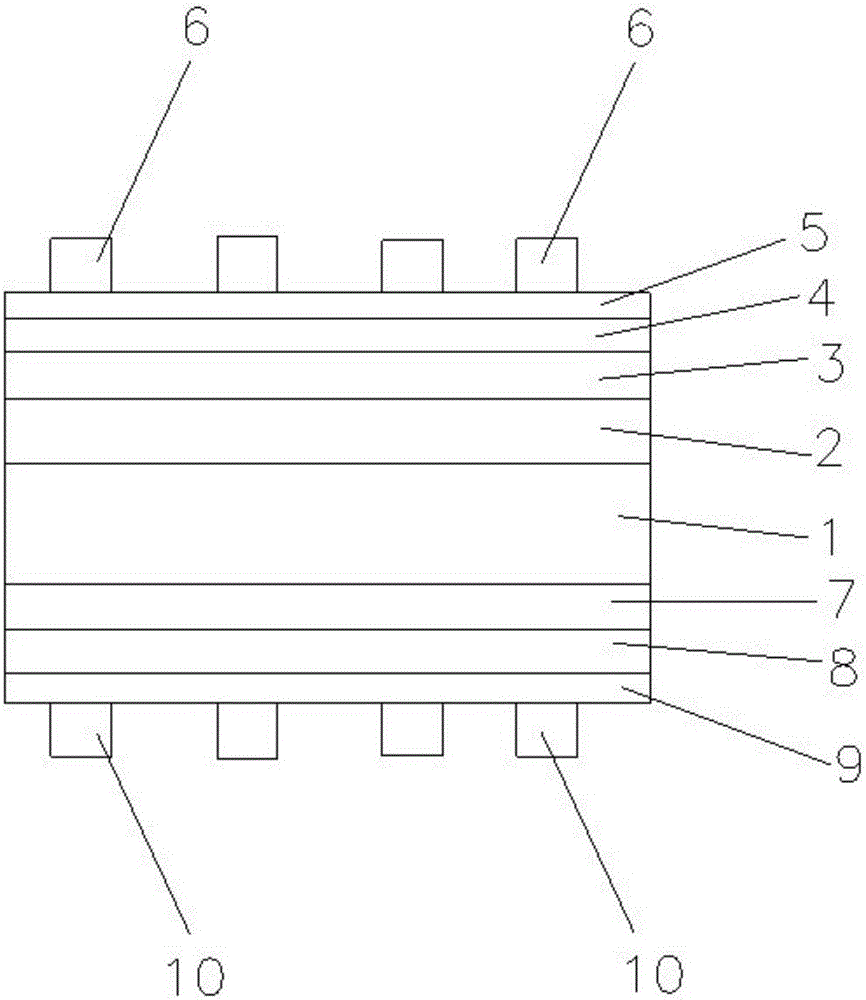

Image

Examples

Embodiment 1

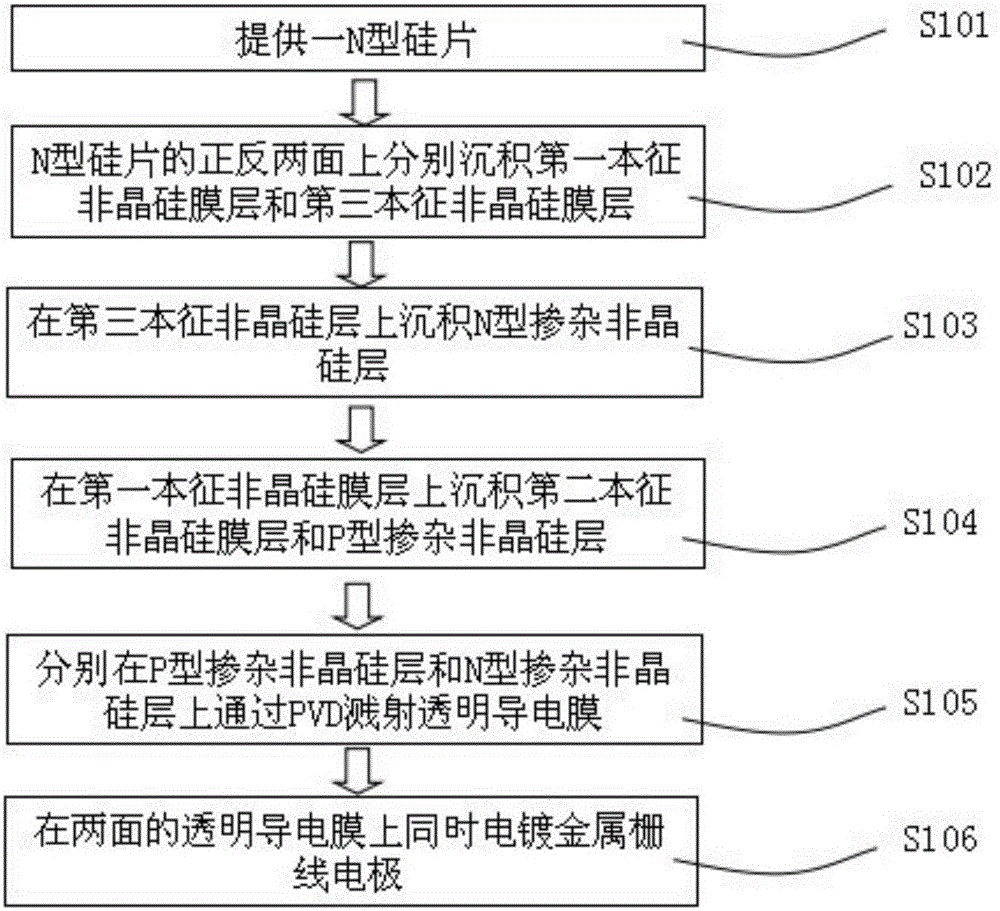

[0030] Such as figure 2 As shown, the invention discloses a method for preparing a high-efficiency silicon-based heterojunction double-sided battery, which includes the following steps:

[0031] S101: providing an N-type silicon wafer;

[0032] S102: Under the first temperature condition, respectively deposit a first intrinsic amorphous silicon film layer and a third intrinsic amorphous silicon film layer by chemical vapor deposition on both sides of the N-type silicon wafer;

[0033] S103: Depositing an N-type doped amorphous silicon layer on the third intrinsic amorphous silicon layer;

[0034] S104: Depositing a second intrinsic amorphous silicon film layer and a P-type doped amorphous silicon layer on the first intrinsic amorphous silicon film layer under a second temperature condition;

[0035] S105: Depositing a transparent conductive film on the P-type doped amorphous silicon layer and the N-type doped amorphous silicon layer by PVD (Physical Vapor Deposition) magnetro...

Embodiment 2

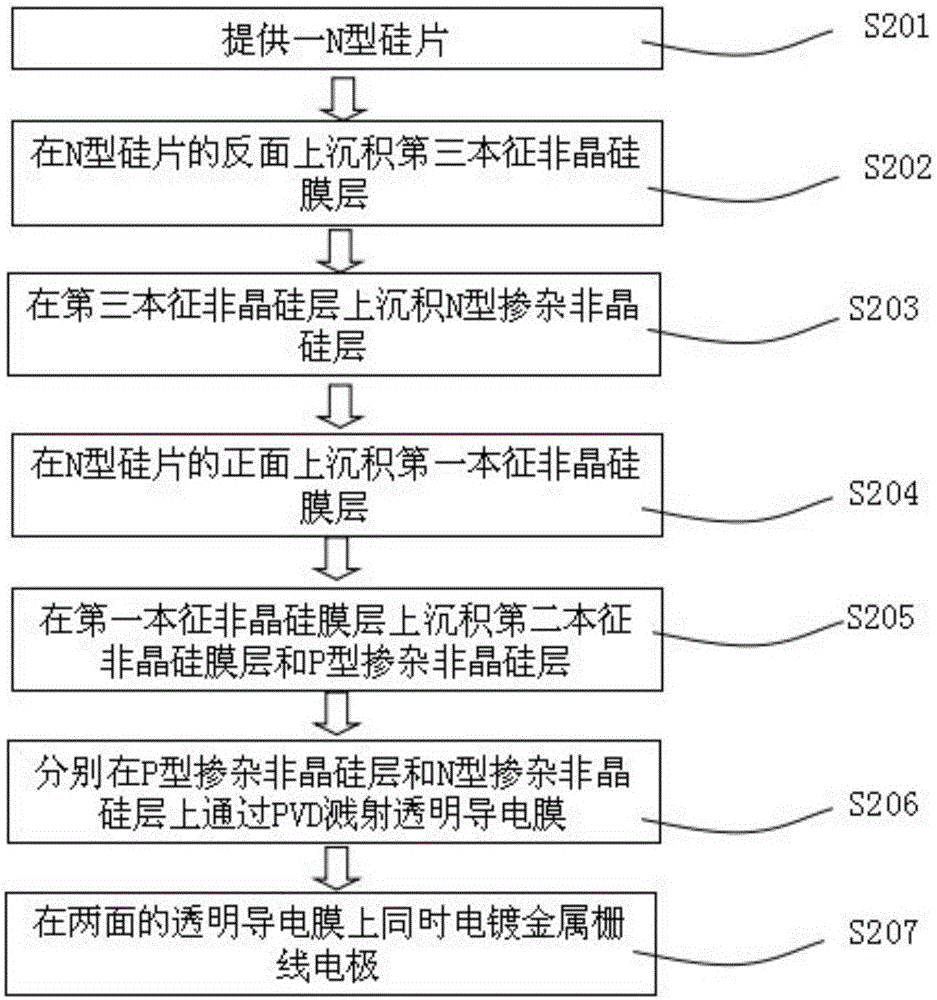

[0044] Such as image 3 As shown, the difference from Example 1 is that in this example, the third intrinsic amorphous silicon film layer and the N-type doped amorphous silicon layer on one side of the N-type silicon wafer are prepared first, and then another The first intrinsic amorphous silicon layer, the second intrinsic amorphous silicon layer and the P-type doped amorphous silicon layer on one side, and finally prepare a transparent conductive film layer and a metal grid line electrode, which specifically includes the following steps:

[0045] S201: providing an N-type silicon wafer;

[0046] S202: Under the first temperature condition, respectively deposit a third intrinsic amorphous silicon film layer on the reverse side of the N-type silicon wafer by chemical vapor deposition;

[0047] S203: depositing an N-type doped amorphous silicon layer on the third intrinsic amorphous silicon layer;

[0048] S204: respectively depositing a first intrinsic amorphous silicon film...

Embodiment 3

[0054] Such as Figure 4 As shown, the difference from Example 1 is that in this example, the first intrinsic amorphous silicon layer, the second intrinsic amorphous silicon layer and the P-type doped amorphous silicon layer on one side of the N-type silicon wafer are prepared first. crystalline silicon layer, and then prepare the third intrinsic amorphous silicon film layer and N-type doped amorphous silicon layer on the other side, and finally prepare a transparent conductive film layer and a metal grid line electrode, which specifically includes the following steps:

[0055] S301: providing an N-type silicon wafer;

[0056] S302: Depositing a first intrinsic amorphous silicon film layer on the front side of the N-type silicon wafer by chemical vapor deposition under the first temperature condition;

[0057] S303: Depositing a second intrinsic amorphous silicon film layer and a P-type doped amorphous silicon layer on the first intrinsic amorphous silicon film layer under a ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More