Low-resistance silicon on insulator-lateral insulated gate bipolar transistor (SOI-LIGBT) device capable of preventing snapback effect and manufacturing method thereof

A negative resistance effect and device technology, applied in the field of SOI-LIGBT devices and their manufacturing, can solve problems affecting device performance, etc., and achieve the effects of reducing device area, increasing vertical breakdown voltage, and low conduction loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

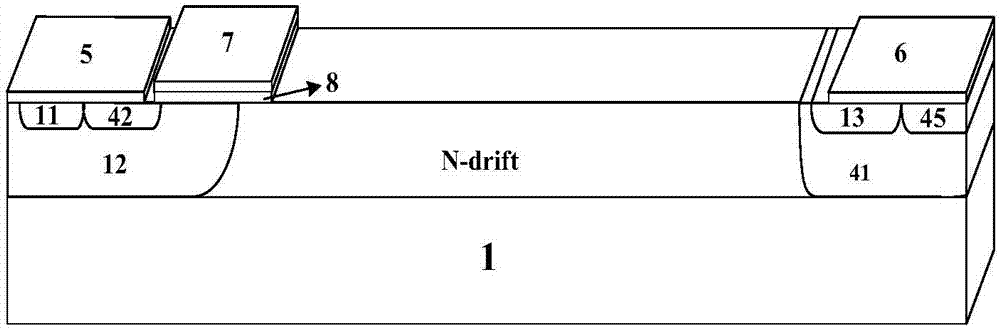

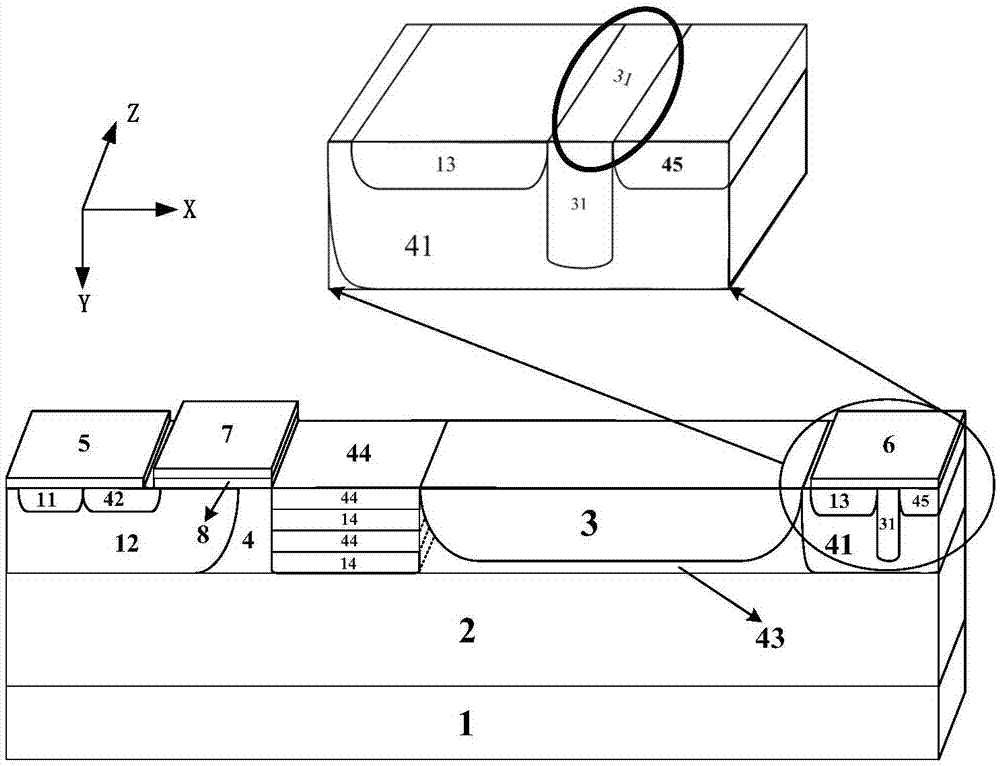

[0058] Such as figure 2 as shown, figure 2 It is a schematic diagram of the SOI-LIGBT device structure with low resistance and can suppress the negative resistance effect of this embodiment; its cell structure includes a substrate 1, a buried oxide layer 2 on the upper surface of the substrate 1, and a thickness above the buried oxide layer 2 The dielectric layer 3, the thick silicon layer drift region 4 on the left side of the thick dielectric layer 3, the P well region 12 at the left end inside the thick silicon layer drift region 4, and the mutually independent P-type heavily doped emitters arranged inside the P well region 12 The pole region 11 and the first N-type heavily doped region 42, the N-type buffer region 41 disposed at the right end of the thick dielectric layer 3 along the longitudinal direction, the P-type heavily doped collector region 13 at the left end inside the N-type buffer region 41, The second N-type heavily doped region 45 at the right end of the N-...

Embodiment 2

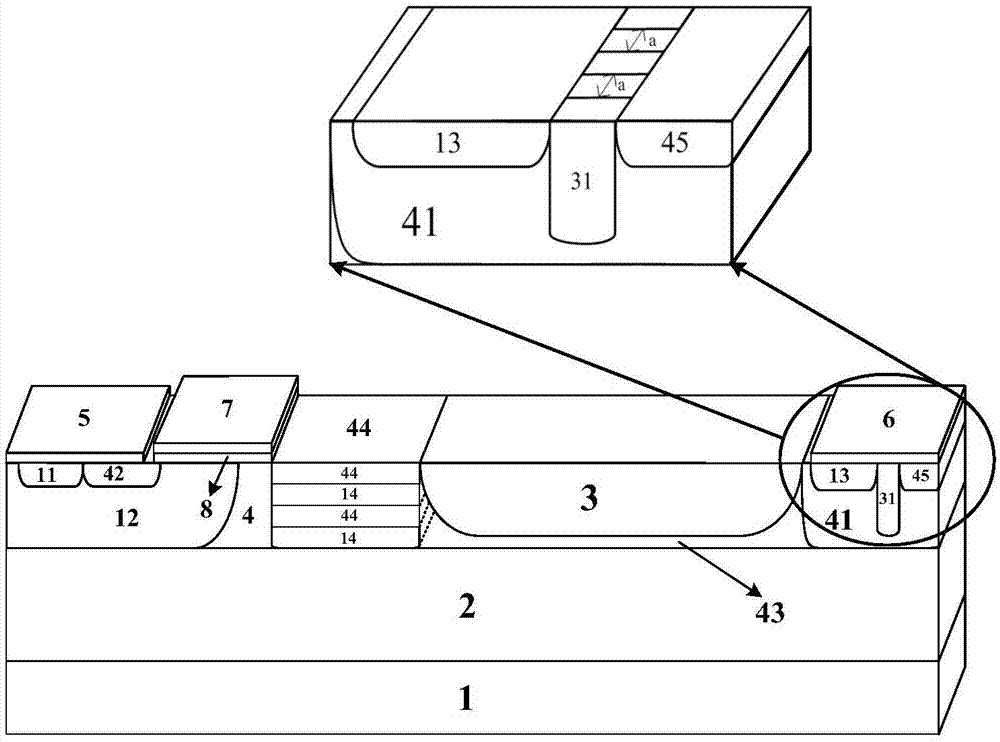

[0075] Such as image 3 As shown, this embodiment is basically the same as Embodiment 1, the difference is that: the collector dielectric barrier layer 31 in this embodiment includes a plurality of sub-barrier layers separated by N-type buffer regions 41 in the Z direction, adjacent sub-barrier layers The distance between the barrier layers in the Z direction is a.

Embodiment 3

[0077] Such as Figure 4 As shown, this embodiment is basically the same as Embodiment 1, with the difference that: in this embodiment, the N strips 44 and the P strips 14 are not in contact with the upper surface of the buried oxide layer 2 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More