Patents

Literature

73results about How to "High breakdown electric field" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

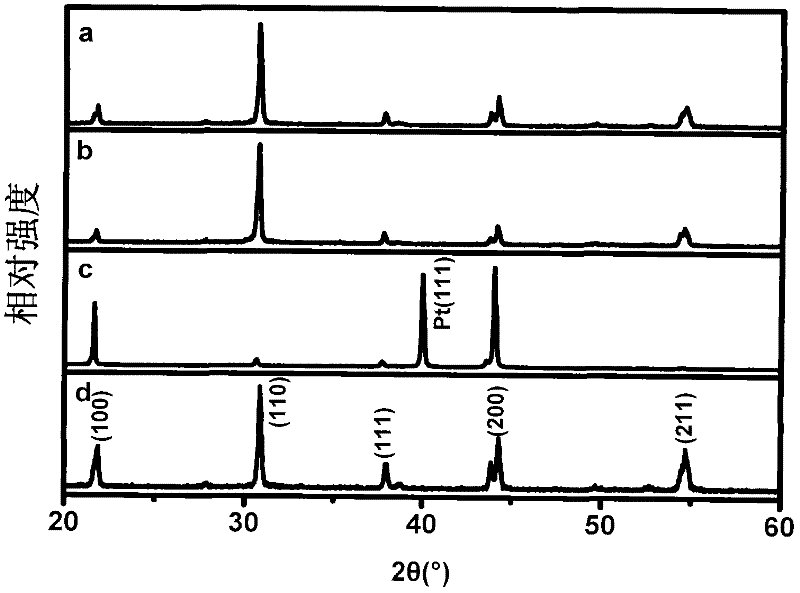

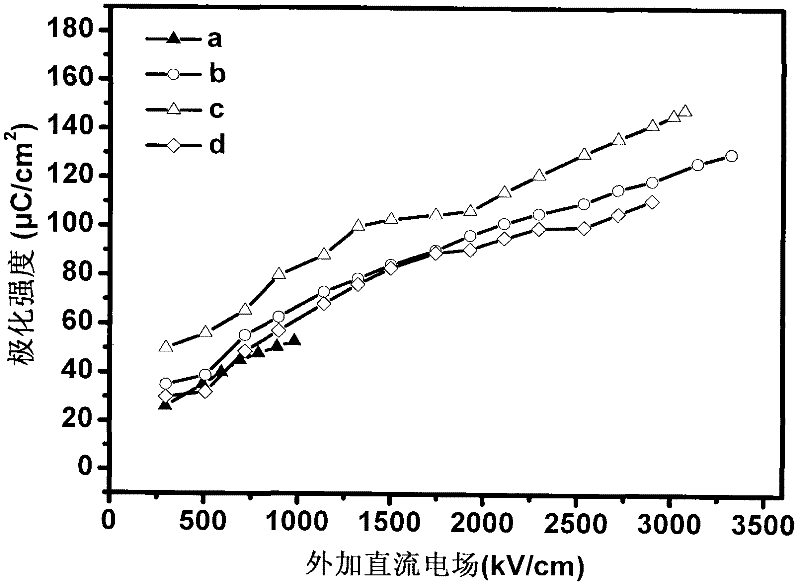

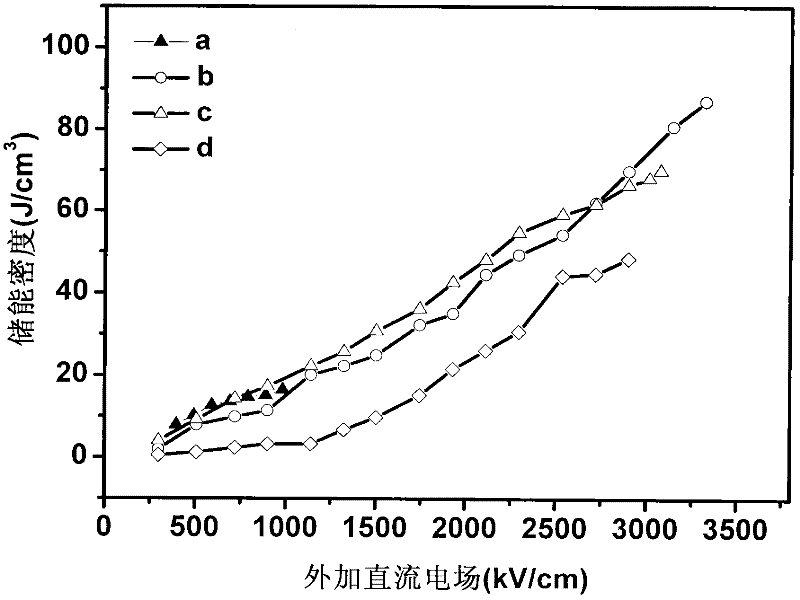

Anti-ferroelectric thick film with high breakdown field strength and preparation method

InactiveCN102584221AHigh breakdown electric fieldHigh saturation polarizationElectric fieldHigh energy

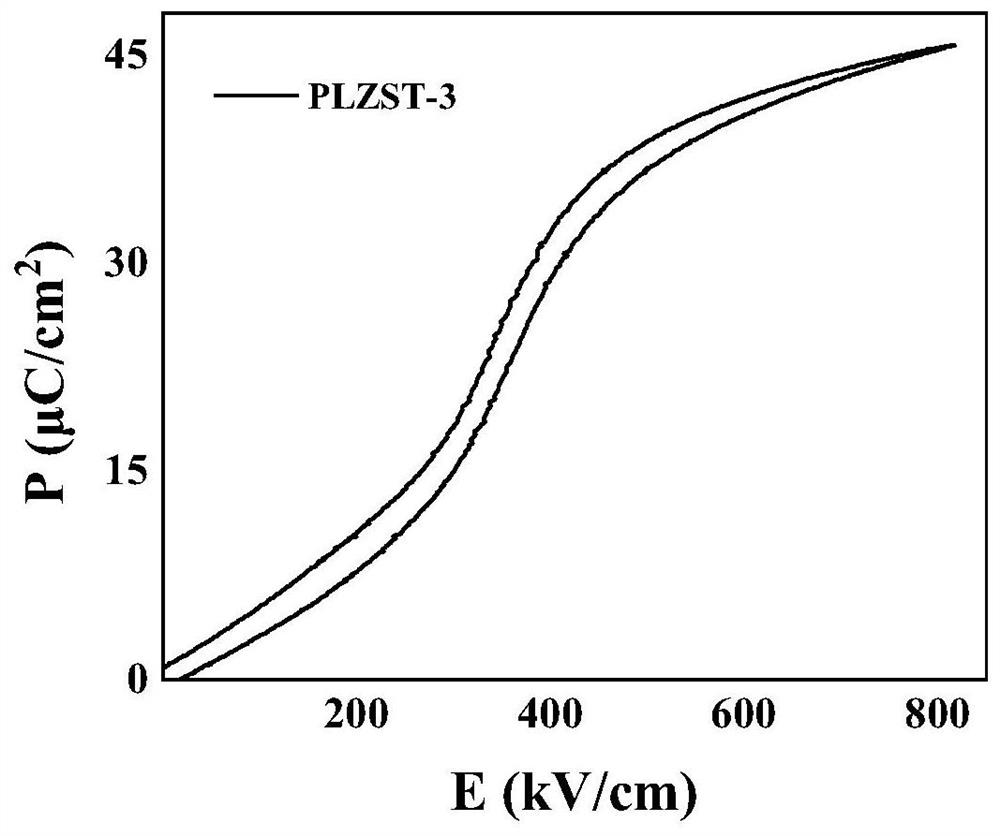

The invention relates to an anti-ferroelectric thick film with high breakdown field strength and a preparation method. The general chemical formula of the anti-ferroelectric thick film is (Pb1-aLa2a / 3)(Zr1-x-ySnxTiy)O3, wherein a is larger than or equal to 0 and smaller than or equal to 0.06, x is larger than or equal to 0 and smaller than or equal to 0.45 and y is larger than or equal to 0 and smaller than or equal to 0.10; polyvinylpyrrolidone (PVP) is adopted as a film forming additive; and the molar ratio of (Pb1-aLa2a / 3)(Zr1-x-ySnxTiy)O3 to PVP is 1: (0.5 to 2). The anti-ferroelectric thick film provided by the invention has high breakdown field strength as well as high saturated polarization strength, and can be applied to high energy density capacitors.

Owner:INNER MONGOLIA UNIV OF SCI & TECH

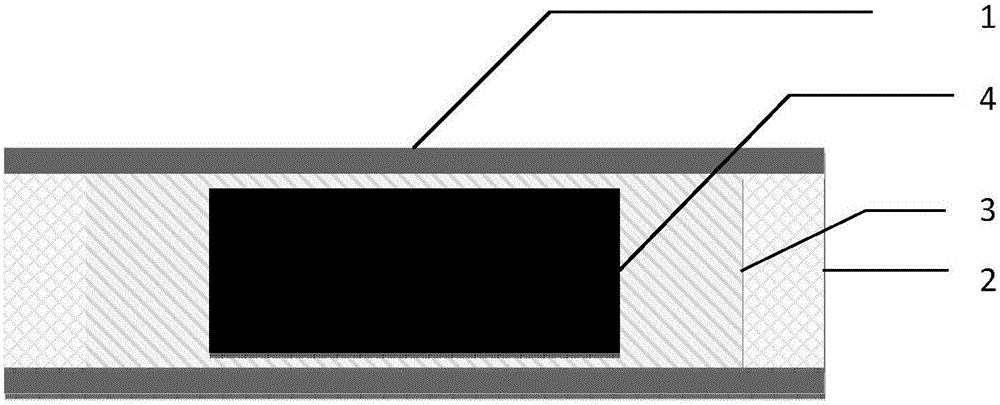

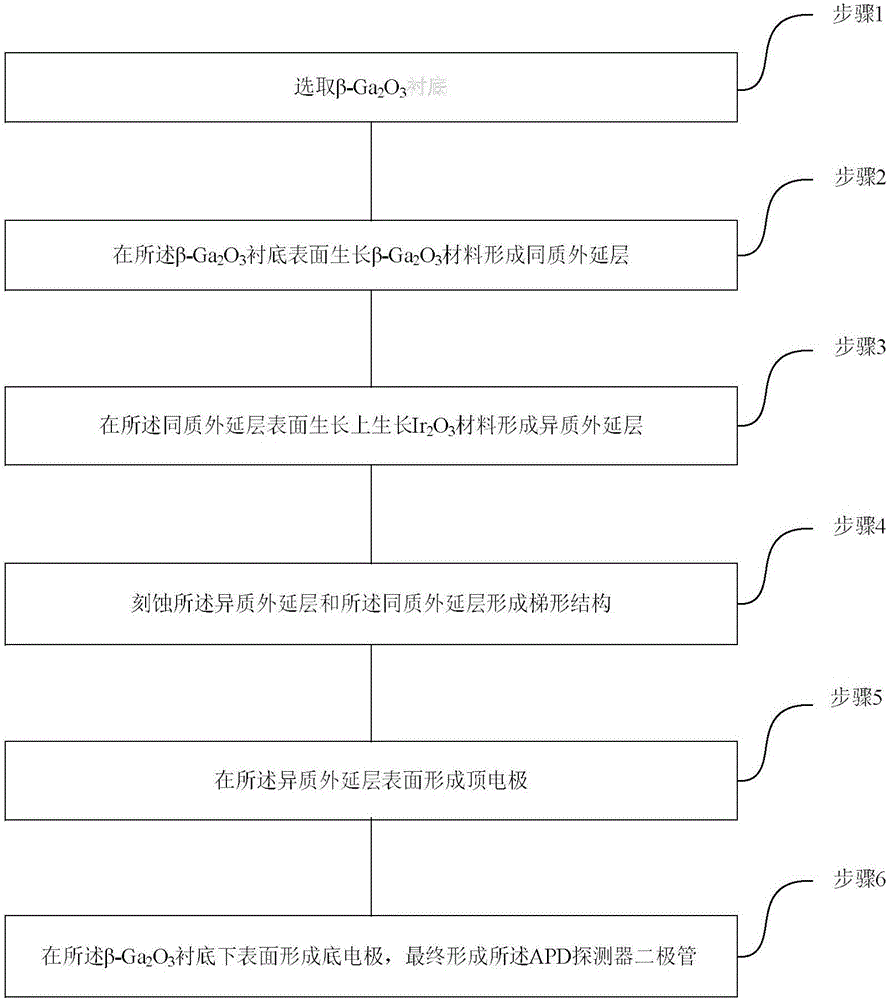

Deep ultraviolet APD detection diode based on Ir2O3/Ga2O3 and manufacturing method thereof

ActiveCN106409987AHigh light transmittanceHigh transparencySemiconductor devicesHigh pressureLight penetration

The invention relates to a deep ultraviolet APD detection diode based on Ir2O3 / Ga2O3 and a manufacturing method thereof. The method comprises the following steps of selecting a beta-Ga2O3 substrate; growing a beta-Ga2O3 material on a beta-Ga2O3 substrate surface to form a homogeneous epitaxial layer; growing an Ir2O3 material on a homogeneous epitaxial layer surface so as to form a heterogeneous epitaxial layer; etching the heterogeneous epitaxial layer and the homogeneous epitaxial layer to form a trapezoidal structure; forming a top electrode on a heterogeneous epitaxial layer surface; and forming a bottom electrode on a lower surface of the beta-Ga2O3 substrate and finally forming an APD detector diode. In the invention, the beta-Ga2O3 material is used, a super high light penetration rate and transparency of the material in a deep ultraviolet area and a visible light area are performed, super high voltage withstanding performance of an APD detector and a high breakdown electric field are ensured; the diode is suitable for extreme environments of a high frequency, high radiation, high temperature and high voltage and the like; under the extreme environments, device reliability can be greatly increased and detection performance is better than that of an existing APD detector.

Owner:XIDIAN UNIV

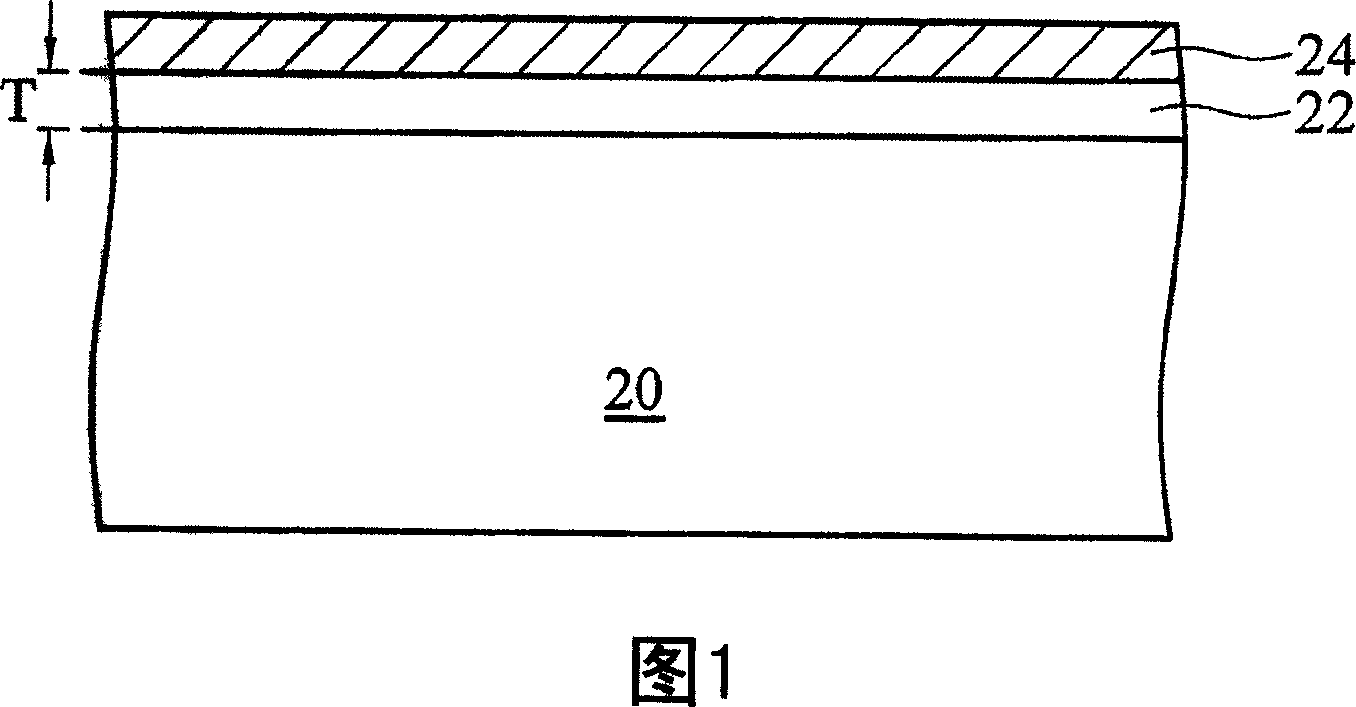

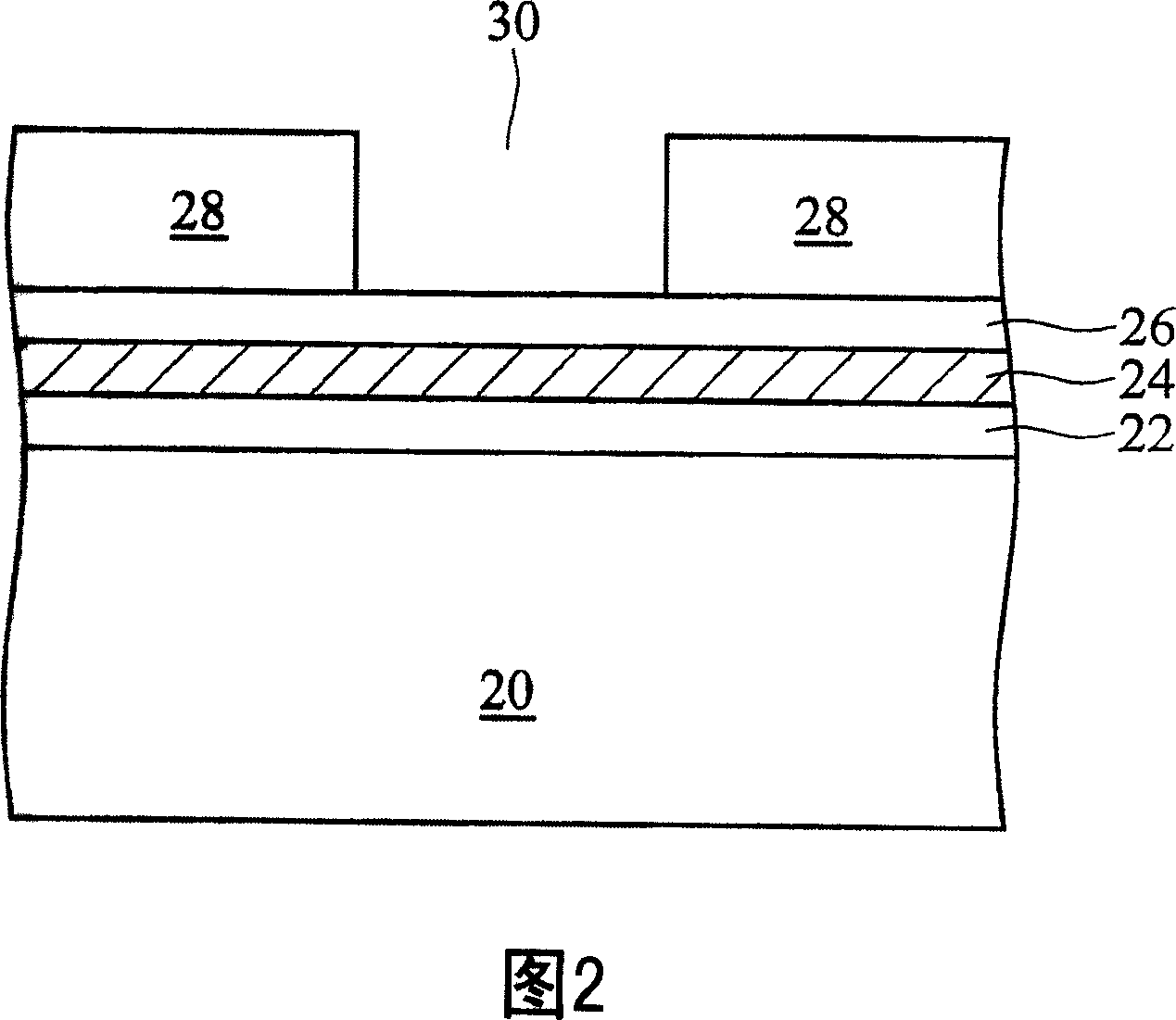

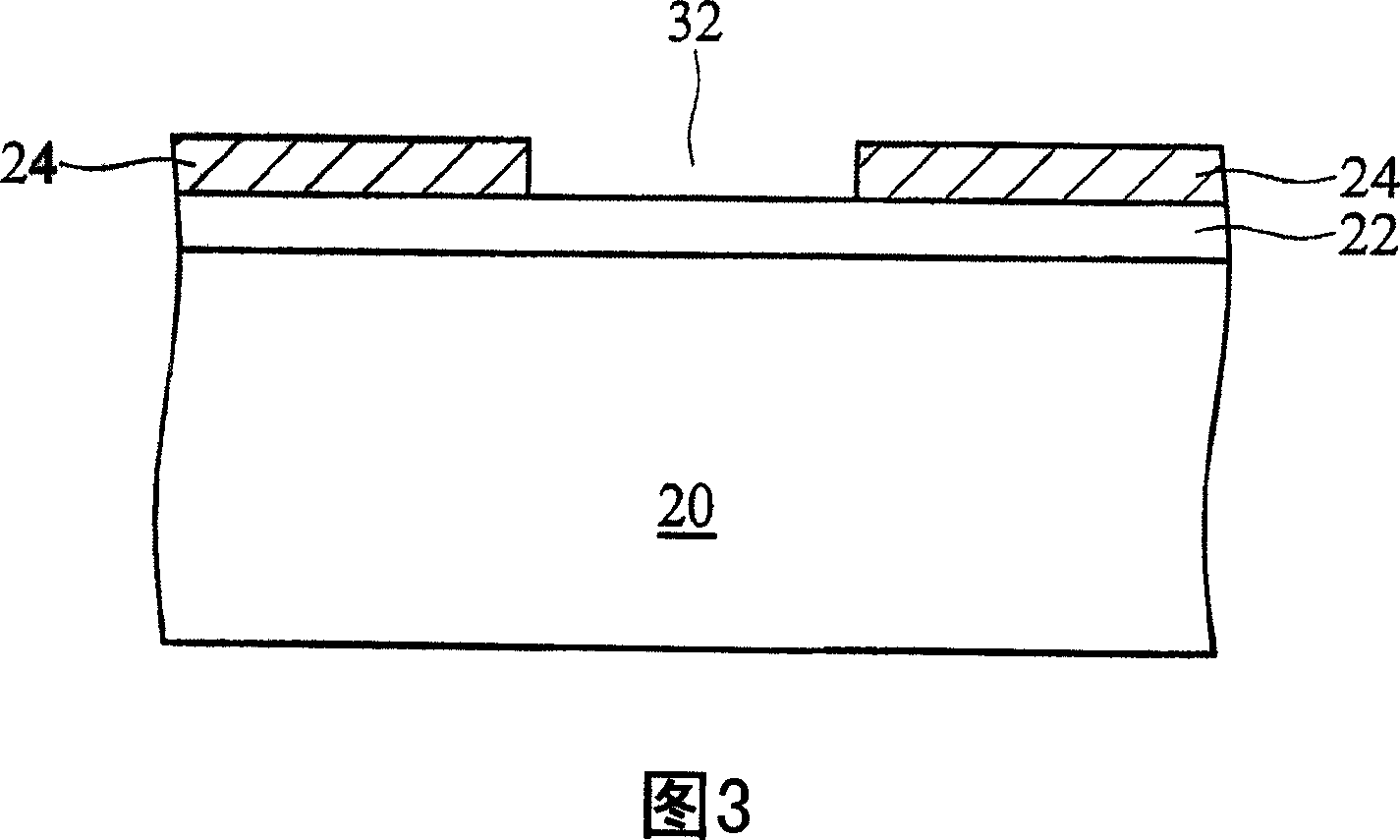

Semiconductor structure and forming method thereof

InactiveCN101030566AHigh mechanical strengthImprove thermal stabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureHigh electron

The present invention discloses a semiconductor structure and a method for forming the semiconductor structure; the semiconductor structure comprises: a dielectric layer with a low dielectric constant; an top cover layer on the dielectric layer, wherein, the top cover layer is made of a material formed by a compound group selected from CNx, SiCN, SiCO, SiC, and their mixtures; a dielectric substance in the dielectric layer; and, a metal conductor, which is in the dielectric layer and covers the dielectric substance; in addition, the body of the metal conductor contacts the dielectric substance. The semiconductor structure and the method provided in the present invention are characterized in stability under high-temperature and high electron breakdown field, can improve impedance to thermal circulation and electric power applied, and improve mechanical strength of the semiconductor structure, without any additional manufacturing cost.

Owner:TAIWAN SEMICON MFG CO LTD

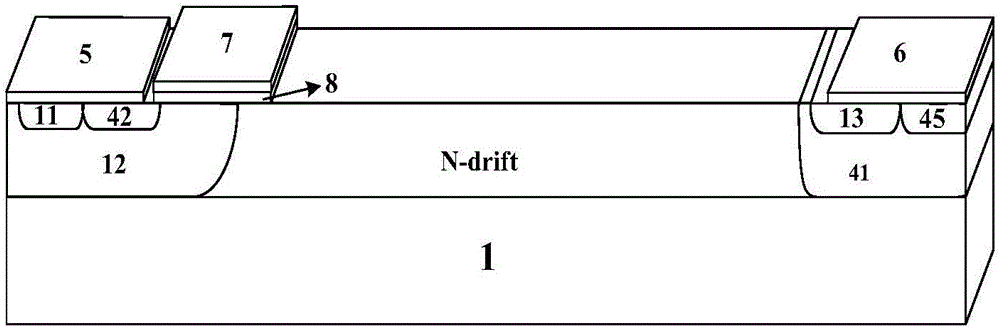

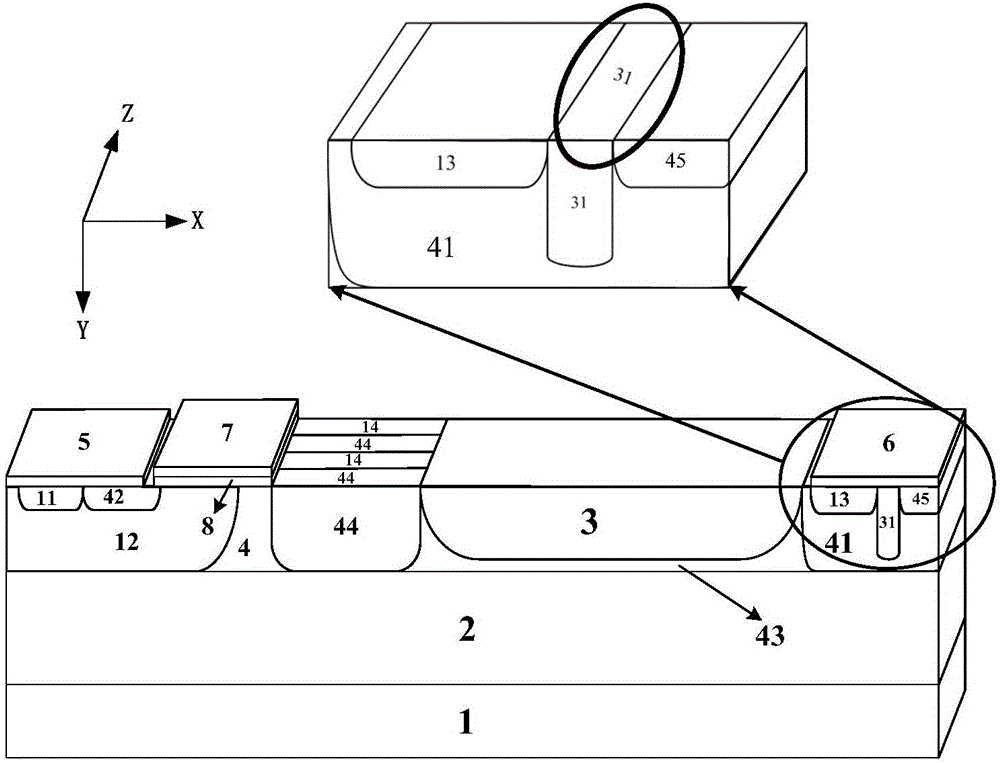

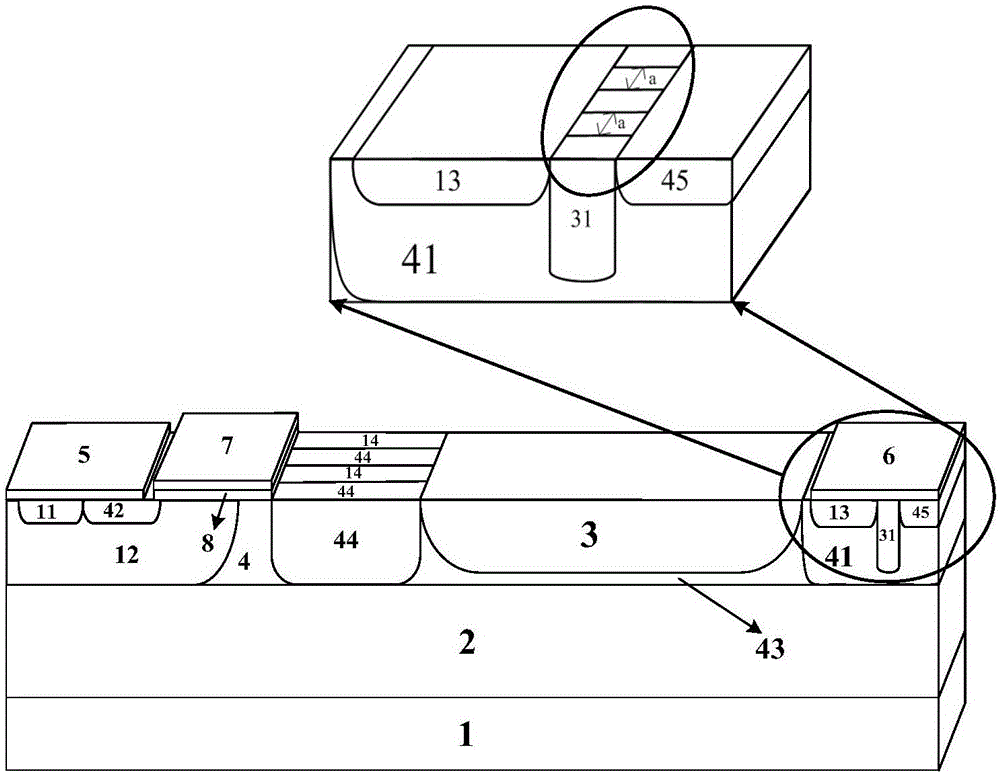

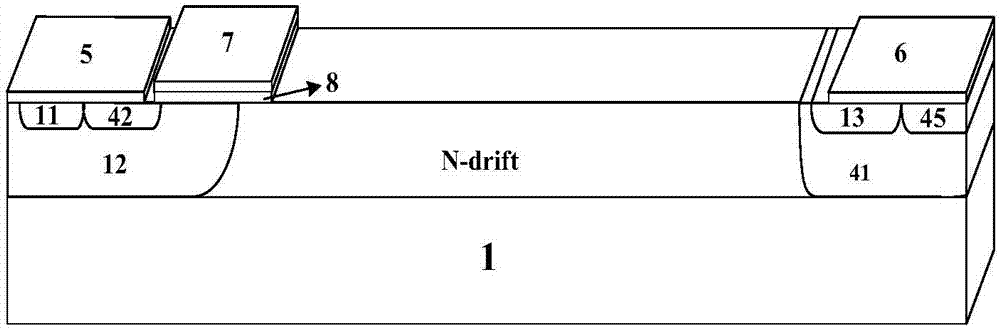

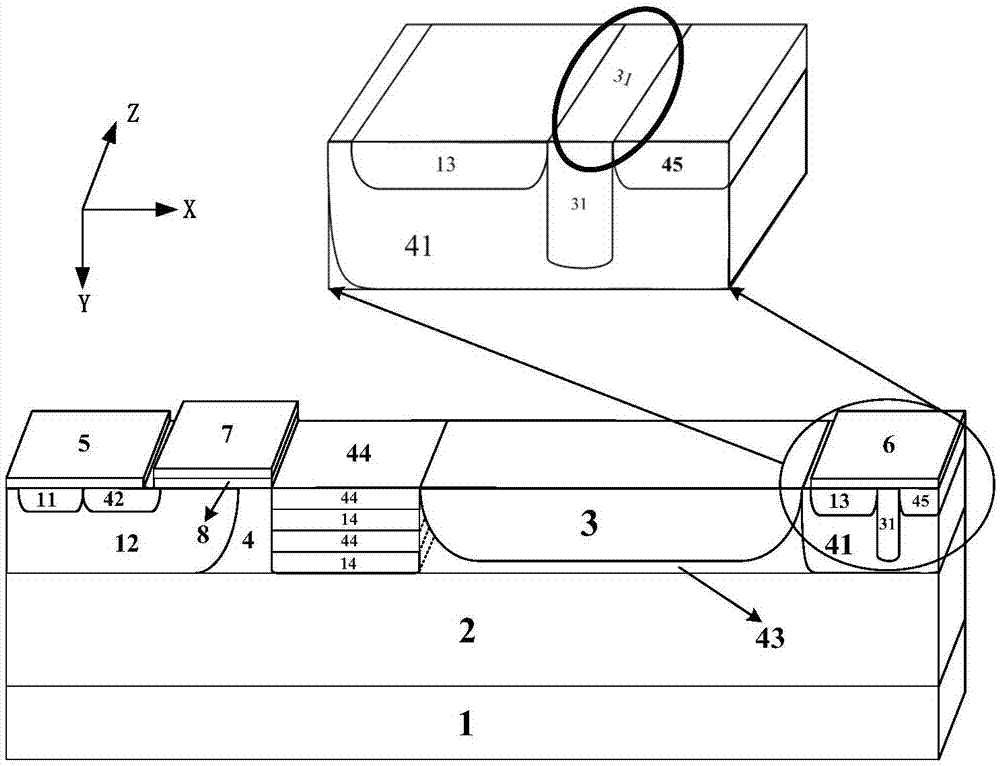

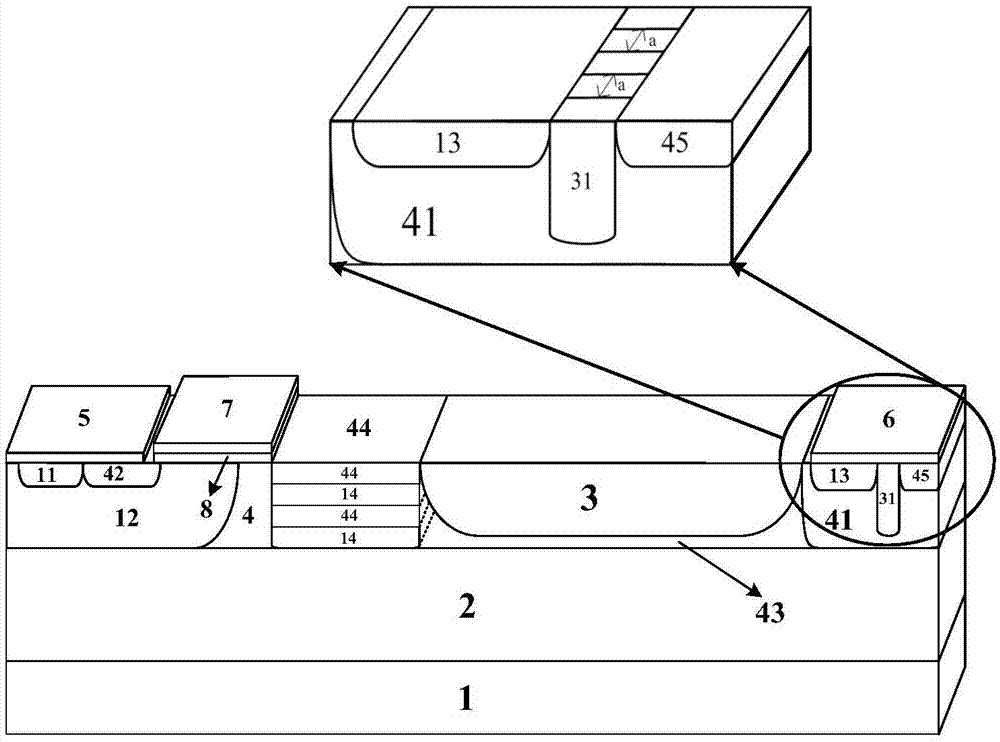

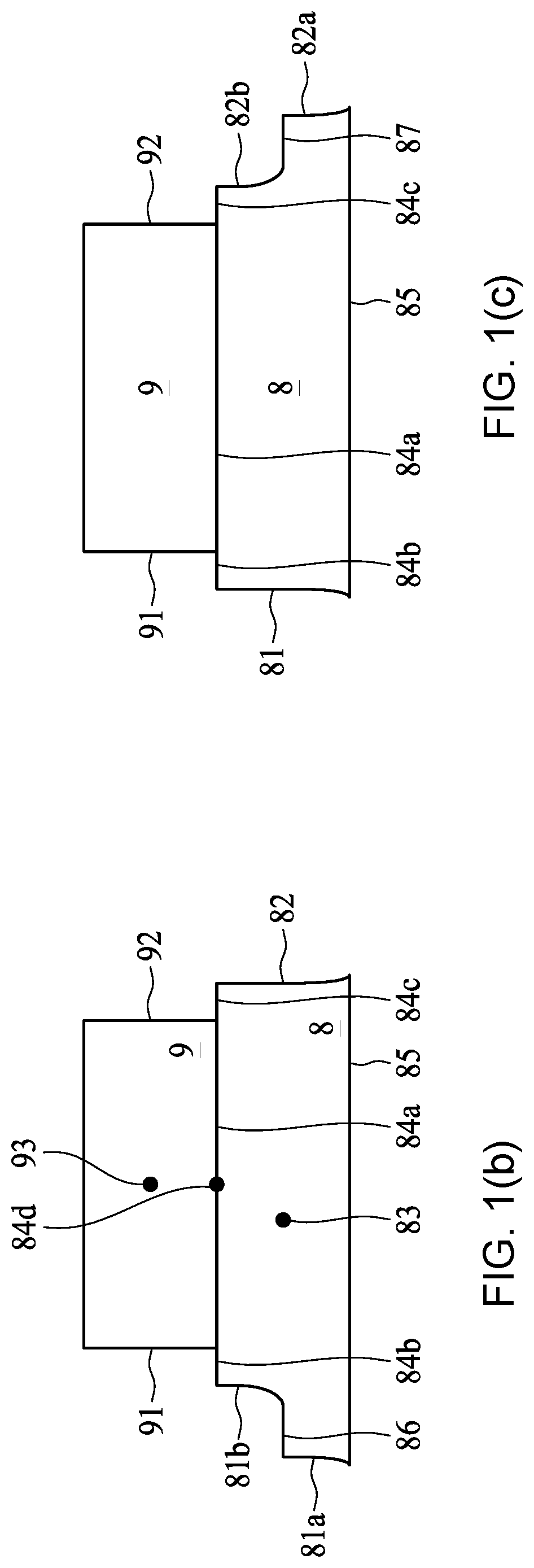

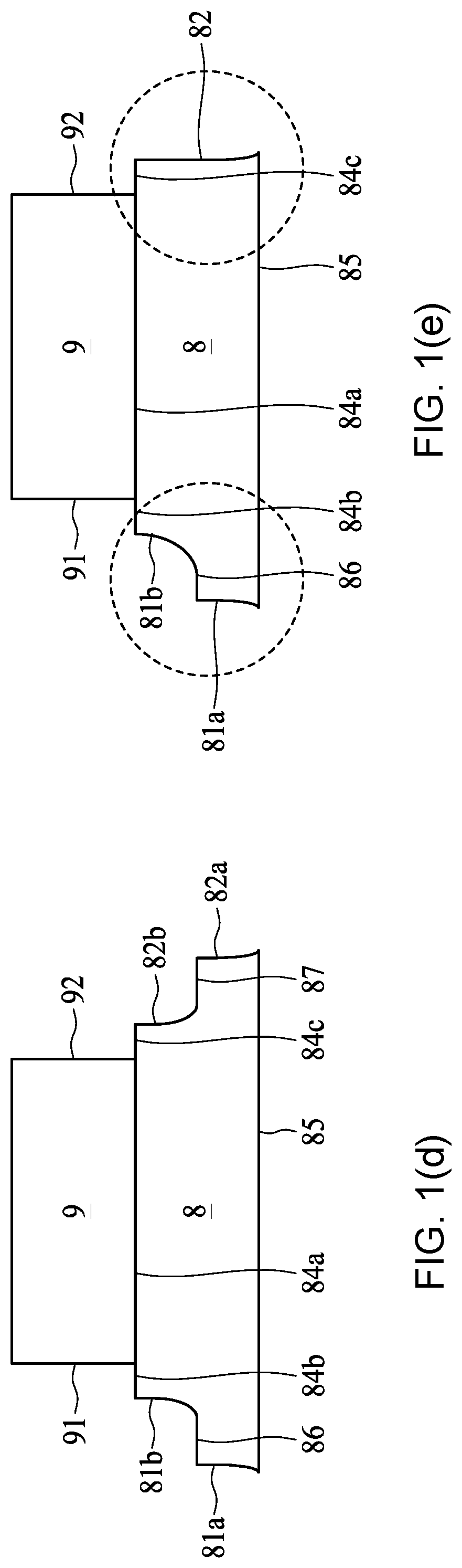

SOI-LIGBT device capable of suppressing Snapback phenomenon and manufacturing method thereof

InactiveCN106847883AImprove vertical breakdown voltageImprove electric field distributionSemiconductor/solid-state device manufacturingSemiconductor devicesElectric fieldContact electrode

The invention provides an SOI-LIGBT device capable of suppressing a Snapback phenomenon and a manufacturing method thereof. The cellular structure of the SOI-LIGBT device comprises a substrate, a buried oxygen layer, a thick dielectric layer, a thick silicon layer drift region, a P well region, a P-type heavily doped emitter region, a first N-type heavily doped region, a N-type buffer region, a P-type heavily doped collector region, a second N-type heavily doped region, a collector dielectric barrier layer, a collector contact electrode, a ultrathin top layer silicon drift region, a P emitter contact electrode, a gate oxide layer, a polysilicon gate, P strips, and N strips. The N strips and the P strips are alternately arranged in the thick silicon layer drift region in the Z direction. The ultrathin top layer silicon drift region enhances the buried layer electric field to improve the longitudinal breakdown voltage of the SOI device. The thick silicon layer drift region reduces the specific on-resistance of the device. Lateral linear variable doping is performed on the ultrathin top layer silicon drift region and the thick silicon layer drift region to adjust the surface electric field distribution so that the specific on-resistance is greatly reduced while the high breakdown voltage of the device is maintained.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA +1

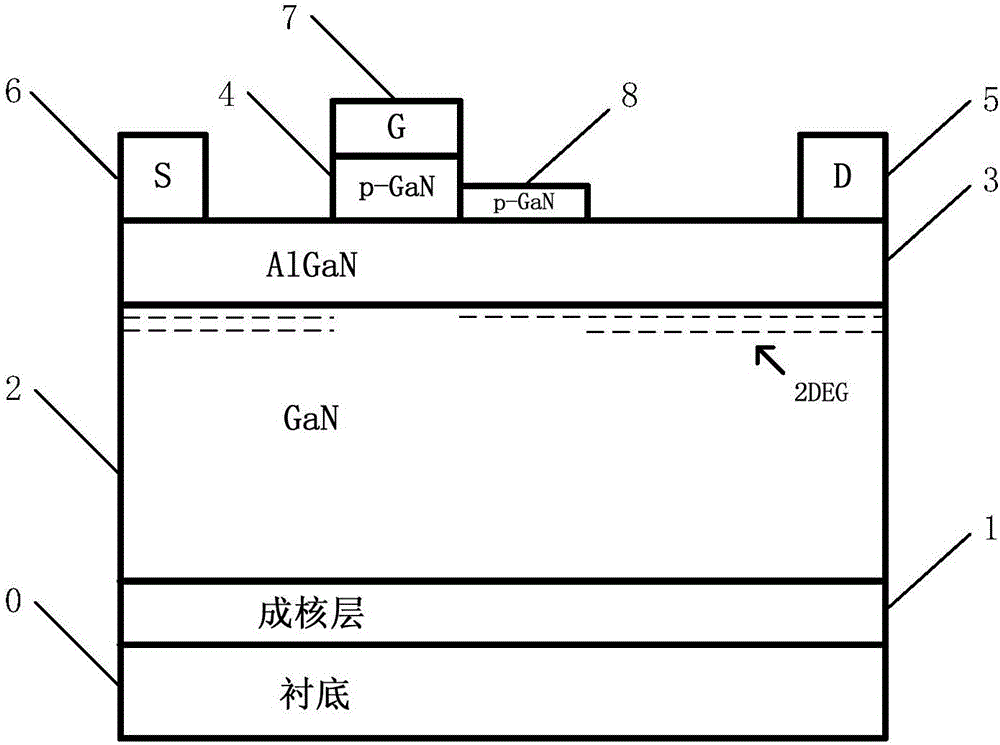

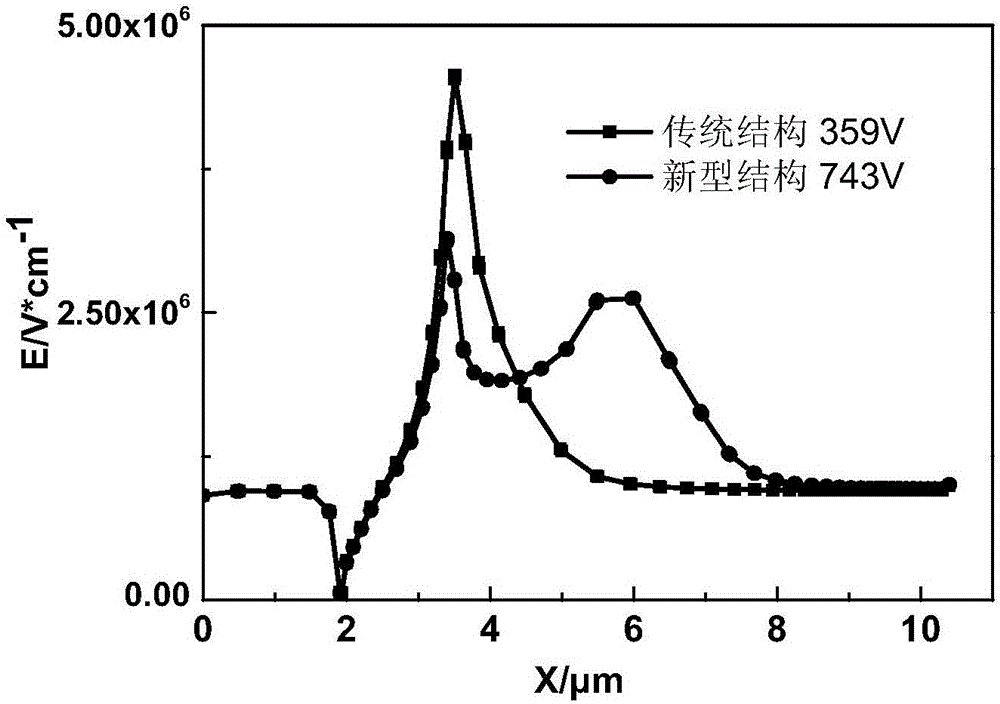

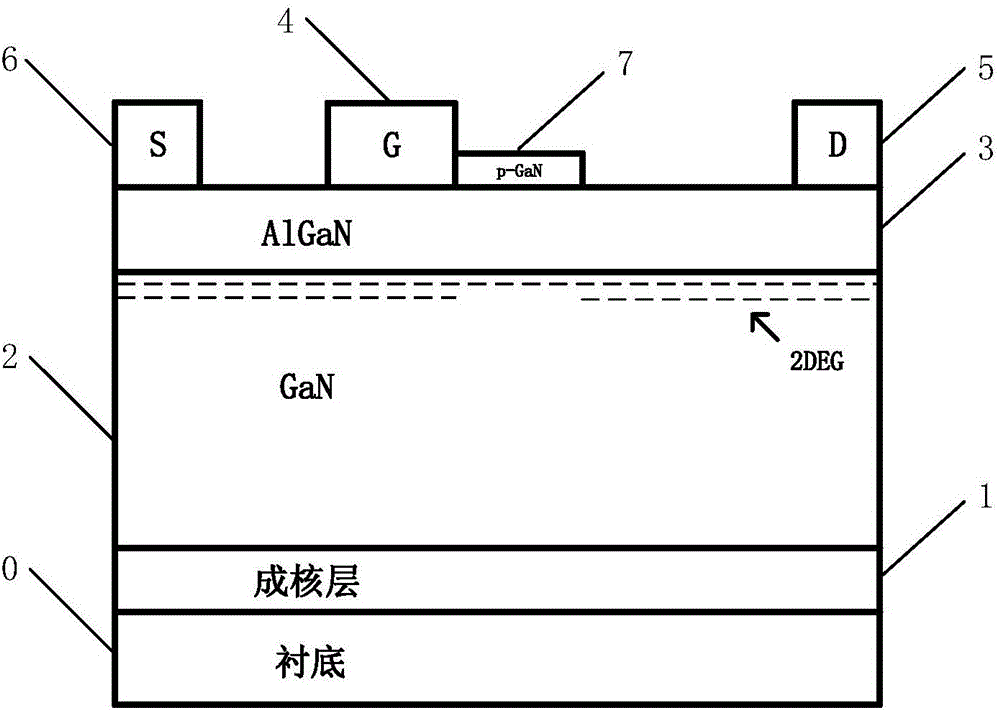

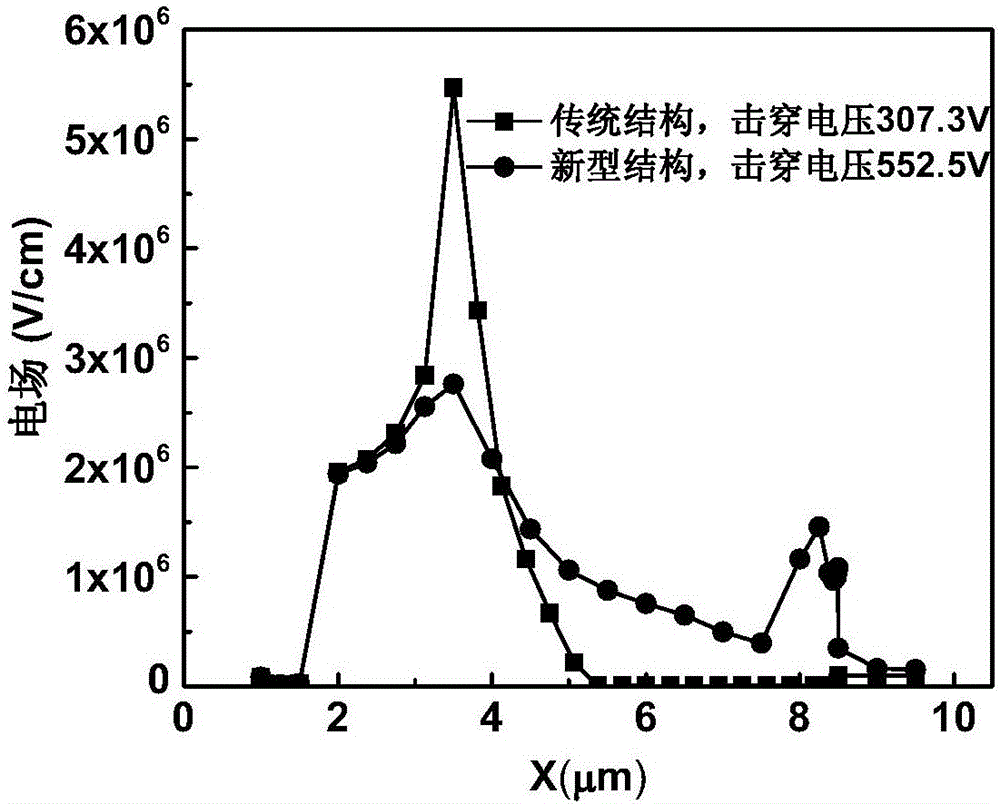

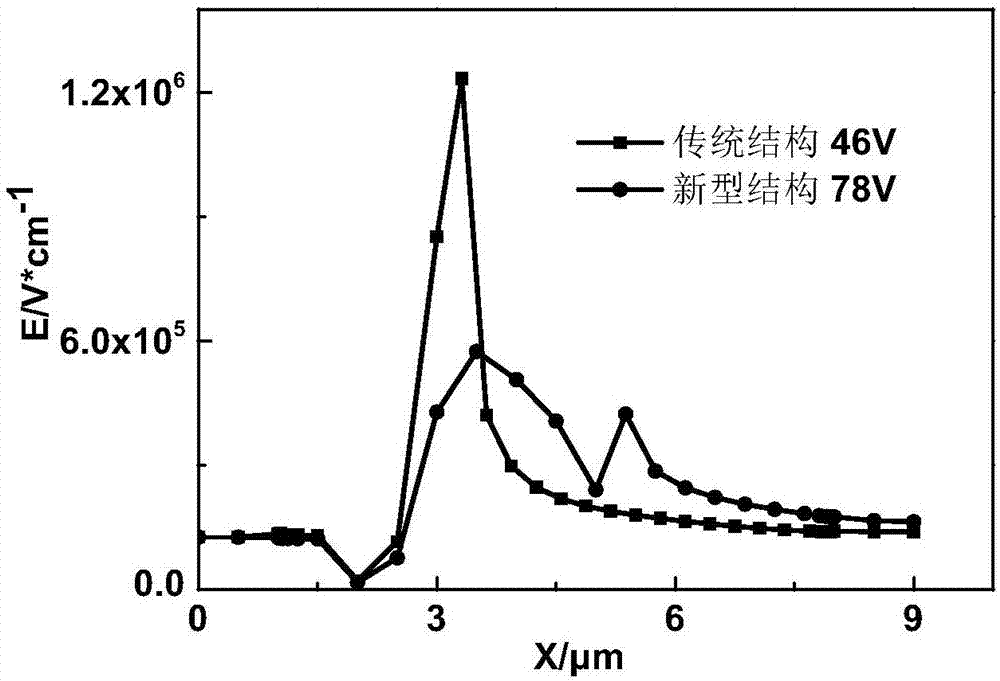

Step p-GaN enhanced AlGaN/GaN heterojunction field effect transistor

InactiveCN106783960AReduce high electric fieldIncrease peak electric field dropSemiconductor devicesElectric field modulationGas concentration

The invention discloses a step p-GaN enhanced AlGaN / GaN heterojunction field effect transistor. According to the transistor structure, a p type GaN cap layer is introduced into the transistor grid edge, and the thickness of the cap layer is smaller than that of a p type GaN dielectric layer under a grid. The p type GaN cap layer can lower the two-dimensional electron gas concentration of a conducting channel in the area, and the electric field modulation effect is achieved. By generating a new electric field peak, a high electric field at the grid edge is lowered, and electric field distribution on the surface of the transistor is more uniform. Compared with a traditional p-GaN enhanced structure, the step p-GaN enhanced AlGaN / GaN heterojunction field effect transistor is obviously raised and improved in the aspects of breakdown voltage and reliability.

Owner:XIDIAN UNIV

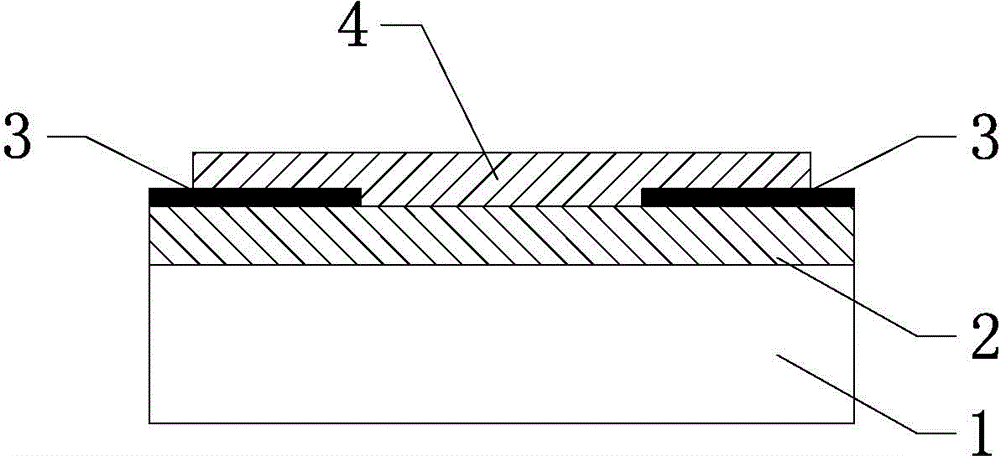

Photoconductive semiconductor switch structure

InactiveCN102945887AHigh breakdown electric fieldReduce dark currentSemiconductor devicesPower flowSemiconductor

The invention relates to the technical field of semiconductor apparatuses, and in particular relates to a photoconductive semiconductor switch structure. The photoconductive semiconductor switch structure comprises a substrate, wherein a first silicon carbide film is arranged on the top surface of the substrate; electrodes are respectively arranged on the two ends of the top end surface of the first silicon carbide film; a second silicon carbide film is arranged on the top end surfaces of the electrodes; and the second silicon carbide film covers a gap between the electrodes and part area on the top end surfaces of the electrodes. According to the photoconductive semiconductor switch structure disclosed by the invention, a silicon carbide film is arranged on the top end surfaces of the electrodes to increase the contact area of the silicon carbide film and the electrodes, so that break-over current can circulate from the two surfaces of the electrodes. Meanwhile, breakdown voltage and break-over current of the photoconductive semiconductor switch are improved, and the dark current is reduced.

Owner:DONGGUAN WUFENG TECH

AlGaN/GaN heterojunction field effect transistor with partial P type GaN cap layer

InactiveCN106783961AReduce concentrationUniform electric field distributionSemiconductor devicesElectric field modulationGas concentration

The invention discloses an AlGaN / GaN heterojunction field effect transistor with a partial P type GaN cap layer. According to the transistor structure, the P type GaN cap layer is introduced into the grid edge of the transistor and will reduce the two-dimensional electron gas concentration of a conducting channel of the region to achieve the electric field modulation effect. By generating a new electric field peak, high electric field of the grid edge is reduced, and the electric field on the surface of the transistor is more uniform. Compared with a traditional structure, the breakdown voltage and reliability of the field effect transistor are obviously improved.

Owner:XIDIAN UNIV

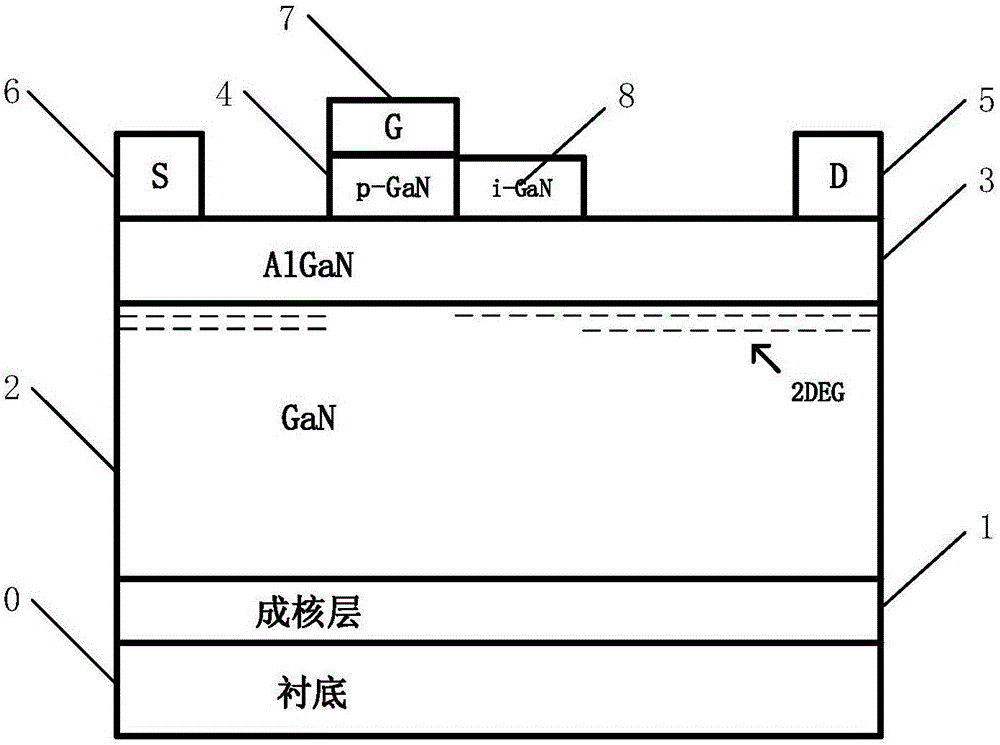

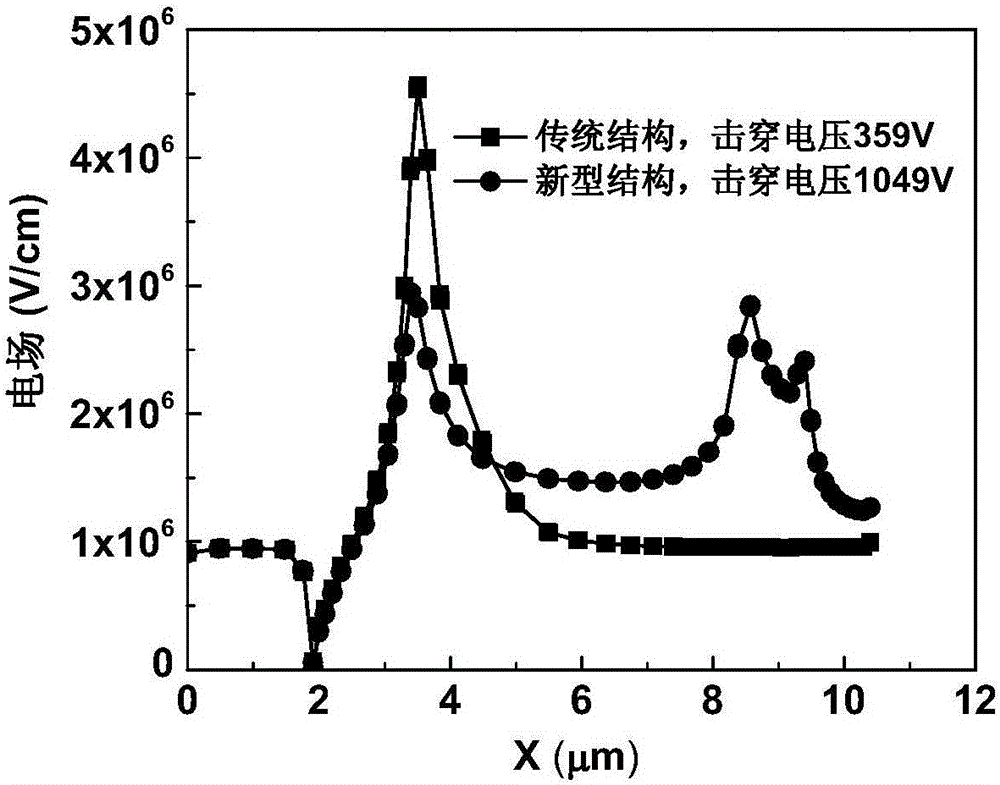

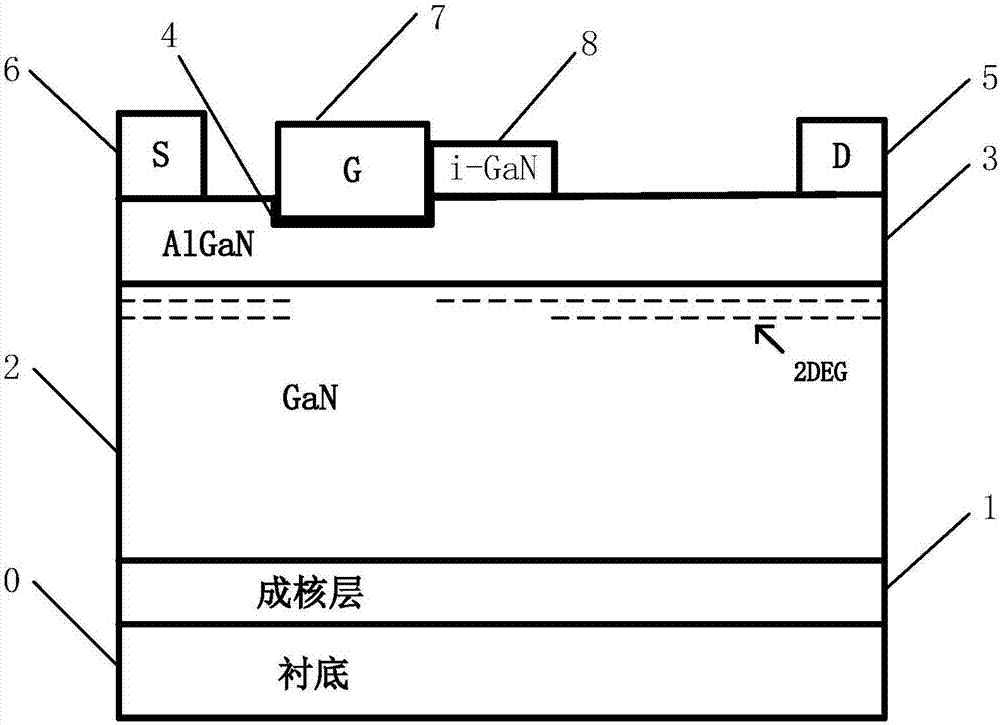

p-GaN enhanced AlGaN/GaN high-electron-mobility transistor

InactiveCN106783962AReduce high electric fieldReduce concentrationSemiconductor devicesElectric field modulationIntrinsics

The invention discloses a p-GaN enhanced AlGaN / GaN high-electron-mobility transistor with a partially intrinsic GaN cap layer. According to the transistor structure, the intrinsic GaN cap layer is introduced into a transistor grid electrode and the edge of a p type GaN medium layer of the transistor grid electrode, the two-dimensional electron gas concentration of a conducting channel in the area can be reduced by means of the intrinsic GaN cap layer, and the electric field modulation effect is achieved. A new electric field peak is generated, so that the high electric field of the grid edge is reduced, and an electric field on the surface of the transistor is distributed more evenly. Compared with a traditional p-GaN enhanced structure, the breakdown voltage and reliability of the novel structure are obviously improved.

Owner:XIDIAN UNIV

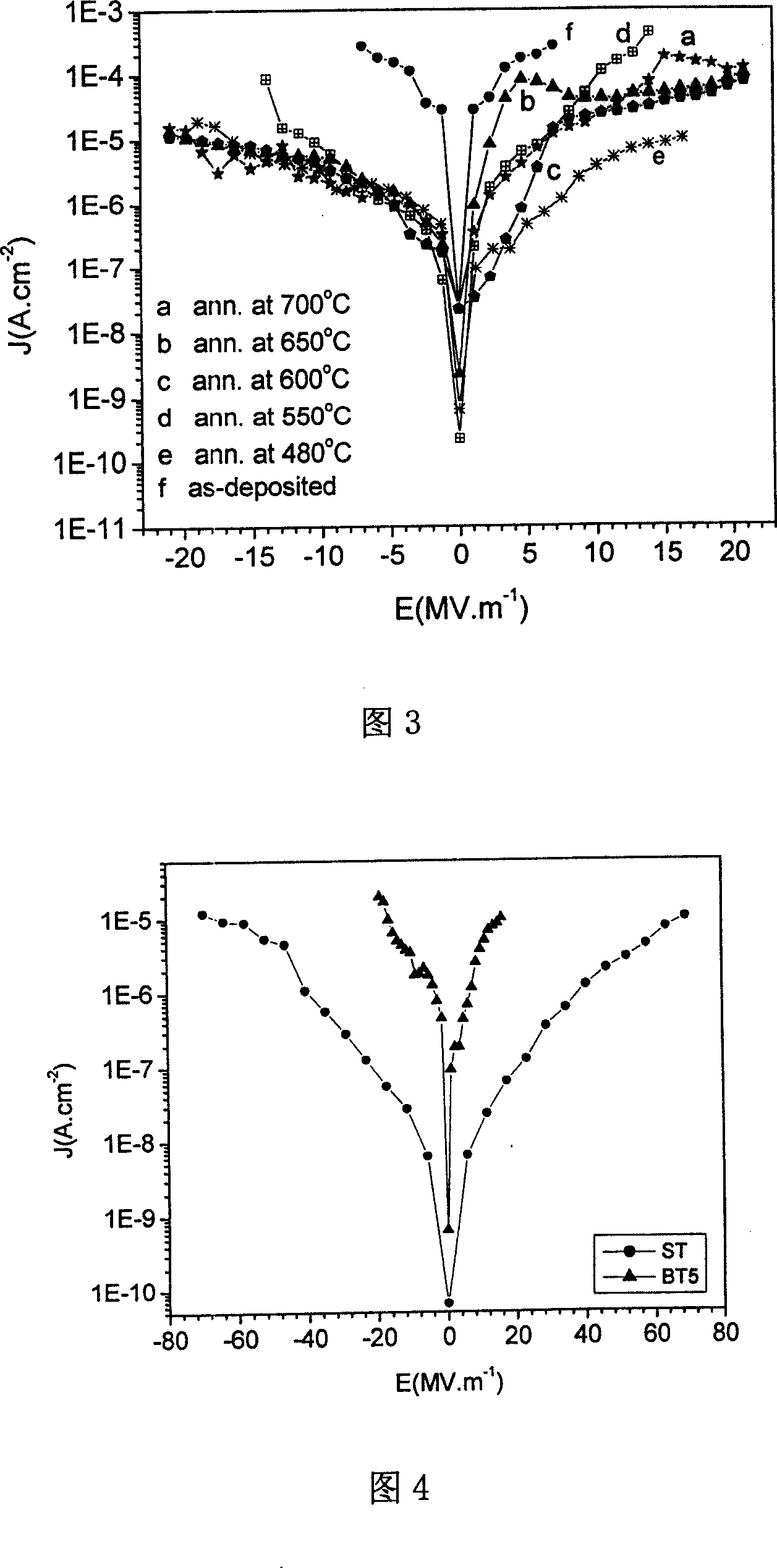

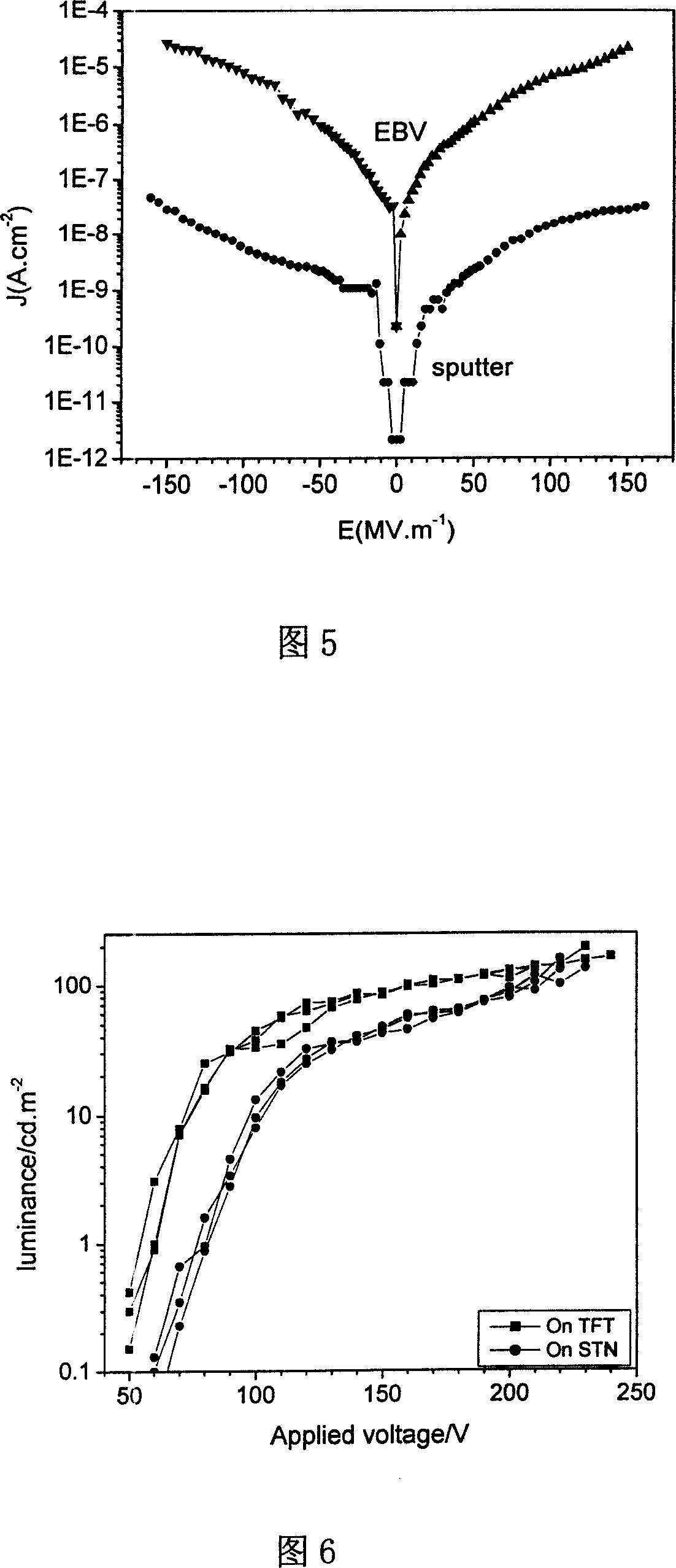

Inorganic EL display insulation media and its making method

InactiveCN101123282AReduce the driving voltageHigh initial ignition field strengthSolid-state devicesVacuum evaporation coatingComposite filmRadio frequency magnetron sputtering

An inorganic electroluminescent display insulating medium and the manufacturing method comprise: a multi-layer composite thin film A1203 / Ti02 and a AlxTiyOz thin film are manufactured as the medium layer on the ZnS:Mn ACTFEL device through electron beam evaporation method; Bati03 and SrTi03 thin films as the lower medium layer or the electric injection layer of ZnS:Mn ACTFEL device are manufactured and the follow-up annealing temperature of the BaTi03 thin film is reached through the electron evaporation method. The thin films are compared with the SrTi03 and Ba0.55Sr0.5Ti03 thin films manufactured through the traditional sputtering method. The invention optimizes the technique environment of pulse reactive sputtering A1203 thin film, comprising the power, pressure and oxygen content, and is appied to the ZnS:Mn four-pixel devices and the two-inch 128*64 matrix, obtaining better brightness effect. Mediums used in manufacturing the devices comprise Ba0.5Sr0.5TiO3 question mark SrTiO3 question mark BaTiO3 question mark HfO2 question mark Al2O3 question mark Ta2O5 question mark ZrO2 thin films by electron beam evaporation, radio frequency magnetron sputtering or impulse reactive sputtering.

Owner:INESA ELECTRON

Strontium titanate-based ceramic material with high energy storage density and low dielectric loss and preparation method thereof

The invention discloses a strontium titanate-based ceramic material with high energy storage density and low dielectric loss and a preparation method thereof. The method comprises the following steps: preparing materials according to a chemical formula which is expressed as (1-x)SrTiO[3-x]Bi0.48La0.02Na0.48Li0.02Ti0.98Zr0.02O3, mixing uniformly to obtain raw material powder, uniformly mixing organic solvents and emulsifiers, then adding the raw material powder, adhesives, dispersants and plasticizers, mixing uniformly, carrying out tape casting, then cutting and stacking, then pressurizing, discharging glue and sintering to obtain the strontium titanate-based ceramic material with high energy storage density and low dielectric loss. The ceramic material is simple in preparation process and mature in preparation technique, and is suitable for industrial production; the energy storage density calculated on the basis of ferroelectric hysteresis loop is 1.98-2.59j / cm<3>, the energy storage efficiency is 69-87%, and the electric field intensity is 200kV / cm or more; the ceramic material is excellent in energy storage characteristic and low in dielectric loss.

Owner:SHAANXI UNIV OF SCI & TECH

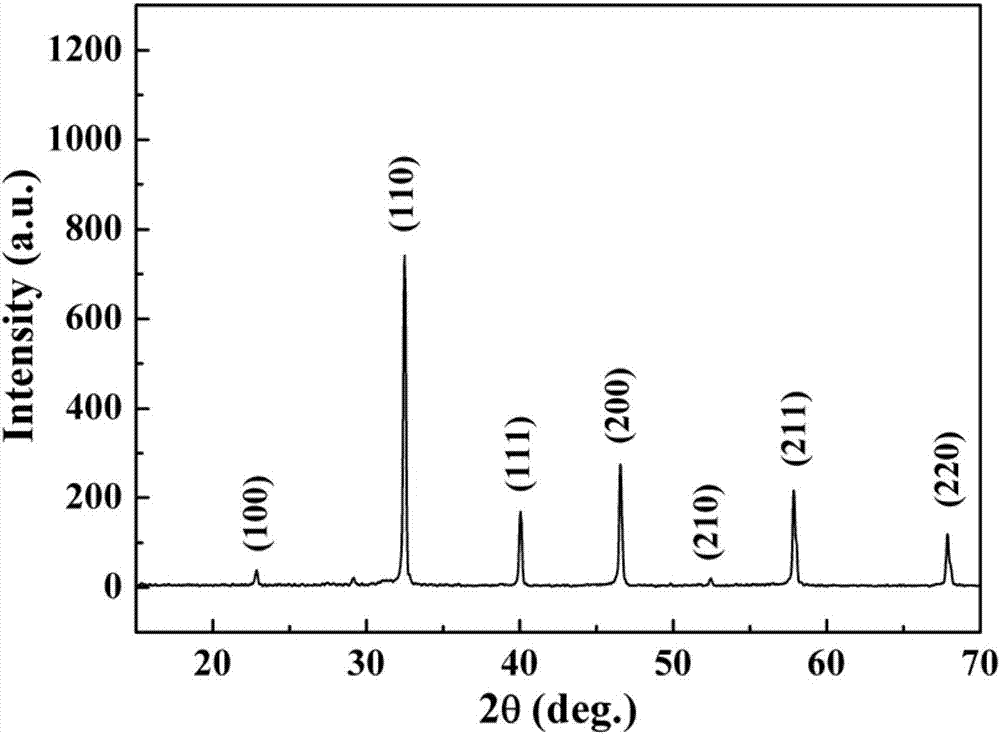

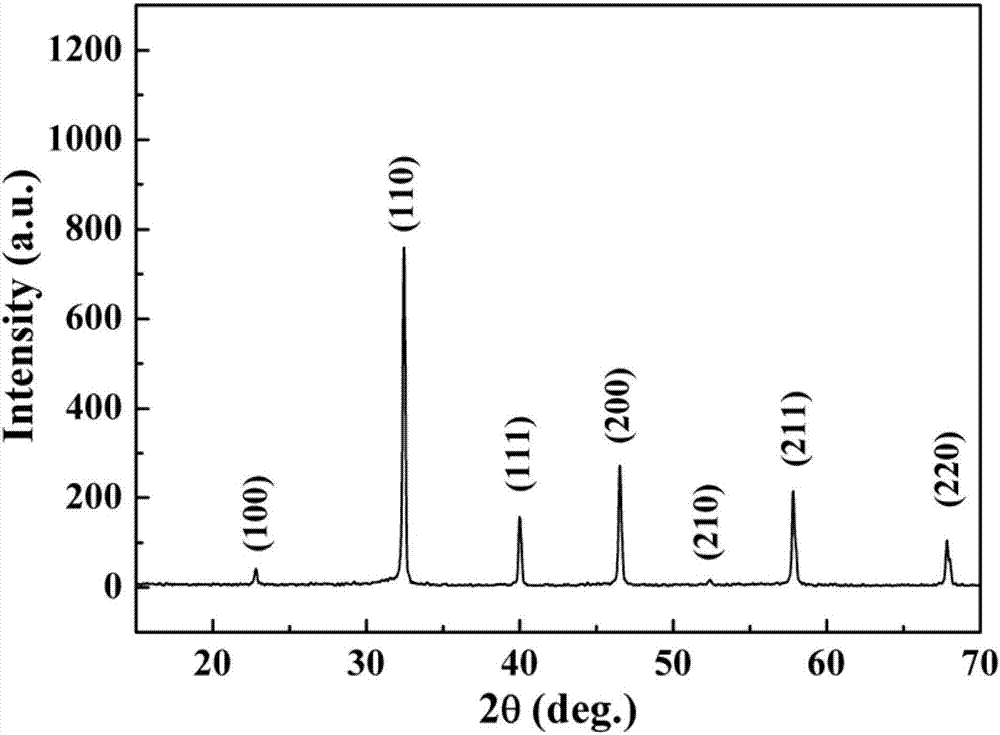

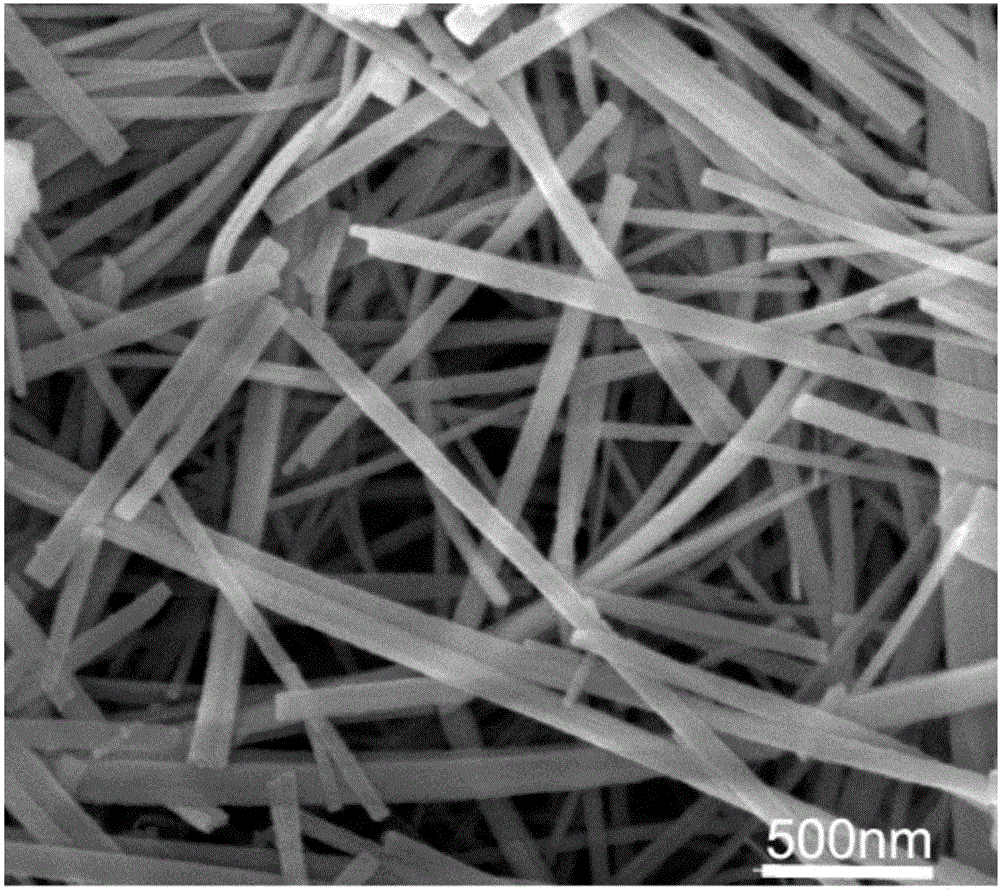

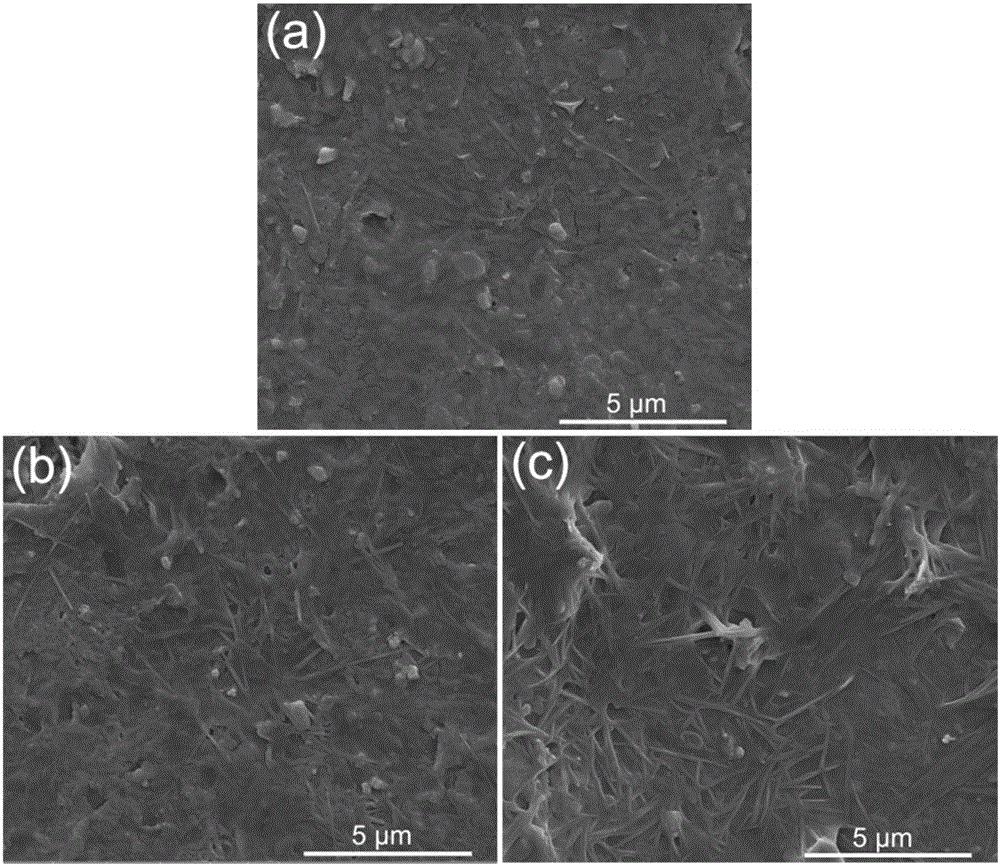

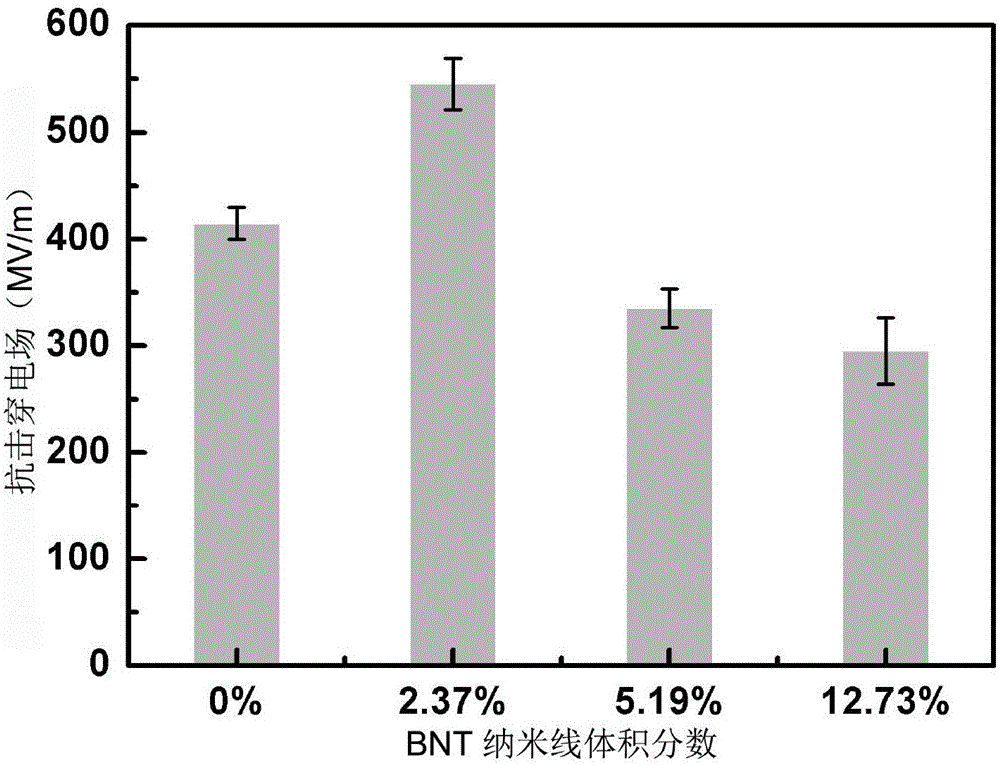

BNT-monocrystal-nanowire-based dielectric composite material and preparation method thereof

ActiveCN105860376AHigh dielectric constantHigh resistance to breakdown electric fieldMaterial nanotechnologyTitanatesDielectricNanowire

The invention discloses a BNT-monocrystal-nanowire-based dielectric composite material and a preparation method thereof. The preparation method comprises the following steps: preparing a BNT monocrystal nanowire material with the length-diameter ratio of 20-50 by a hydrothermal process, carrying out chemical modification by using dopamine, and compounding with a vinylidene fluoride-hexafluoropropylene P(VDF-HFP) copolymer to obtain the dielectric composite material. On the premise of implementing low ceramic phase content, the dielectric composite material obtains the anti-breakdown electric field of up to 458 kV / mm which is higher than the anti-breakdown electric field of 398 kV / mm of the straight polymer P(VDF-HFP), and implements the high energy density of 12.7 J / cm<3>.

Owner:云帆新材料集团有限公司

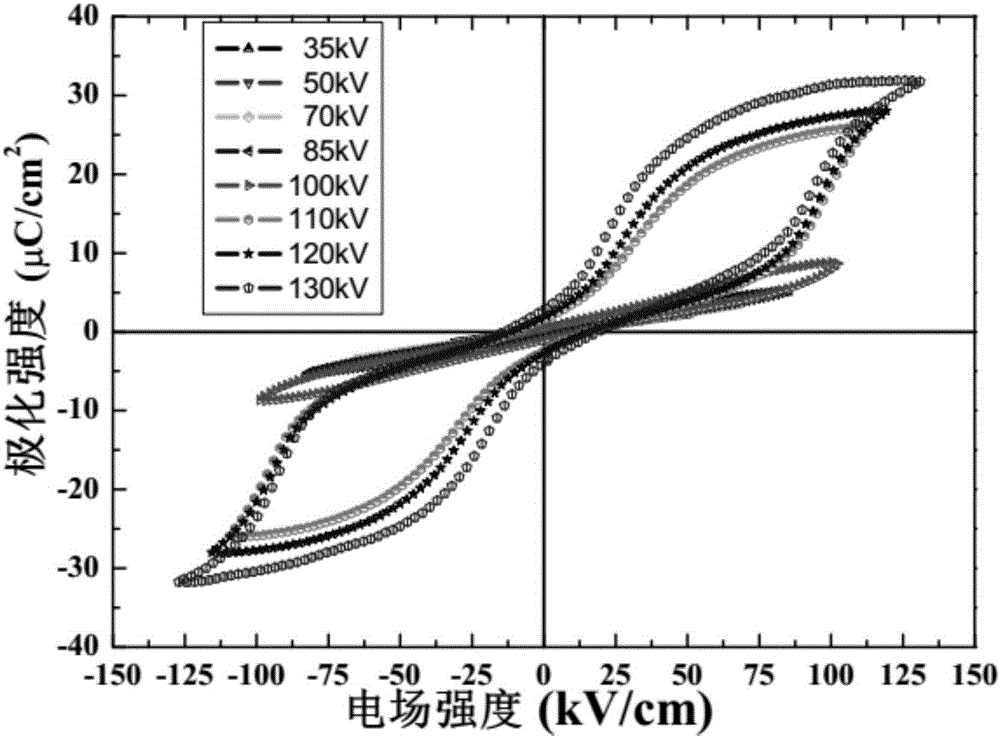

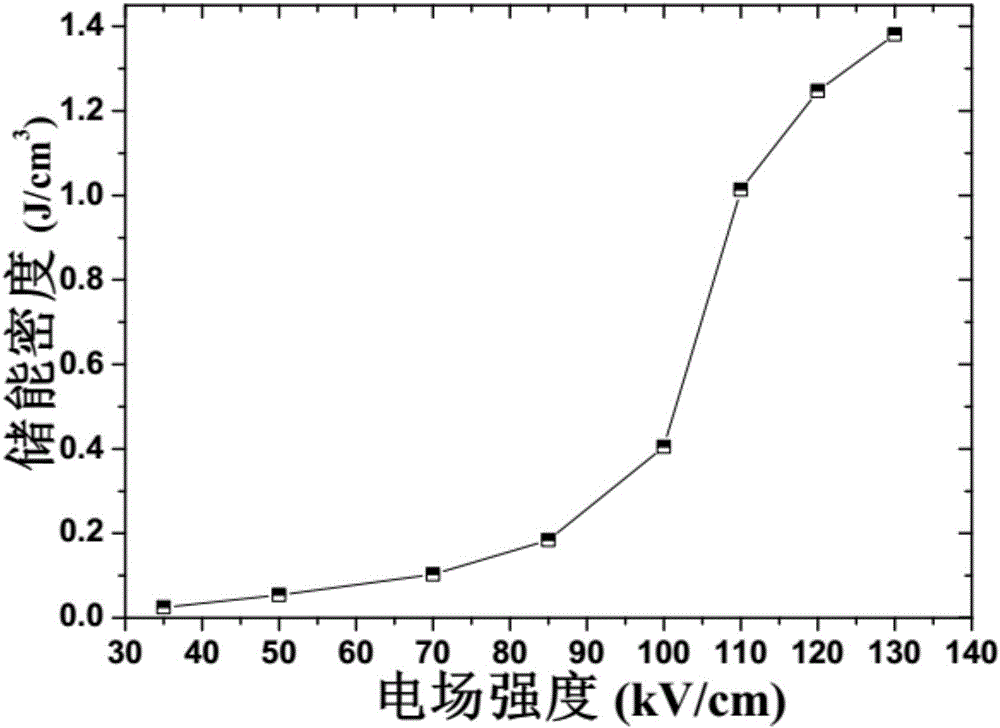

Antiferroelectric high-energy-density ceramic material and preparation method thereof

InactiveCN106699173AHigh energy storage densityHigh electric field induced polarizationFixed capacitor dielectricDielectricHigh energy

The invention relates to an antiferroelectric high-energy-density ceramic material and a preparation method thereof. The general formula of the composition is (1-x)PbHfO[3-x]PbMg0.5W0.5O3, wherein x represents the mol percent of PbMg0.5W0.5O3, and x=0.01-0.25. By adopting a two-step solid-phase sintering process to prepare the ceramic material, the composition is controlled, so that the critical electric field of the antiferroelectric ceramic is obviously lowered, and the withstand voltage strength is enhanced, thereby implementing high-energy-density application in the room temperature environment. The high-energy-density ceramic capacitor dielectric material has the advantages of low sintering temperature, high withstand voltage strength (up to 130 kV / cm) and high energy density (up to 1.39 J / cm<3>), can be used for preparing high-energy-density multilayer ceramic capacitors, and has favorable application prospects. The antiferroelectric high-energy-density ceramic material has the characteristics of simple technique and stable performance, and is suitable for industrial popularization.

Owner:XI AN JIAOTONG UNIV

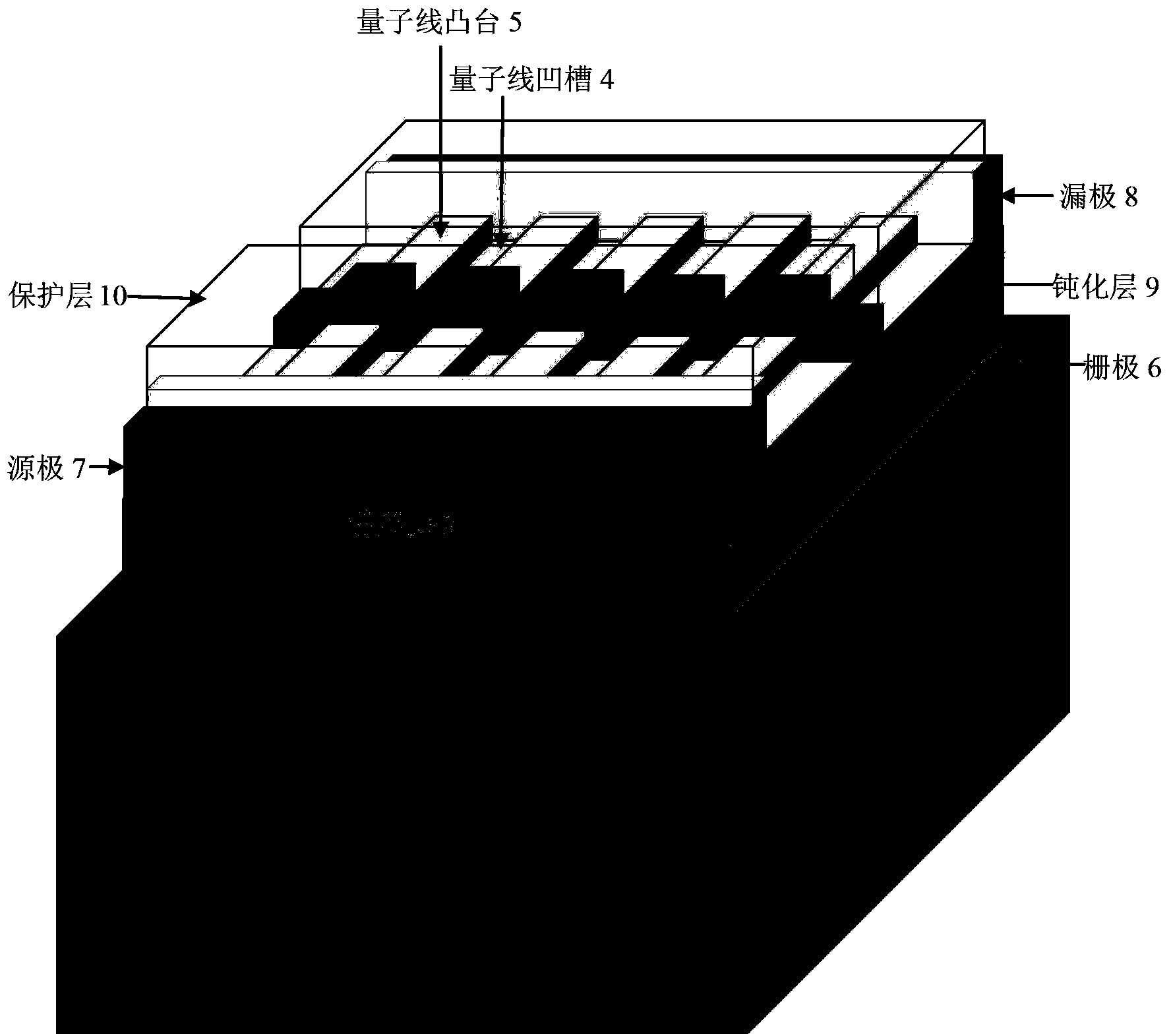

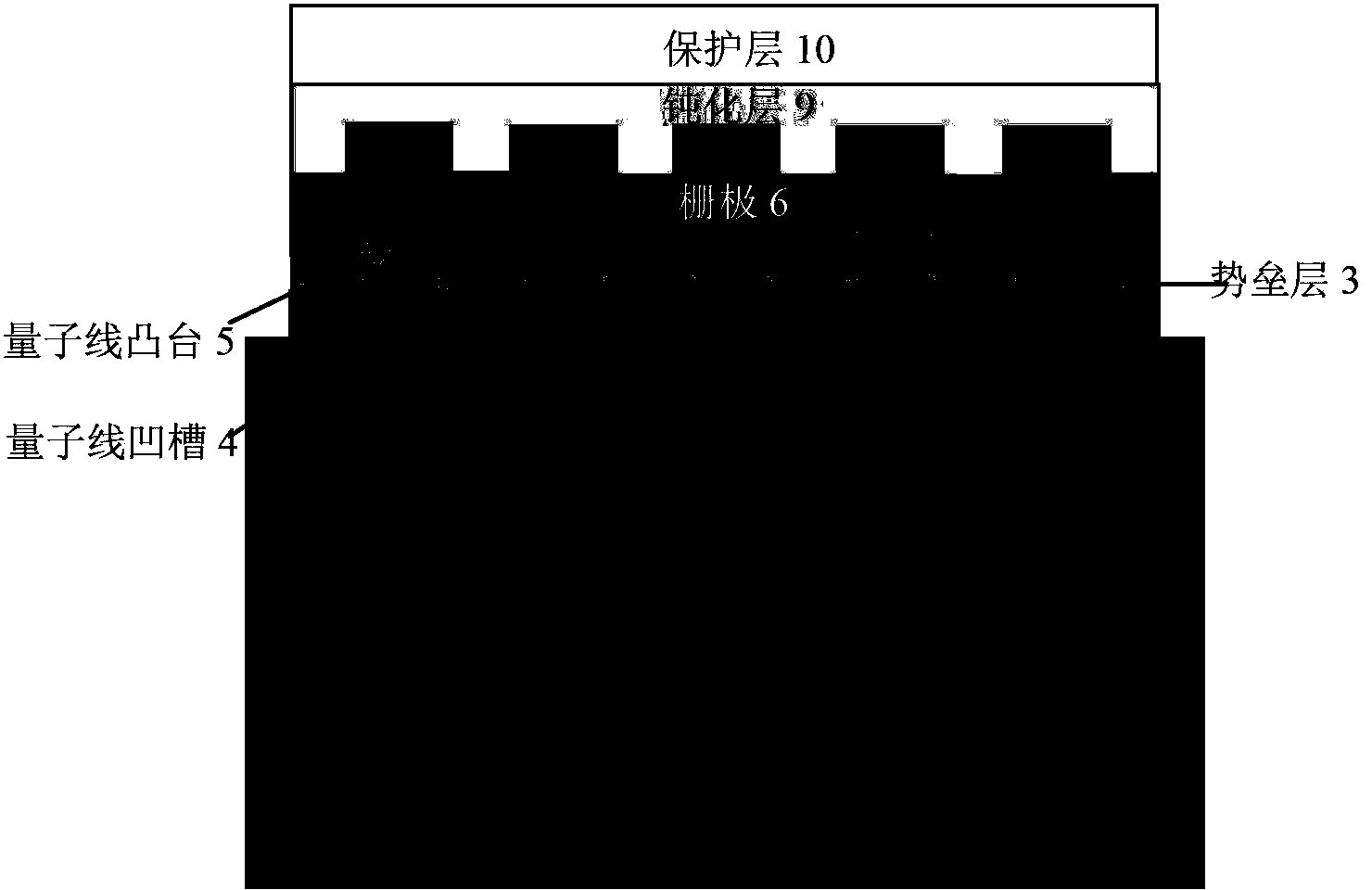

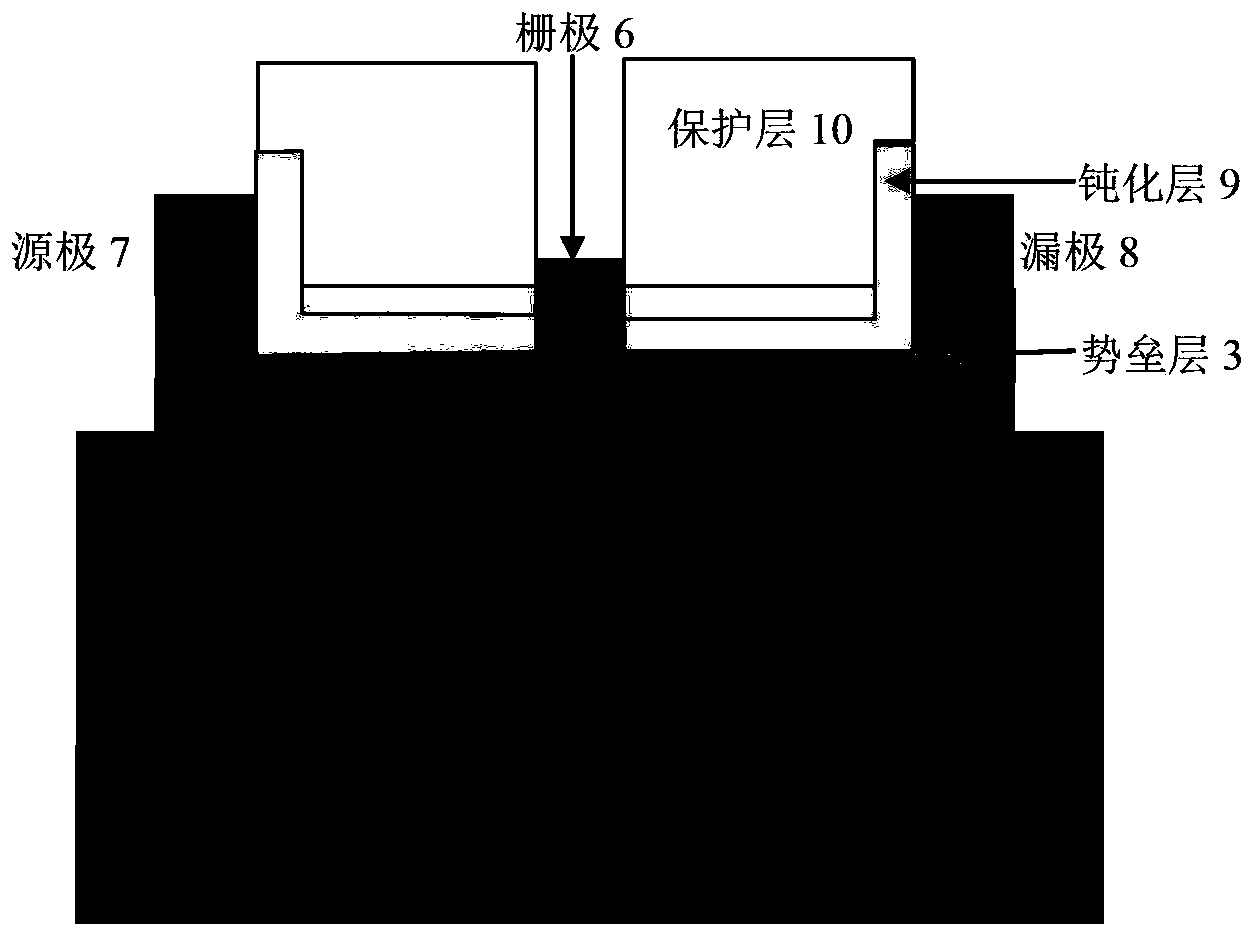

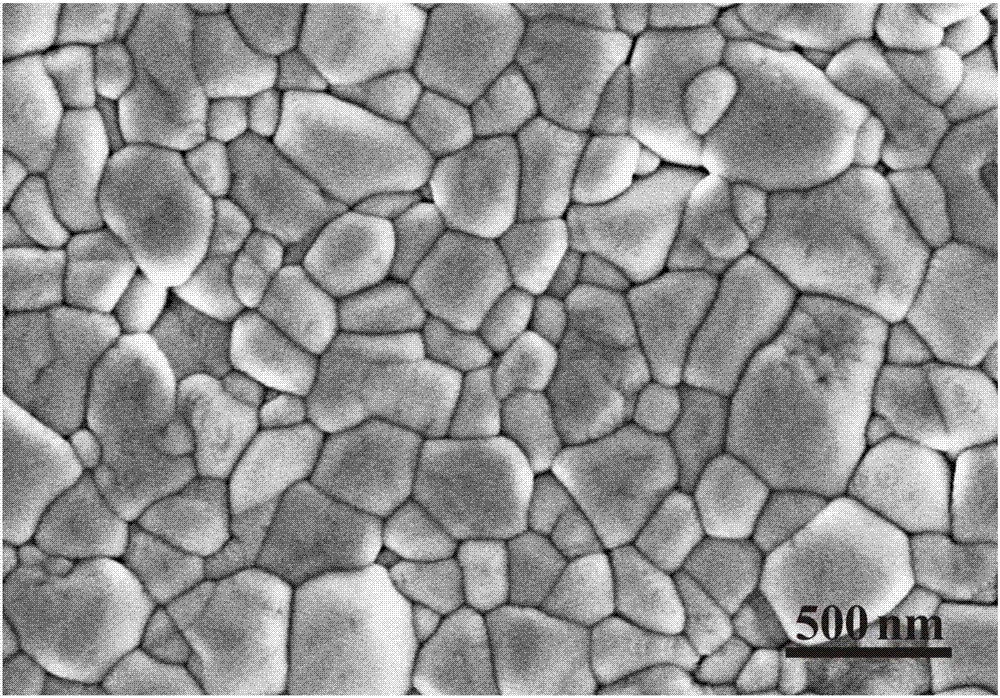

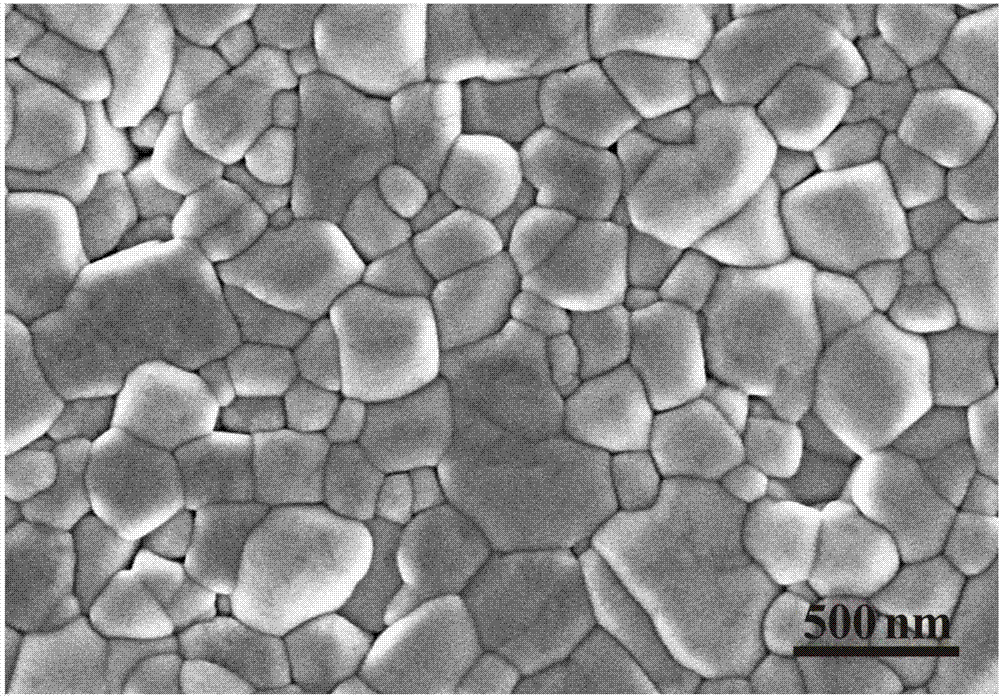

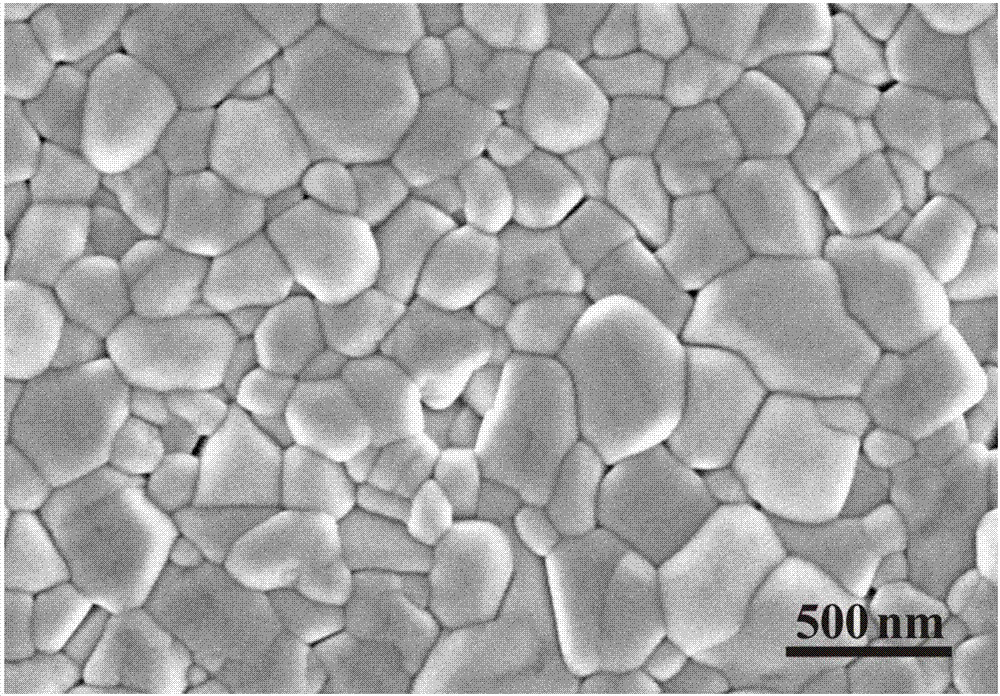

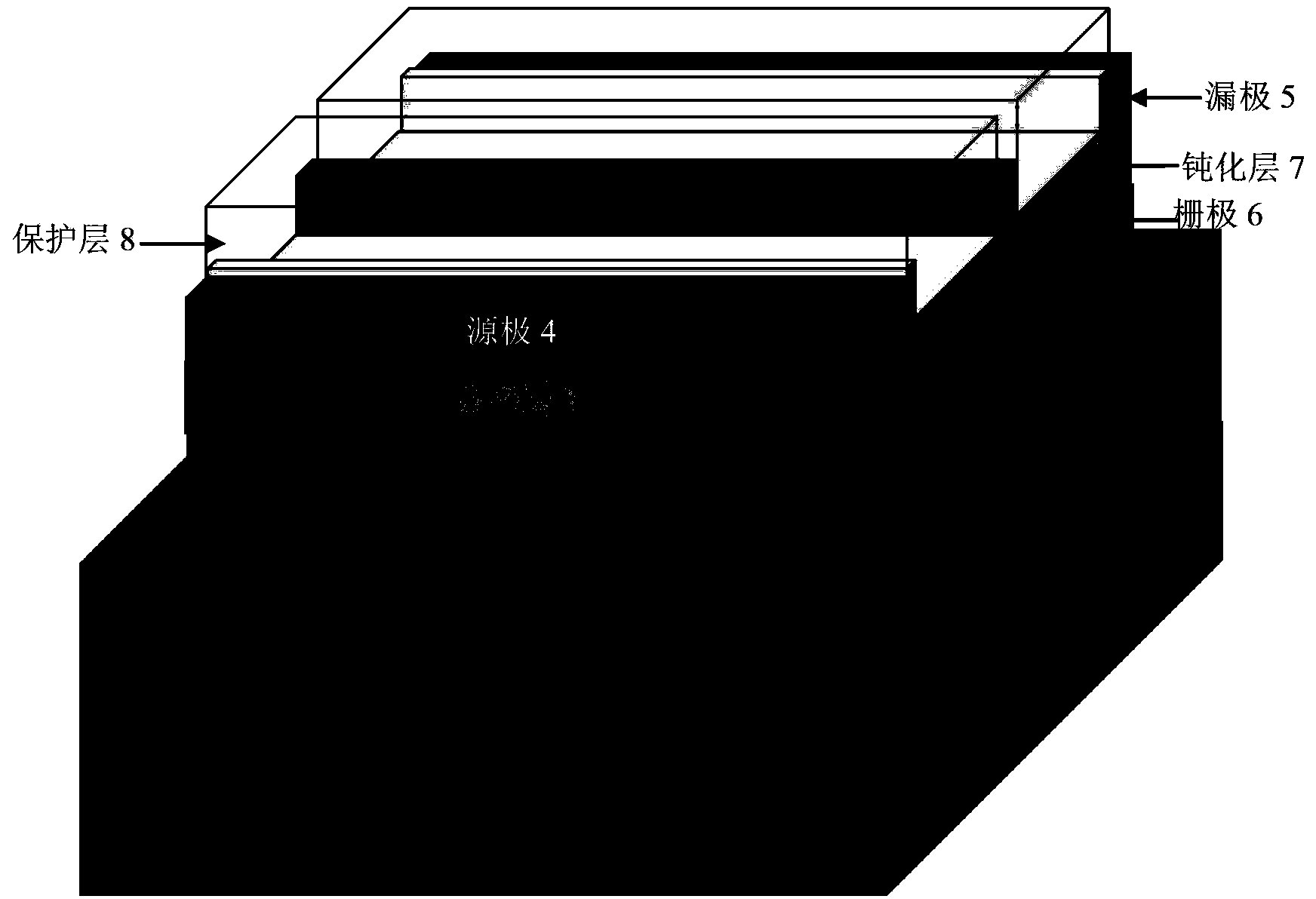

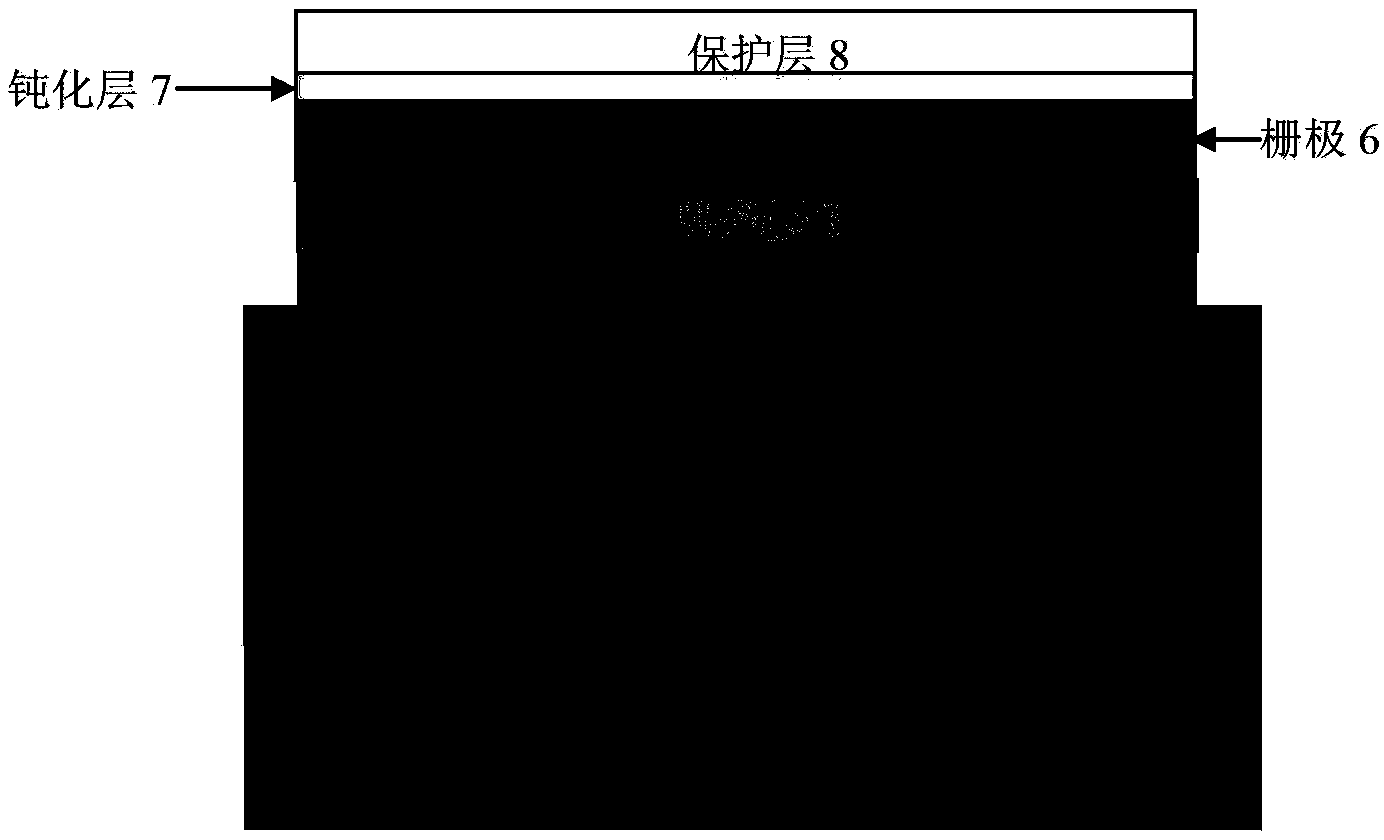

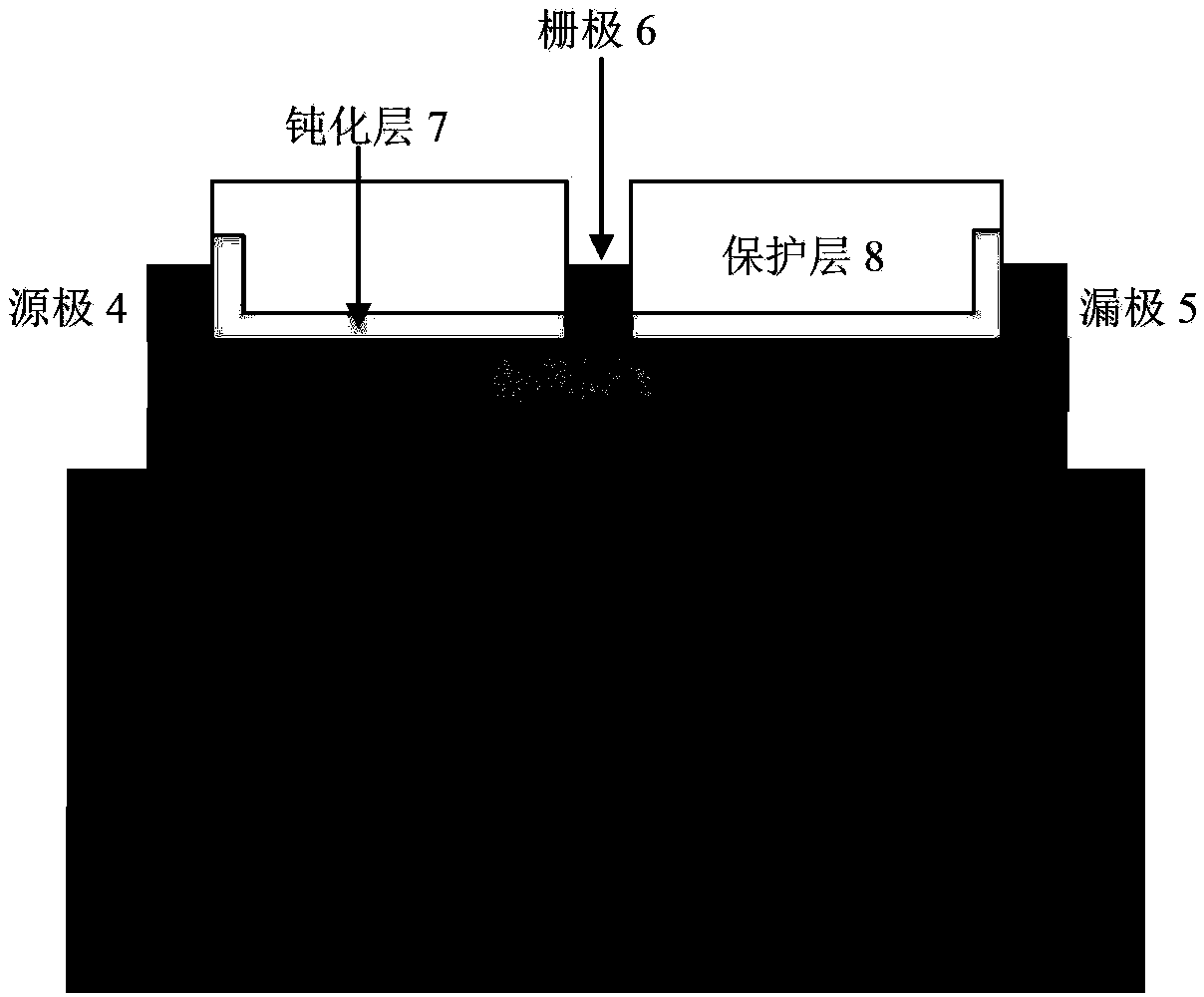

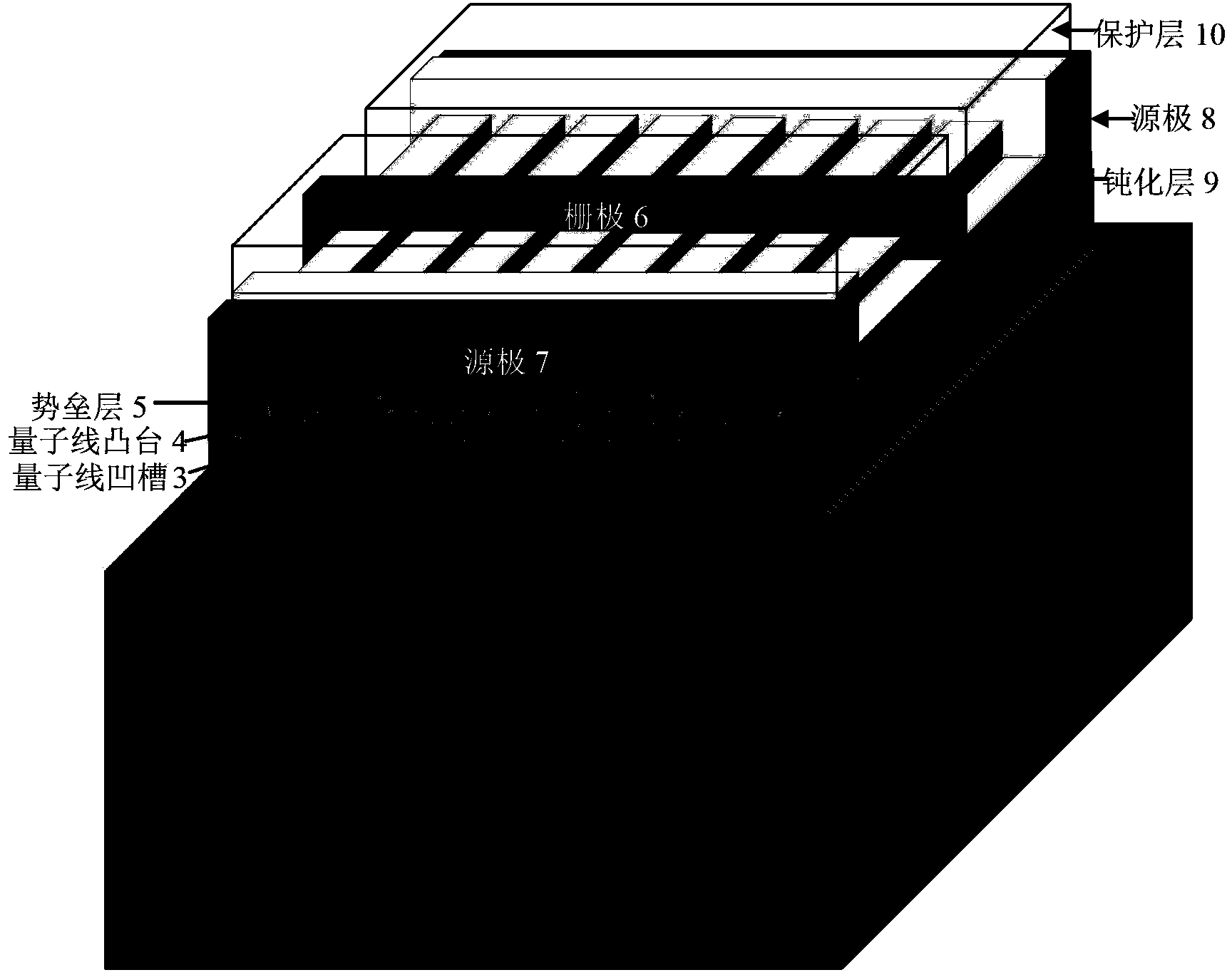

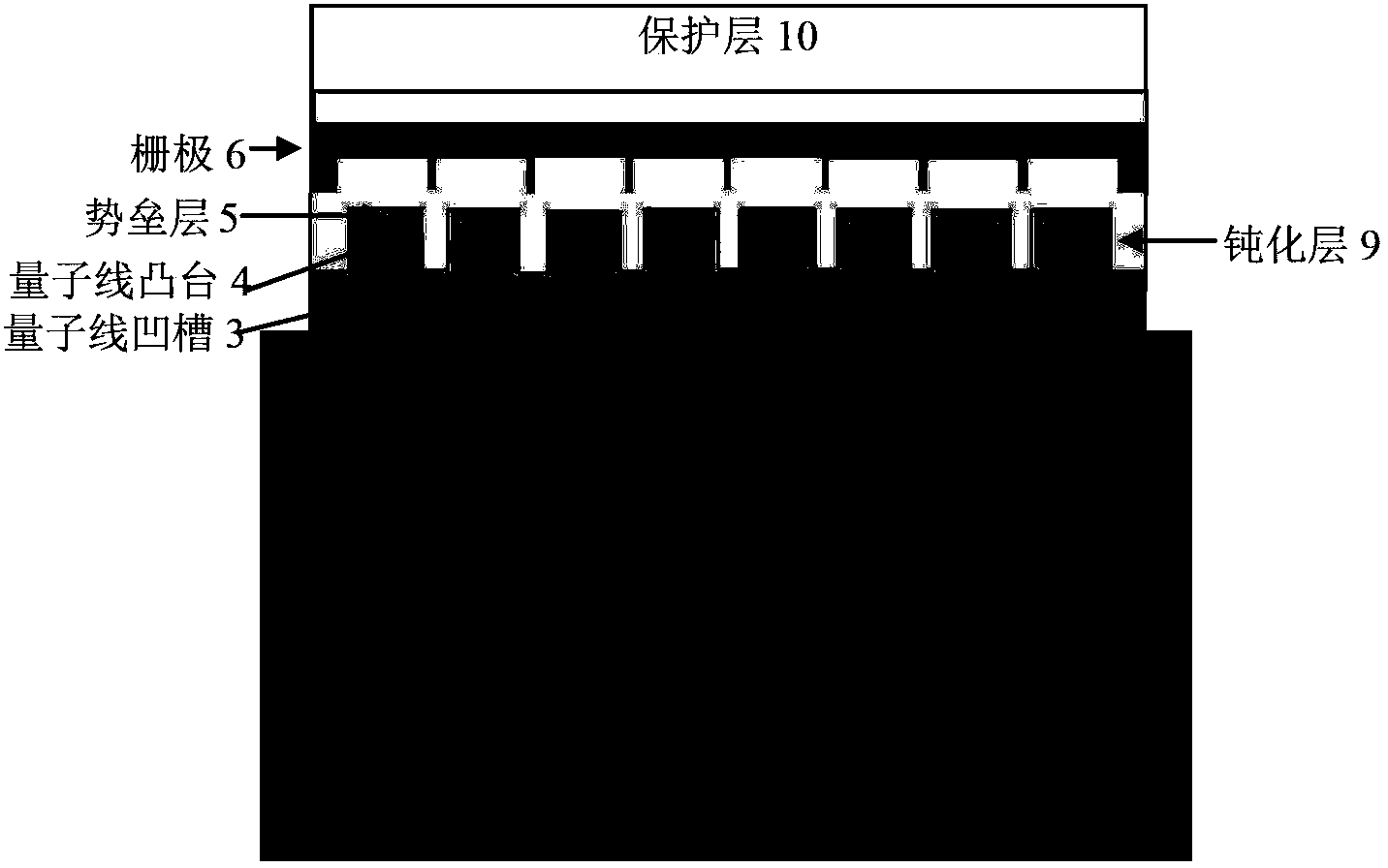

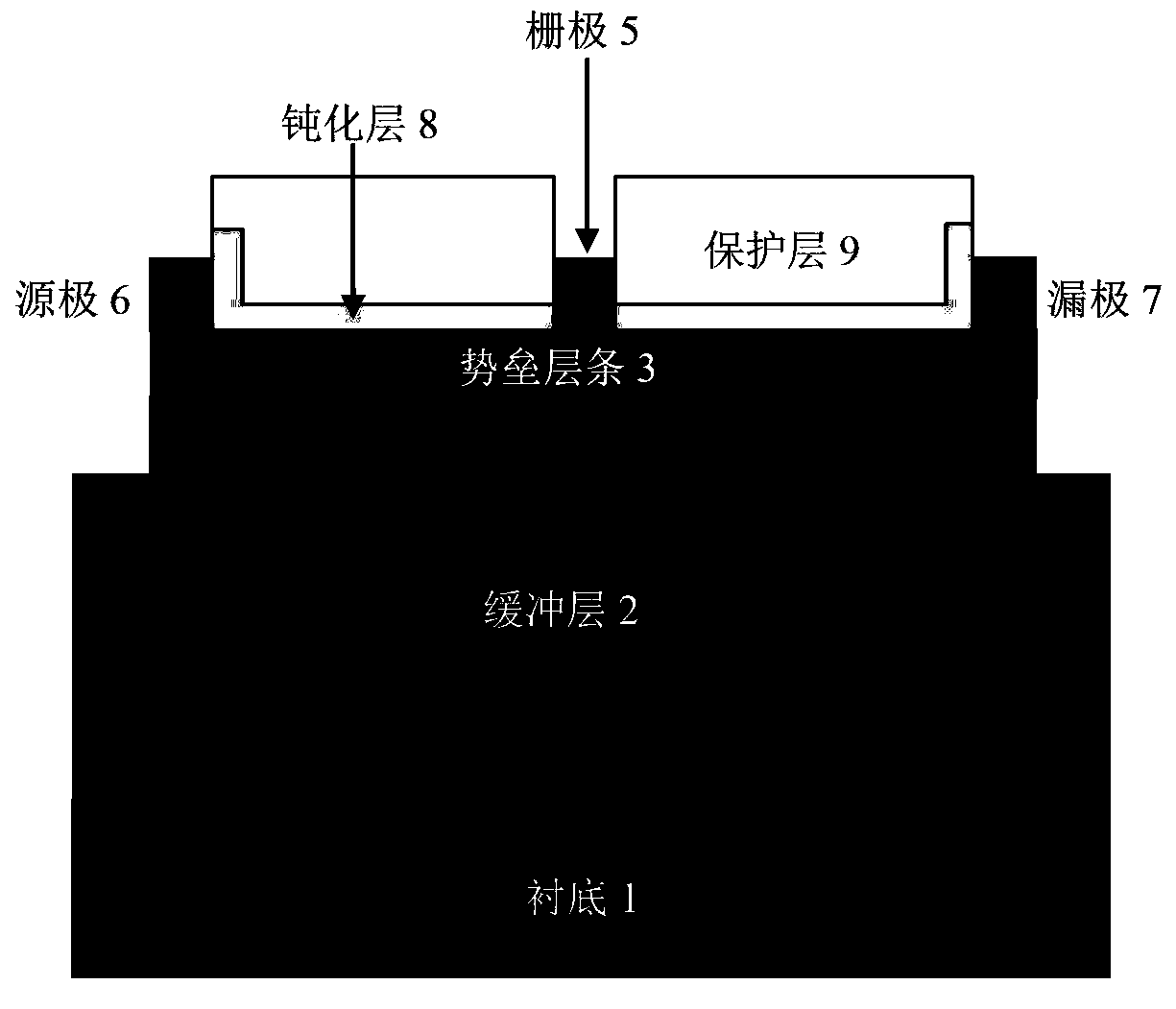

Etching-based one-dimensional electron gas GaN-based HEMT (high electron mobility transistor) device and preparation method thereof

ActiveCN103367428AImprove high temperature and high pressure characteristicsImprove featuresSemiconductor/solid-state device manufacturingSemiconductor devicesHigh pressureFrequency characteristic

The invention discloses an etching-based one-dimensional electron gas GaN-based HEMT (high electron mobility transistor) device and preparation method thereof, and mainly solves the problems that the conventional one-dimensional electron gas device has low high-temperature and high-pressure characteristics, frequency characteristics and power characteristics. The device comprises a substrate, a buffering layer, a potential barrier layer, a passivation layer and a protection layer from top to bottom; the two ends of the potential barrier layer are respectively a source and a drain; the passivation layer is positioned on the potential barrier layer between the source and the drain; a gate groove is formed in the passivation layer; and a gate is arranged in the gate groove. A plurality of quantum wire grooves which are arranged uniformly are etched on the potential barrier layer so as to obtain a plurality of quantum wire bosses with the width of nanoscale; and one-dimensional electron gas is formed in heterogenous junctions of the quantum wire bosses. The buffering layer adopts GaN; and the potential barrier layer adopts AlGaN. Compared with a Si-based device and a GaAs-based device, the etching-based one-dimensional electron gas GaN-based HEMT device has high high-temperature and high-pressure characteristics, frequency characteristics and power characteristics, and can be used for manufacturing ultrahigh speed low-power consumption one-dimensional electron gas devices.

Owner:云南凝慧电子科技有限公司

Lead-free ceramic material with high energy storage density and high energy storage efficiency and preparation method thereof

The invention relates to a lead-free ceramic material with high energy storage density and high energy storage efficiency and a preparation method thereof. According to the method, firstly, proportioning is performed according to a chemical formula of Ba0.4Sr0.6TiO3-x(Bi2O3-B2O3-SiO2), wherein the x is the mass percent of Bi2O3-B2O3-SiO2, and the x is greater than or equal to 3 weight percent and is smaller than or equal to 12 weight percent; through ball milling and drying, raw material powder is obtained; the obtained raw material powder is pressed into sheets; sintering is performed at 1300 to 1350 DEG C; the lead-free ceramic material with high energy storage density and high energy storage efficiency can be obtained. The lead-free ceramic material has the advantages that the preparation process is simple and stable, and is suitable for industrial production; the energy storage characteristic is excellent; the energy storage density calculated based on a ferroelectric hysteresis loop is 1.73 to 1.98J / cm<3>; the energy storage efficiency is 90 percent or higher.

Owner:SHAANXI UNIV OF SCI & TECH

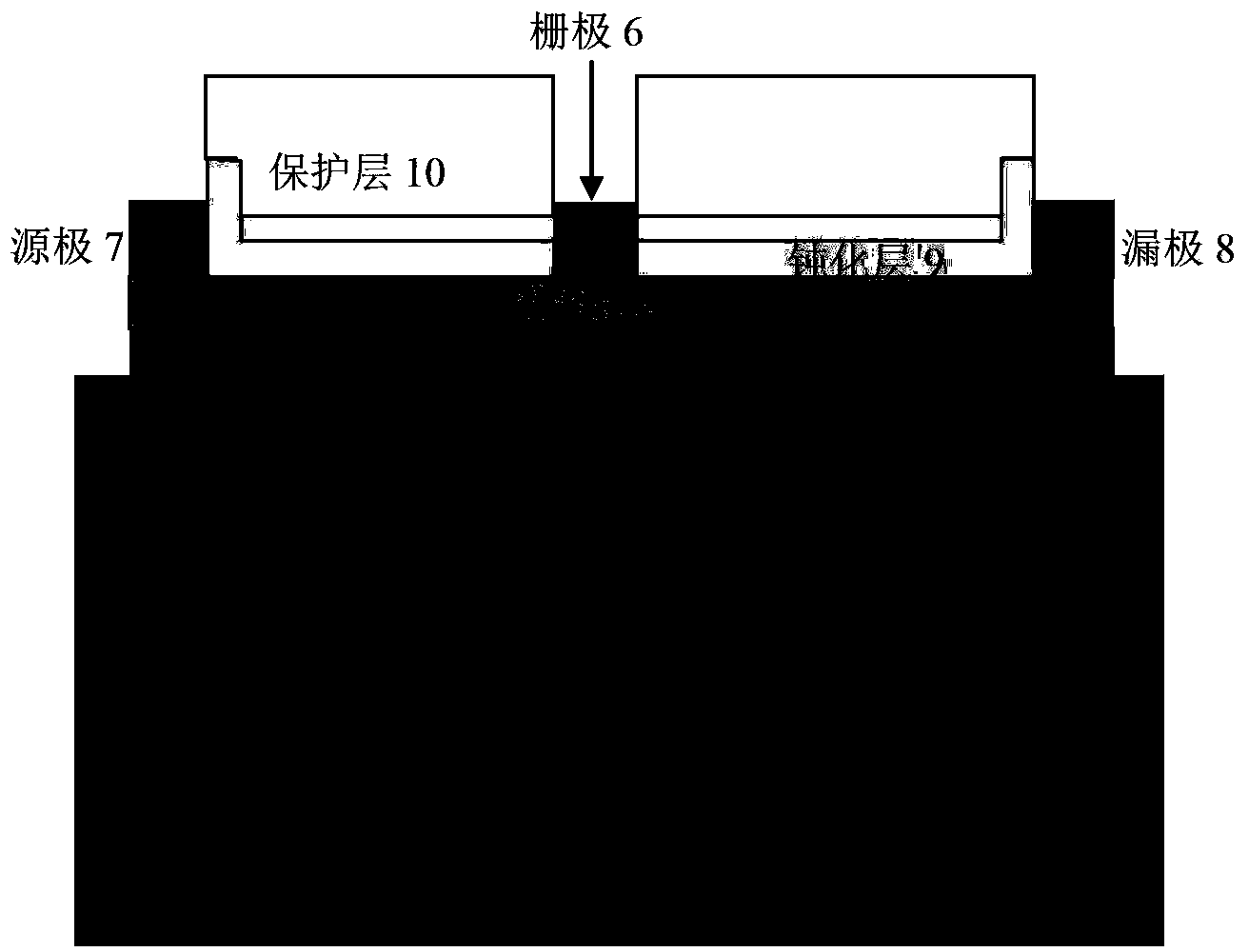

Ion-implanted one-dimensional electron gas GaN-based HEMT (high electron mobility transistor) device and preparation method

ActiveCN103367416AHigh electron mobilityIncrease electron concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesUltra high speedHigh pressure

The invention discloses an ion-implanted one-dimensional electron gas GaN-based HEMT (high electron mobility transistor) device and a preparation method. The problems of poorer high-temperature high-voltage characteristics, frequency characteristics and power characteristics of the conventional one-dimensional electron gas device are mainly solved. The device comprises a substrate, buffer layer, a potential barrier layer, a passivation layer and a protective layer from bottom to top, wherein a source and a drain are arranged at two ends on the potential barrier layer respectively; the passivation layer is positioned on the potential barrier layer between the source and the drain; a gate trough is formed in the passivation layer, and a gate is arranged in the gate trough; the buffer layer is made from GaN, and the potential barrier layer is made from AlGaN; anions are implanted into local areas on the potential barrier layer, and the areas where the anions are implanted are a plurality of spaced strips; the widths of areas where the anions are not implanted between the strips are at a nanometer order of magnitude, and a one-dimensional electron gas is formed in heterogeneous junctions below the areas where the anions are implanted. Compared with Si-based and GaAs-based devices, the device has good high-temperature high-voltage characteristics, good frequency characteristics and good power characteristics, and a one-dimensional electron gas device with super-high speed and low power consumption can be manufactured.

Owner:陕西半导体先导技术中心有限公司

Strontium titanate based lead-free high-pressure-resistant ceramic energy storage material and preparation method thereof

ActiveCN107445616ASimple preparation processThe preparation process is matureHysteresisElectrical field strength

The invention discloses a lead-free ceramic material with high energy storage density and energy storage efficiency and a preparation method thereof. The preparation method comprises the following steps of mixing materials according to a chemical formula (1-x)SrTiO3-x(0.93Bi0.5Na0.5TiO3-0.07Ba0.94La0.04Zr0.02Ti0.98O3), uniformly mixing, so as to obtain raw-material powder, uniformly mixing an organic solvent and an emulsifier, then adding the raw-material powder, a binder, a dispersant and a plasticizer, then uniformly mixing, carrying out tape casing, and then cutting, superposing, pressurizing, discharging glue and sintering, so that a strontium titanate based lead-free high-pressure-resistant ceramic energy storage material is obtained. The ceramic material provided by the invention is simple in preparation process, mature in technique, suitable for industrialized production and excellent in energy storage property, and has the energy storage density of 1.80J / cm<3> to 2.83J / cm<3>, the energy storage efficiency of 74 to 87 percent and the electric field intensity of 175kV / cm to 326kV / cm, which are calculated based on an electric hysteresis loop.

Owner:SHAANXI UNIV OF SCI & TECH

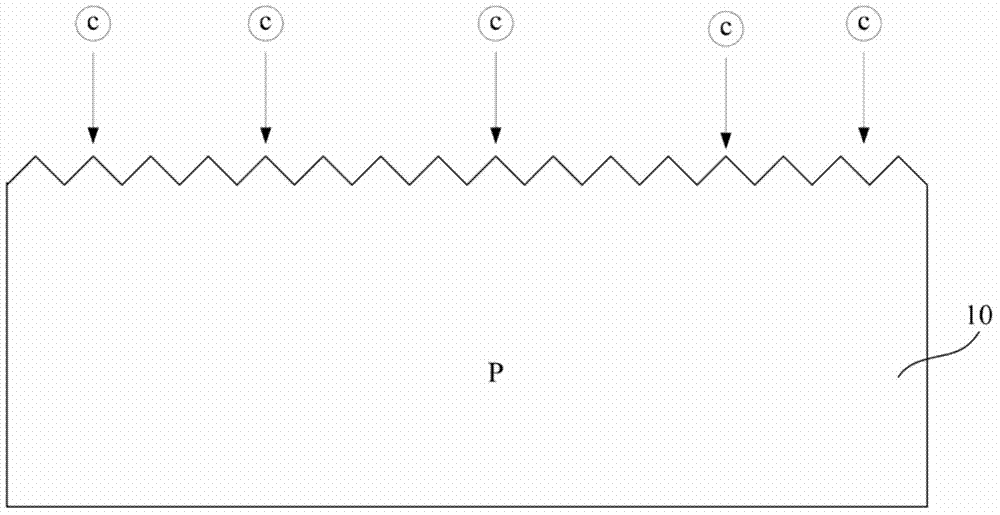

Crystalline silicon solar cell having doped silicon carbide layer and manufacturing method thereof

InactiveCN104282777AGood electronic characteristicsBest Radiation HardnessFinal product manufacturePhotovoltaic energy generationElectrical resistance and conductancePhotoelectric conversion

The present invention discloses a crystalline silicon solar cell having a doped silicon carbide layer and a manufacturing method thereof. The solar cell comprises: a semiconductor substrate having a roughened first surface; a doped silicon carbide layer arranged at the first surface and comprising a doping element; an anti-reflecting layer; a plurality of front electrodes arranged on the anti-reflecting layer and penetrating the anti-reflecting layer; and a back electrode layer arranged at a second surface of the semiconductor substrate. As the doped silicon carbide layer has doping reversed to the doping type of the semiconductor substrate and a silicon carbide element, the doped silicon carbide layer has the characteristics of low resistance and wide energy gap, so that the doped silicon carbide layer can be used as an emitter of the solar cell, in addition, the doped silicon carbide layer has low absorption for sunlight, so that quantity of light entering the semiconductor substrate can be increased, thereby improving photoelectric conversion rate of the solar cell.

Owner:NEO SOLAR POWER CORP

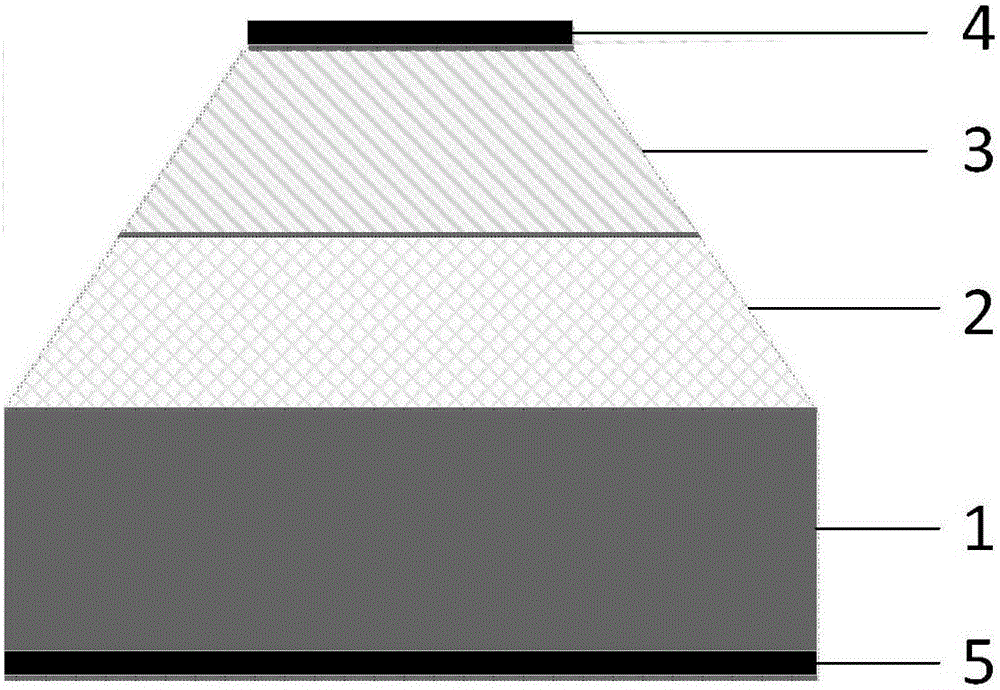

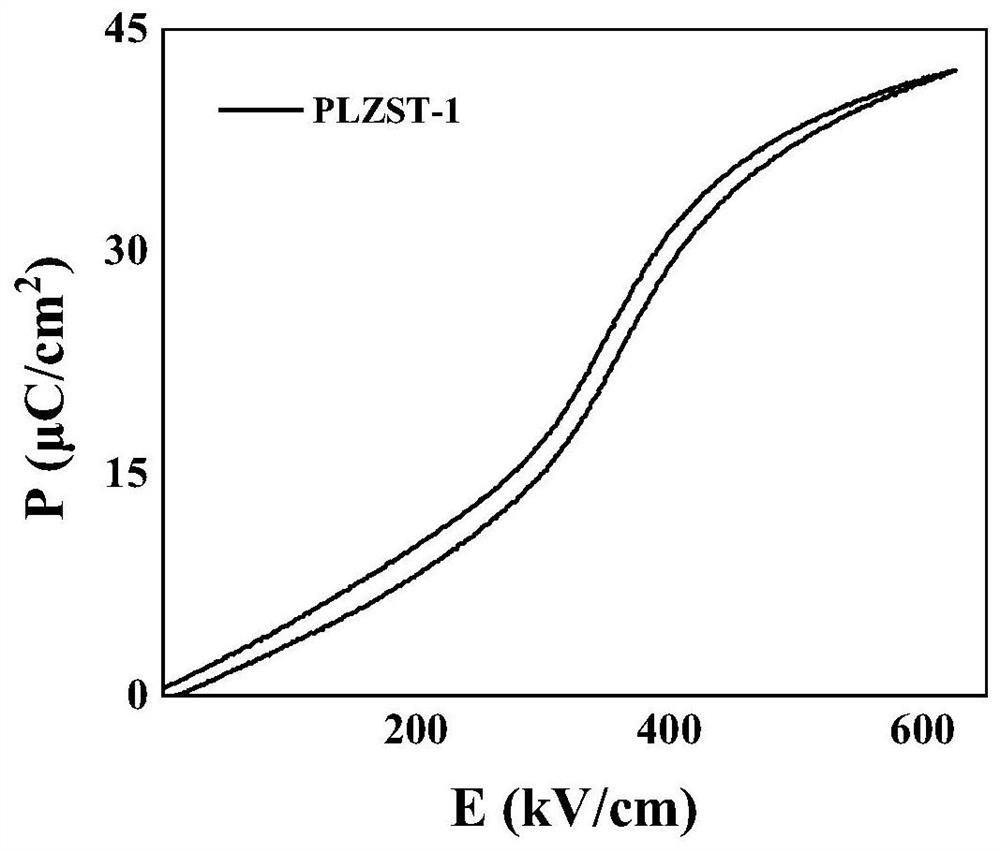

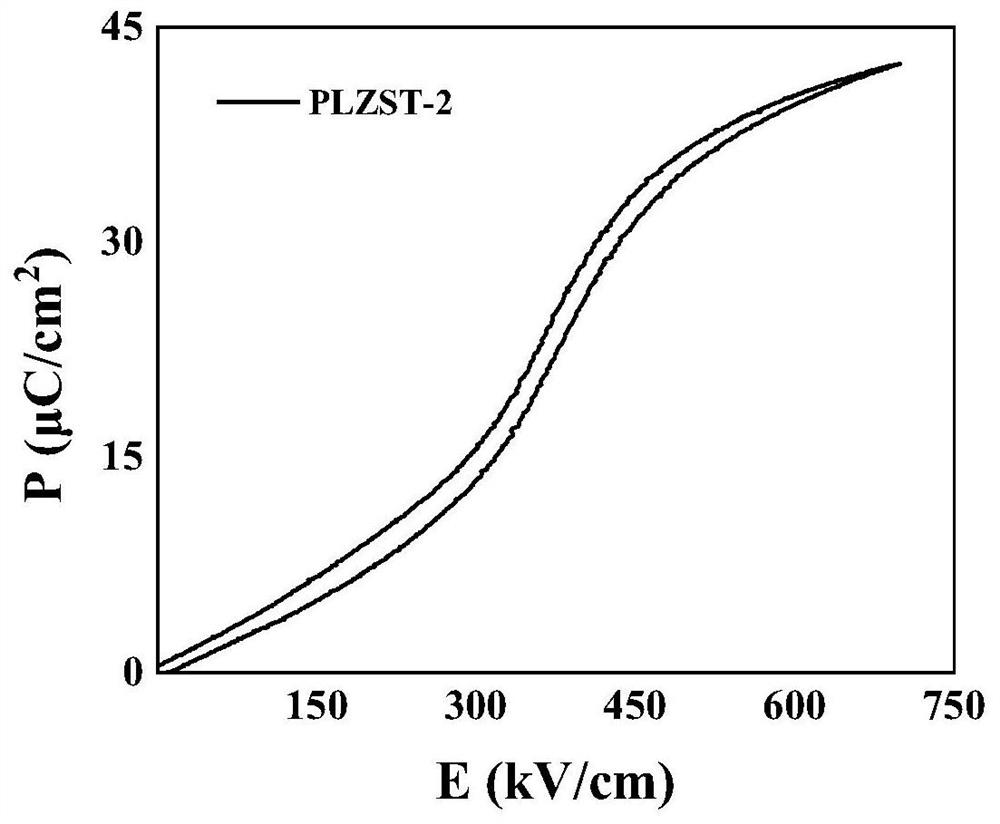

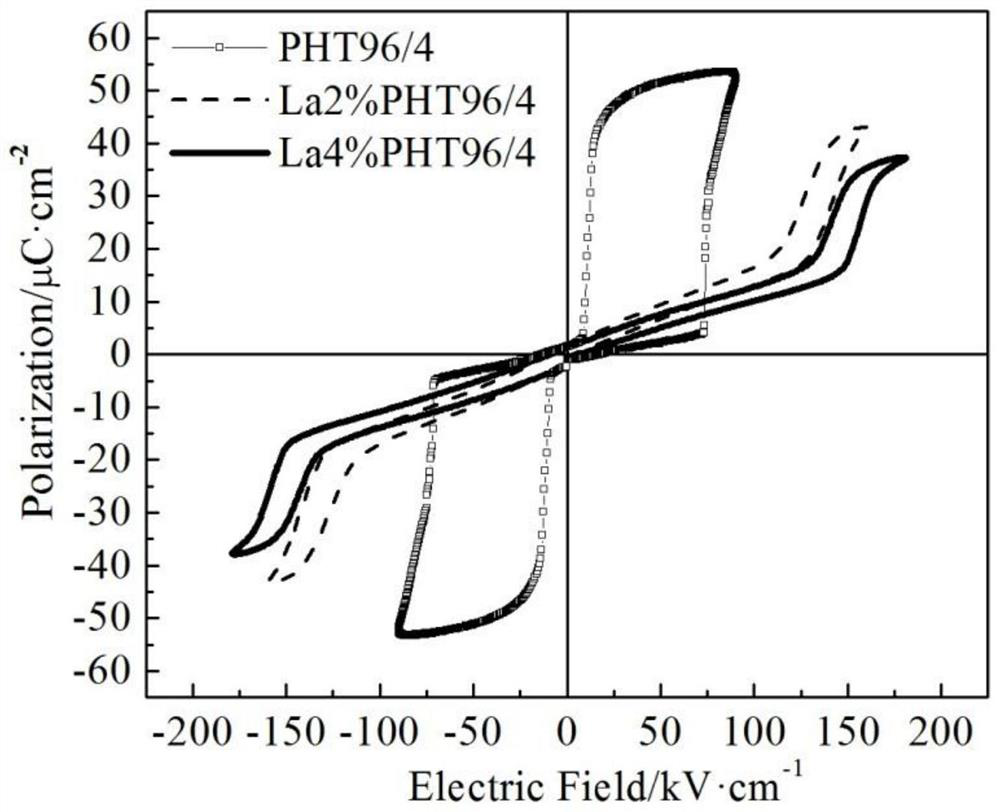

Antiferroelectric material and preparation method thereof, and capacitor containing antiferroelectric material

PendingCN111718194AStrong breakdown resistanceHigh energy storage densityThin/thick film capacitorFixed capacitor dielectricFilm capacitorHigh energy

The invention discloses an antiferroelectric material and a preparation method thereof, and a capacitor containing the antiferroelectric material. The antiferroelectric material includes an antiferroelectric body represented by a general formula (Pb<0.94>La<0.04>)(Zr<1-x-y>Sn<x>Ti<y>)O<3>, where x is greater than or equal to 0.3 and smaller than or equal to 0.5, and y is greater than or equal to 0.3 and smaller than or equal to 0.1. The antiferroelectric material can be used for manufacturing the energy storage capacitor. According to the lead lanthanum zirconate titanate stannate antiferroelectric thick-film capacitor prepared by a tape casting method disclosed by the invention, the ultrahigh energy storage efficiency of 90-95% can be achieved, and the capacitor also has relatively strongbreakdown resistance and high energy storage density, so a solid foundation is laid for researching and developing a dielectric energy storage capacitor with excellent energy storage performance; andthe capacitor has a very good application value.

Owner:INNER MONGOLIA UNIV OF SCI & TECH

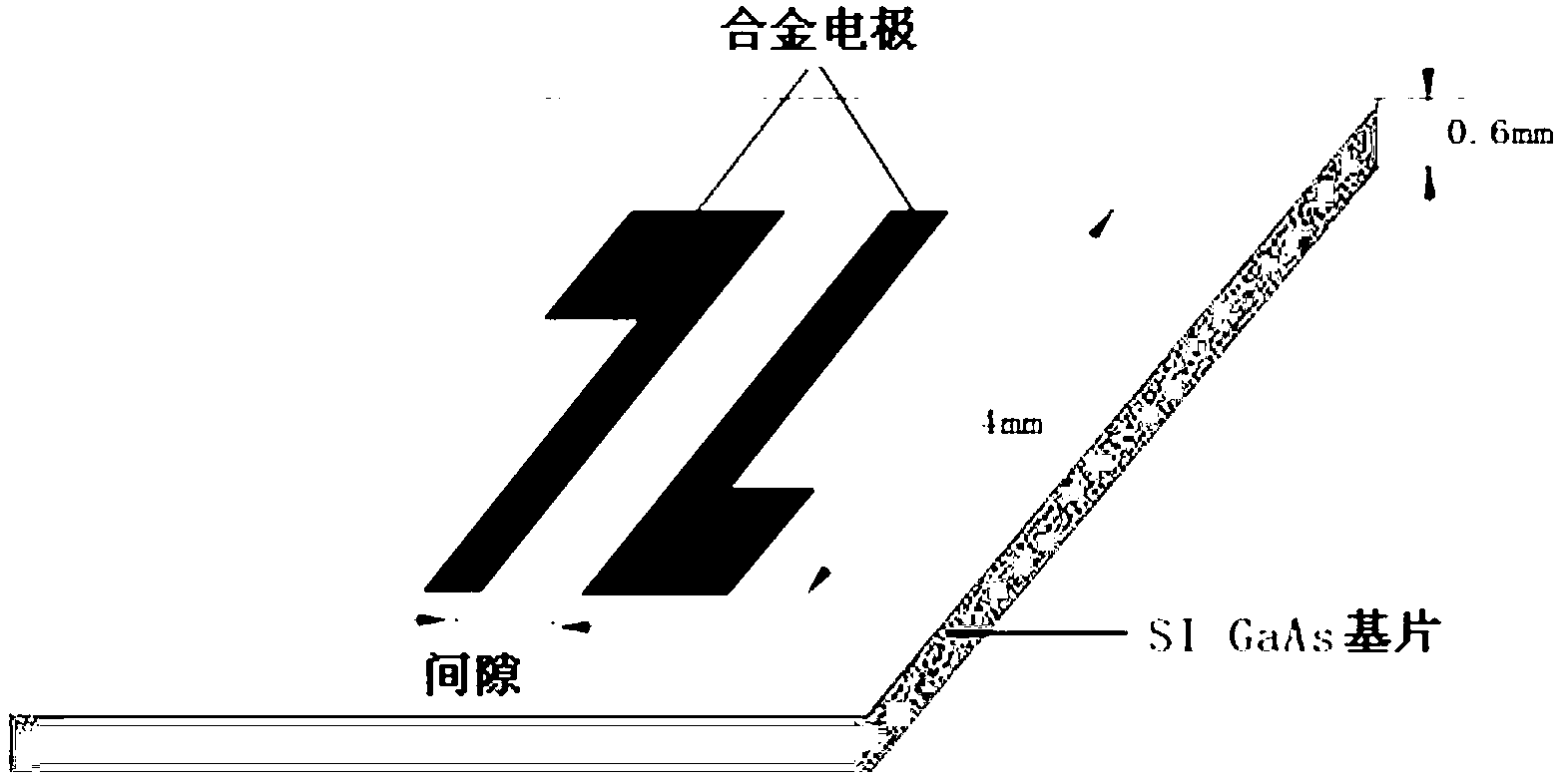

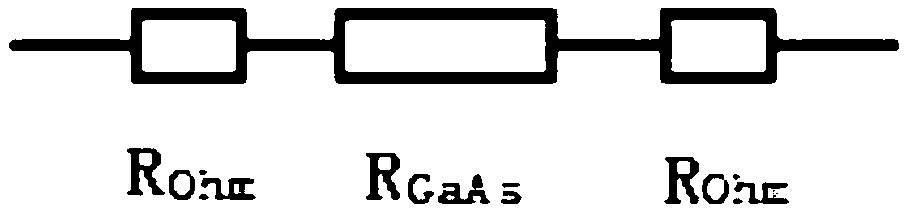

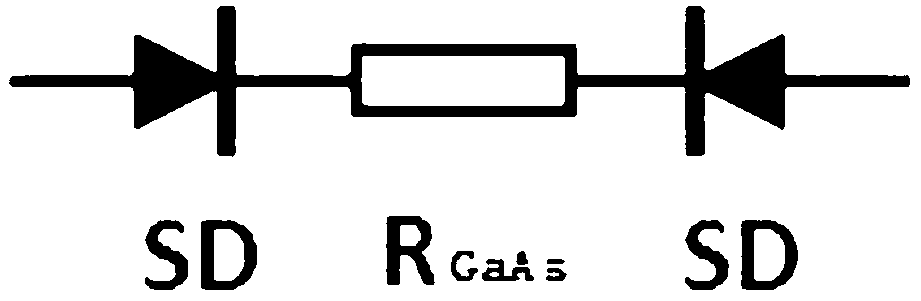

Semi-insolating GaAs photoconductive antenna with ohmic contact electrodes

InactiveCN103236591AHigh breakdown electric fieldImprove radiation efficiencyAntenna supports/mountingsHigh resistanceScreening effect

A semi-insulating GaAs photoconductive antenna with ohmic contact electrodes comprises a semi-insulating GaAs substrate which is provided with a positive AuGeNi alloy electrode and a negative AuGeNi alloy electrode; the semi-insulating GaAs substrate can be considered as a resistor RGaAs with high resistance; the two AuGeNi alloy electrodes can be considered as the resistors Rohm with lower resistance; the resistor RGaAs is connected with the resistors Rohm in serials; and Rohm << RGaAs. Breakdown electric field of the photoconductive antenna is increased through ohmic contact of the antenna electrodes, and meanwhile the whole gap between the electrodes is basically or totally covered by the electric field distribution of the antenna; and as intensity of photon-generated carriers of a unit area is decreased, coulomb screening effect and radiation-field screening effect are controlled effectively, and emitting efficiency of the antenna is increased. Compared with those of the traditional antennas, radiation efficiency and radiation power of the photoconductive antenna with the AuGeNi alloy ohmic contact electrodes are remarkably increased.

Owner:XIAN UNIV OF TECH +1

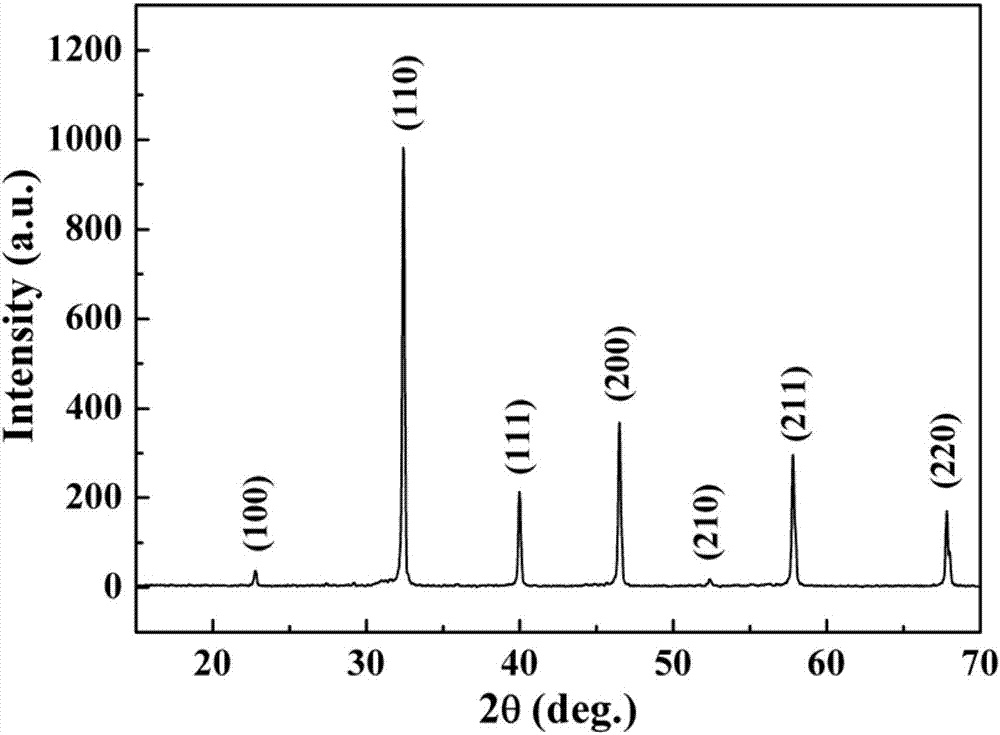

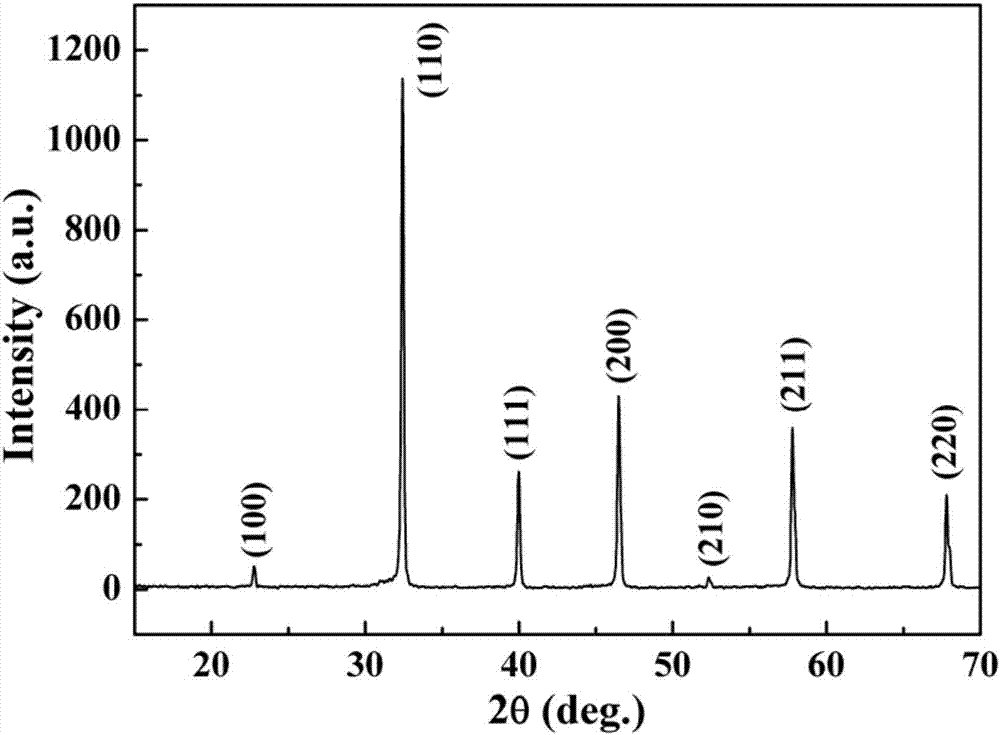

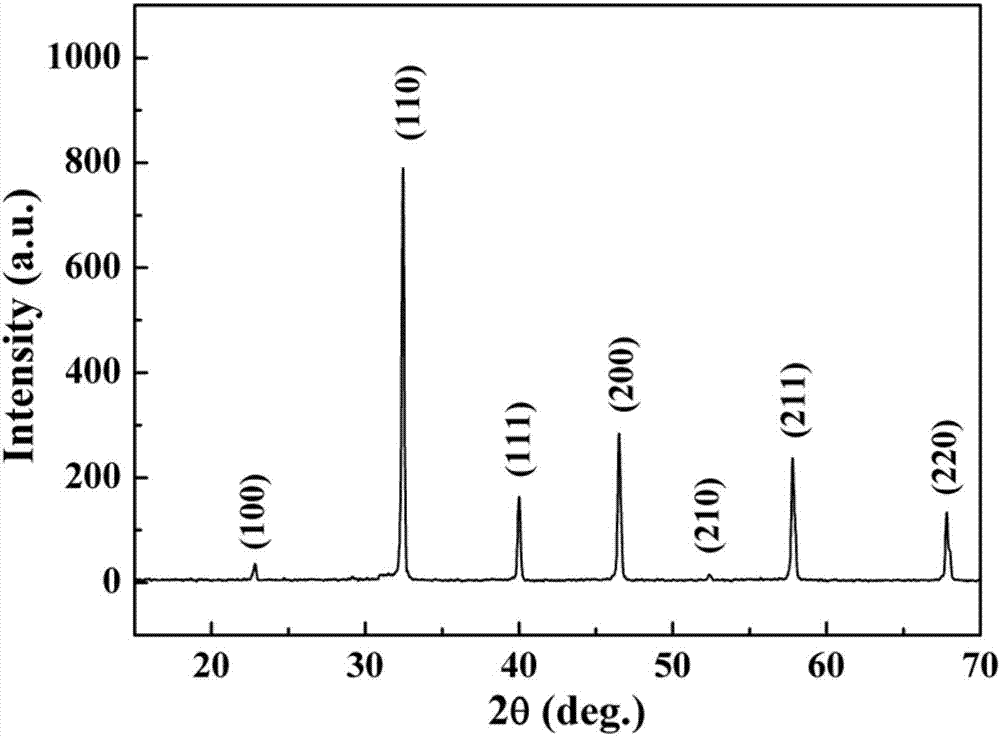

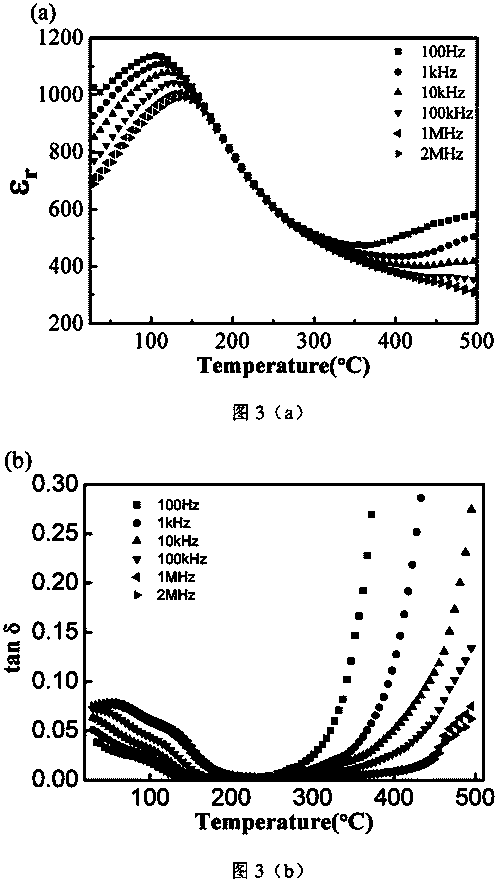

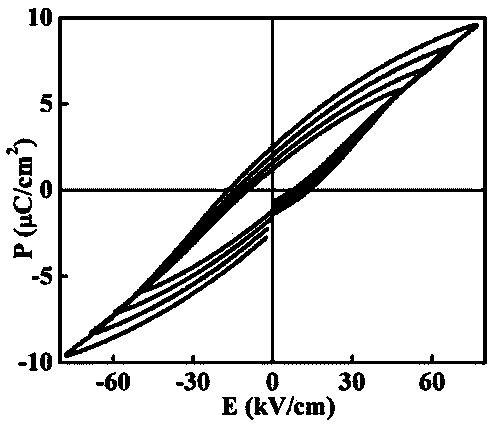

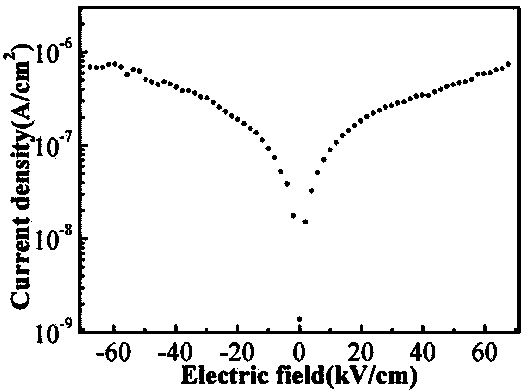

Relaxation ferroelectric material Sr4CaBiTi3Nb7O30 and preparation method thereof

The invention relates to the technical field of ferroelectric material preparation, and discloses a relaxation ferroelectric material Sr4CaBiTi3Nb7O30 synthesized through a conventional solid phase method. The relaxation ferroelectric material Sr4CaBiTi3Nb7O30 is prepared through the following steps: at room temperature, weighing powdery SrCO3, CaCO3, Bi2O3, TiO2 and Nb2O5 according to the stoichiometric ratio of 8:2:1:6:7, uniformly mixing, drying, then presintering, and performing high temperature sintering. The ceramic material has is single-phase in structure, has a relaxation characteristic above room temperature, is low in leakage current, high in breakdown voltage and strong in ferroelectricity at room temperature, and the prepared sample has the property of preferred growth along a single phase. In the preparation of the relaxation ferroelectric material Sr4CaBiTi3Nb7O30, reducing atmosphere is not required, the process is simple, the cost is low, and environmental protection, no toxicity and no pollution are achieved. The relaxation ferroelectric material has a high potential of substituting lead-based relaxation ferroelectric material used as ferroelectric photovoltaic material.

Owner:HUAZHONG UNIV OF SCI & TECH

Trench-gate enhanced type AlGaN/GaN heterojunction field effect transistor

ActiveCN106876458AReduce high electric fieldReduce concentrationSemiconductor devicesElectric field modulationIntrinsics

The invention discloses a trench-gate enhanced type AlGaN / GaN heterojunction field effect transistor which is provided with a part of intrinsic GaN cap layer. The novel structure of the field effect transistor is formed in a manner of introducing the intrinsic GaN cap layer to the edge of a transistor gate, wherein the intrinsic GaN cap layer will reduce the two-dimensional electron gas concentration of a regional conductive trench, and achieves the electric field modulation effect. Through a new electric field peak, the transistor reduces the high electric field of the gate edge, and enables the distribution of the electric field of the surface of the transistor to be more uniform. Compared with a conventional trench-gate enhanced type structure, the novel structure greatly improves the breakdown voltage and reliability.

Owner:XIDIAN UNIV

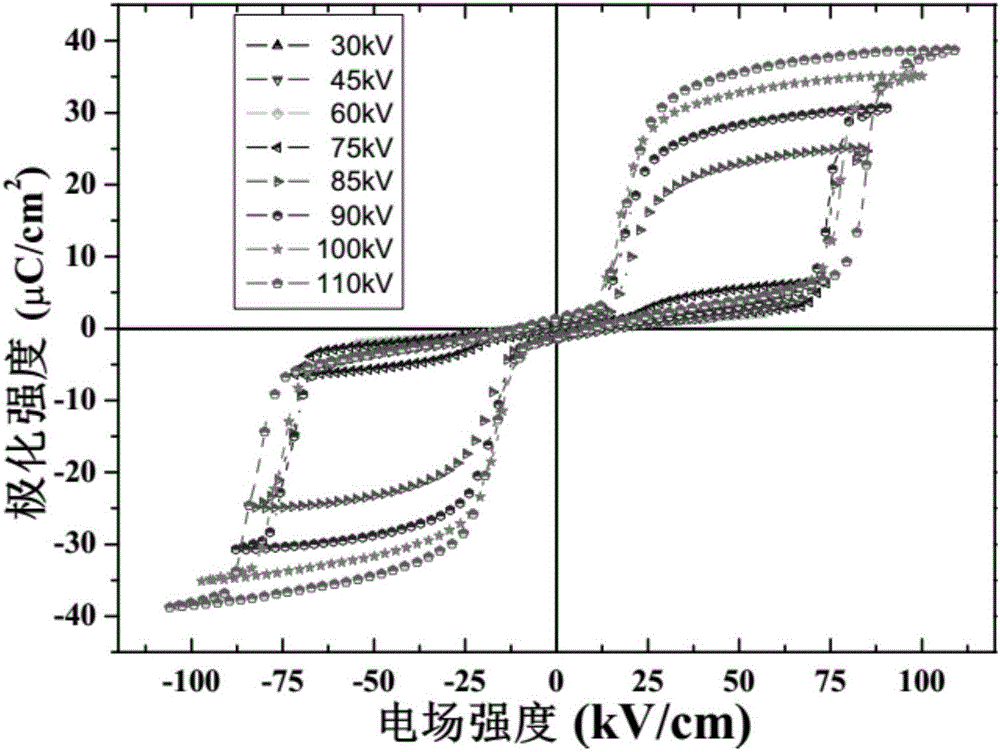

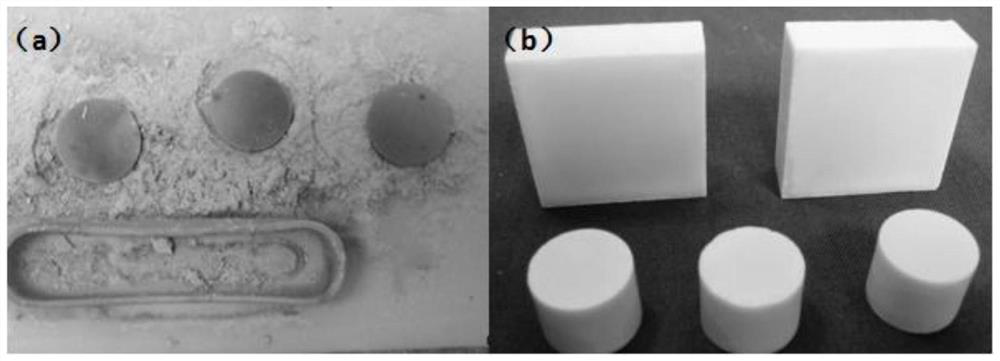

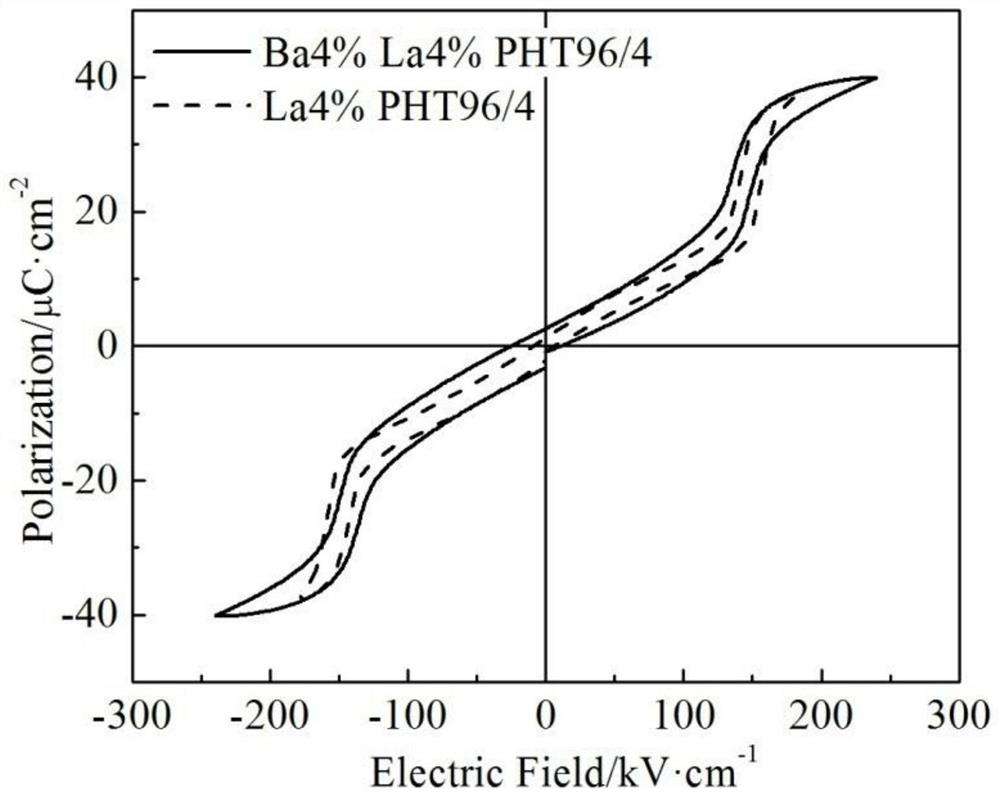

Hafnium lead titanate-based anti-ferroelectric ceramic material and preparation method thereof

A hafnium lead titanate-based anti-ferroelectric ceramic material is characterized in that lead (Pb) in hafnium lead titanate is partially replaced by metal element lanthanum A (La), hafnium (Hf) is partially replaced by tin (Sn), then lead is partially replaced by element B, the chemical formula of the material is [(Pb[1-w]B[w])[1-3z / 2]La[z]][(Hf[1-y]Sn[y])[1-x]Ti[x]]O[3], wherein B is at least one of barium (Ba) and strontium (Sr). The prepared hafnium lead titanate-based anti-ferroelectric ceramic block material has the advantages of compact microstructure, few defects, uniform component distribution, no component segregation, excellent energy storage density (up to 5 J / cm<3>), discharge pulse power (up to 1 MW / cm<3>), high breakdown electric field (up to 250-300 kV / cm), small dielectric loss and stable material performance.

Owner:CHONGQING UNIV OF ARTS & SCI

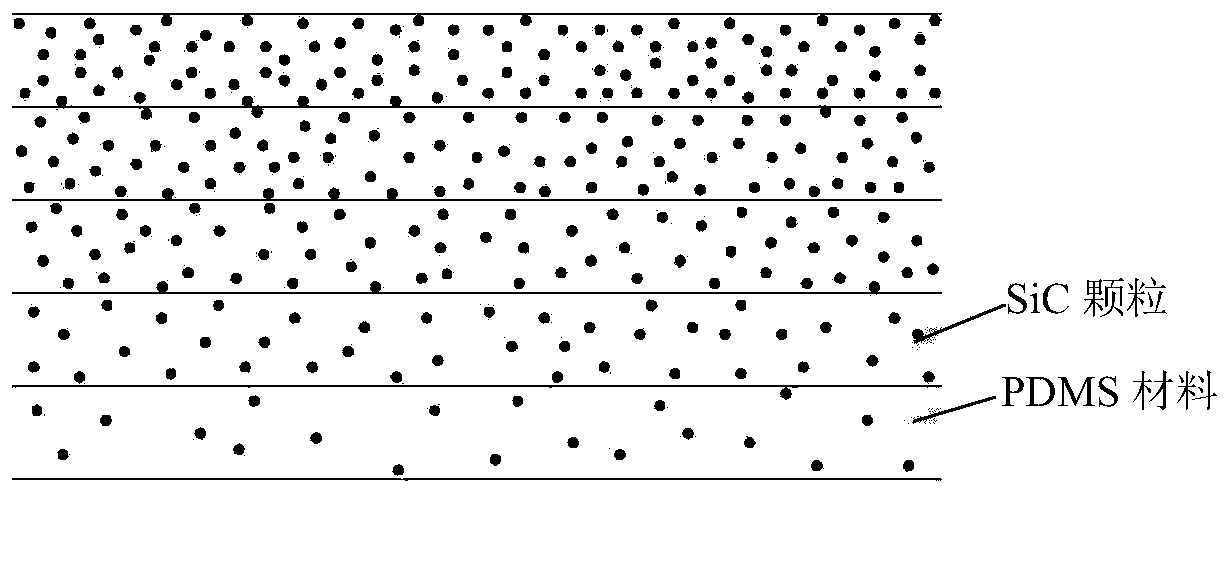

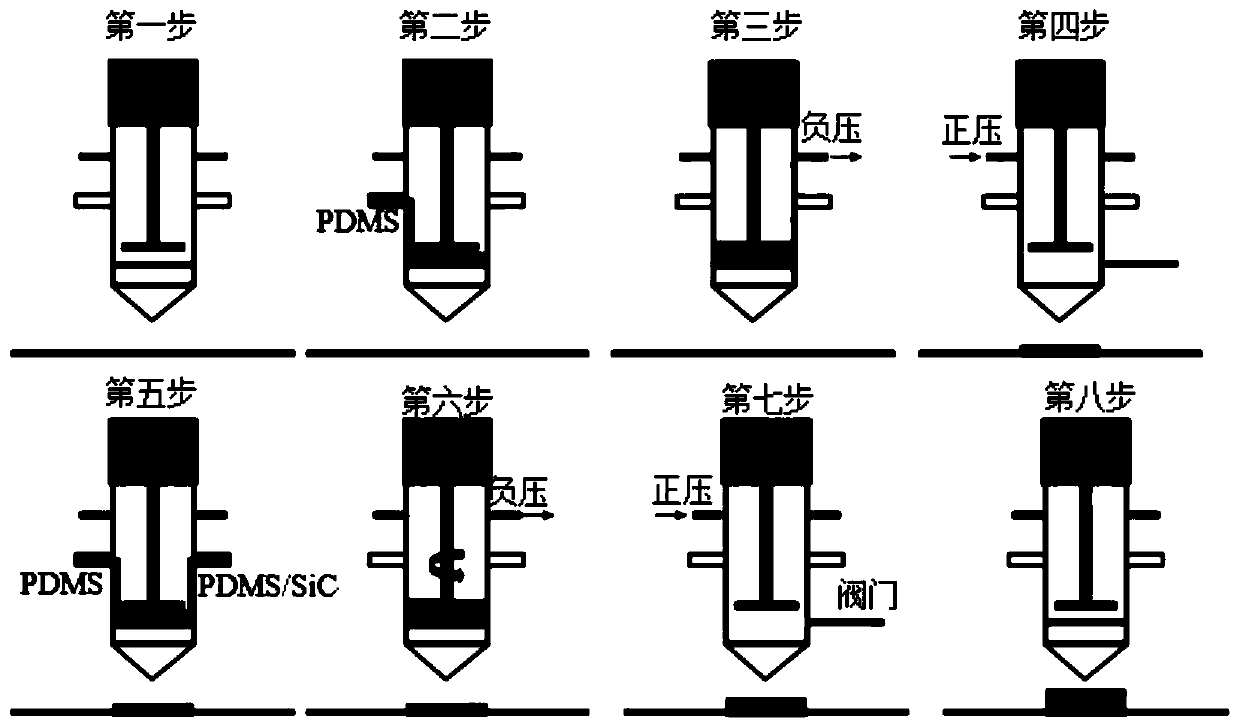

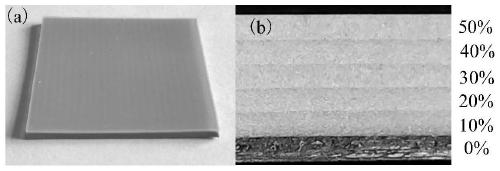

PDMS/SiC functional gradient substrate and preparation method and application thereof

ActiveCN111152452AImprove thermal conductivityImprove wear resistanceAdditive manufacturing apparatusSolid-state devicesHemt circuitsElectrical performance

The invention discloses a PDMS / SiC functional gradient substrate and a preparation method and an application thereof. PDMS in the substrate is a matrix material and SiC is a reinforcing phase; the SiCcontent is in gradient increasing from the outside of the substrate to the inside of the substrate, and the minimum value of SiC content on the outside of the substrate is 0-5%, the maximum value ofthe SiC content in the substrate is 45-55%, -55%, wherein the inner side of the substrate is one side used for being inserted into an electronic component and a connecting circuit. The rigidity of thesubstrate gradually increases from the outer surface to the inner surface, and the flexibility gradually decreases. Namely, the good flexibility on the outer surface of the substrate ensures that thesurface has very good conformability and stretchable / bendable characteristics to meet the requirements of actual working environment and use conditions; however, one side of the inner surface of thesubstrate has higher rigidity, so as to avoid the damage of the electronic component and the connecting circuit caused by excessive deformation when placing the electronic component and printing the connecting circuit (the excessive deformation is limited by improving rigidity constraint), and the stable electrical performance of the electronic component is ensured.

Owner:QINGDAO TECHNOLOGICAL UNIVERSITY

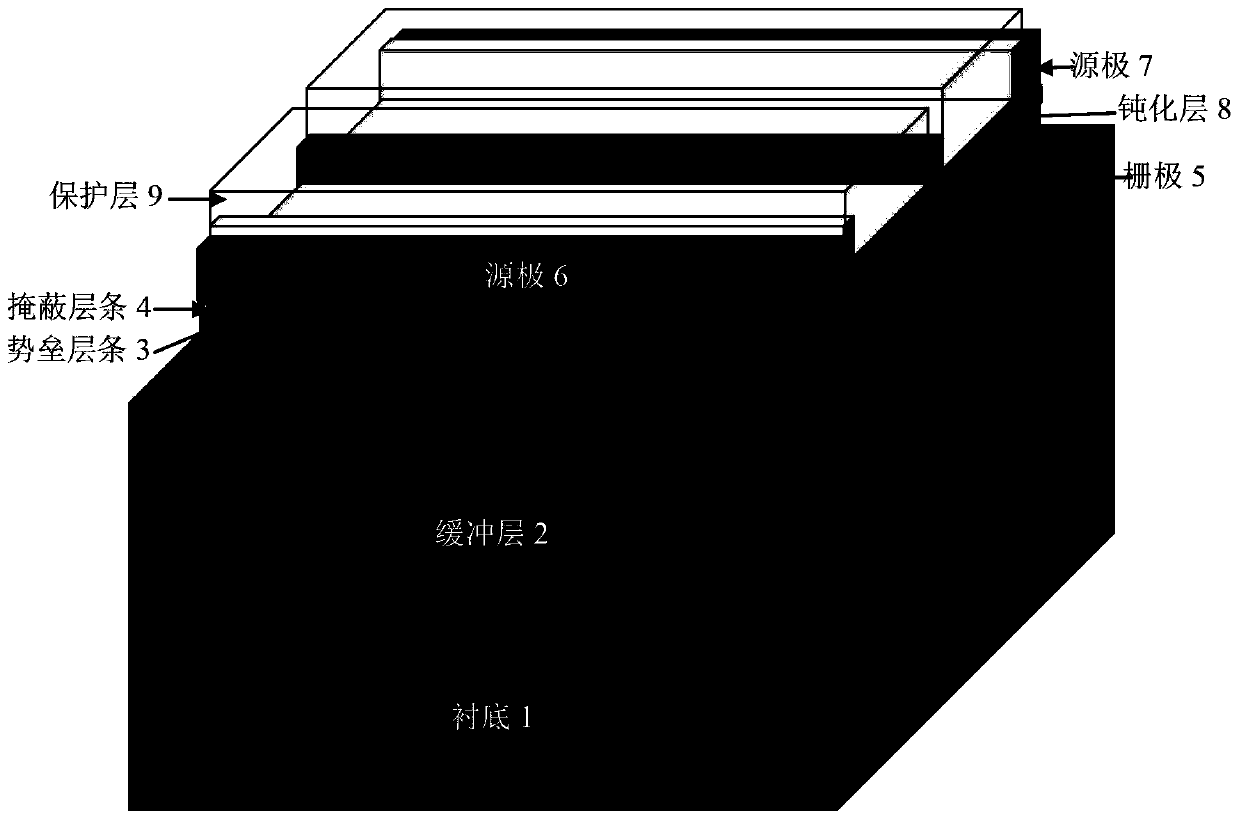

Secondary-growth one-dimensional electron gas GaN-based HEMT (High Electron Mobility Transistor) device and preparation method

ActiveCN103367429AImprove high temperature and high pressure characteristicsImprove featuresNanoinformaticsSemiconductor/solid-state device manufacturingHigh pressureProtection layer

Owner:云南凝慧电子科技有限公司

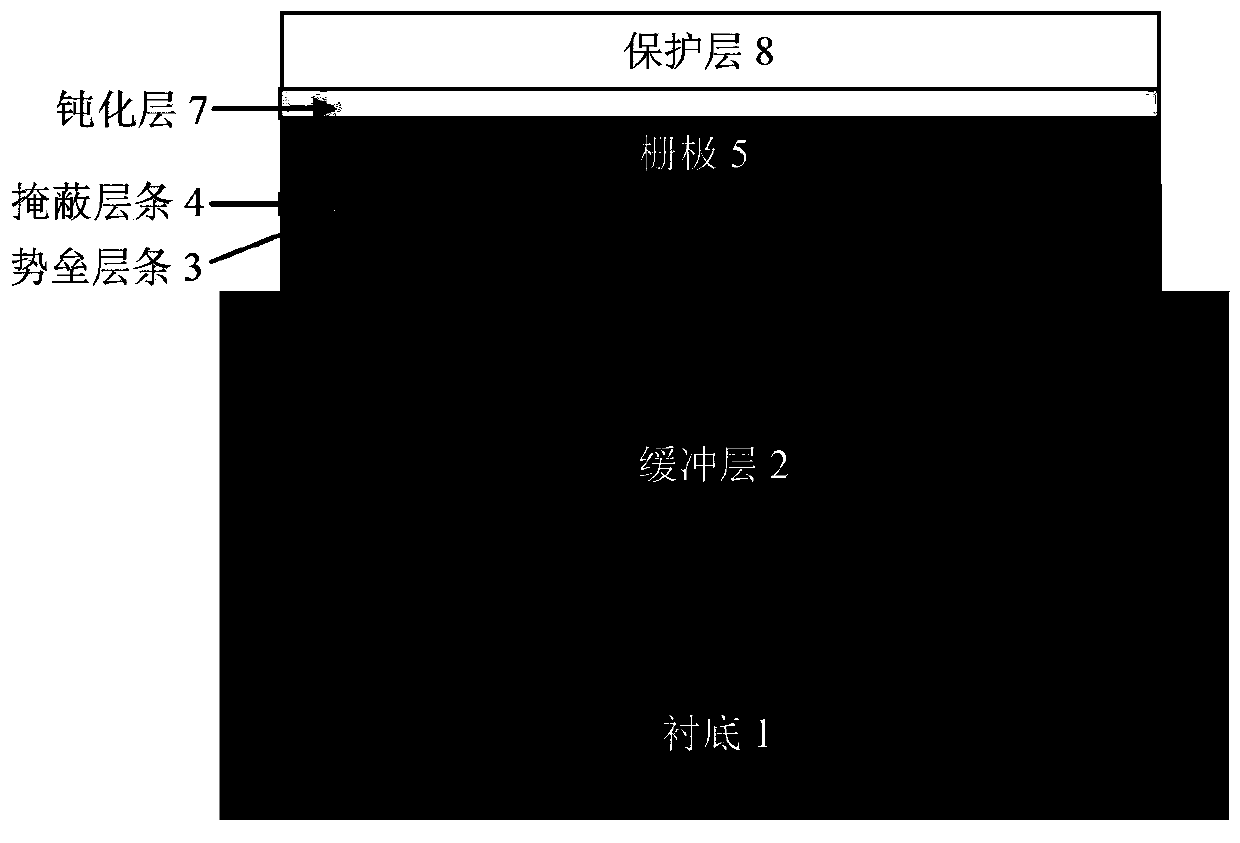

One-dimensional electronic gas GaN-based HEMT (High Electron Mobility Transistor) device adopting selective area epitaxy and preparation method thereof

ActiveCN103400856AImprove high temperature and high pressure characteristicsImprove featuresSemiconductor/solid-state device manufacturingSemiconductor devicesSelective area epitaxyHigh pressure

The invention discloses a one-dimensional electronic gas GaN-based HEMT (High Electron Mobility Transistor) device adopting selective area epitaxy and a preparation method thereof, and mainly solves the problems of poor high temperature and high voltage characteristics, frequency characteristic and power characteristic of an existing one-dimensional electronic gas device. The device comprises a substrate, a buffering layer, a passivation layer and a protection layer from bottom to top; the buffering layer adopts GaN; the buffering layer is provided with barrier layer strips and masking layer strips, which are periodically arranged at intervals; both ends of each barrier layer strip respectively are a source electrode and a drain electrode; the passivation layer is positioned on the barrier layer strips and the masking layer strips; the passivation layer is provided with a grid slot; a grid electrode is arranged in the grid slot; and the barrier layer strips adopt AlGaN and the width of each barrier layer strip is in nanometer dimension so as to form one-dimensional electronic gas. Compared with Si-based and GaAs-based one-dimensional electronic gas devices, due to the adoption of a wide bandgap semiconductor GaN with the outstanding material characteristics, the one-dimensional electronic gas GaN-based HEMT device adopting selective area epitaxy has excellent high temperature and high voltage characteristics, frequency characteristic and power characteristic, and the ultrahigh speed and low power consumption one-dimensional electronic gas device can be made.

Owner:云南凝慧电子科技有限公司

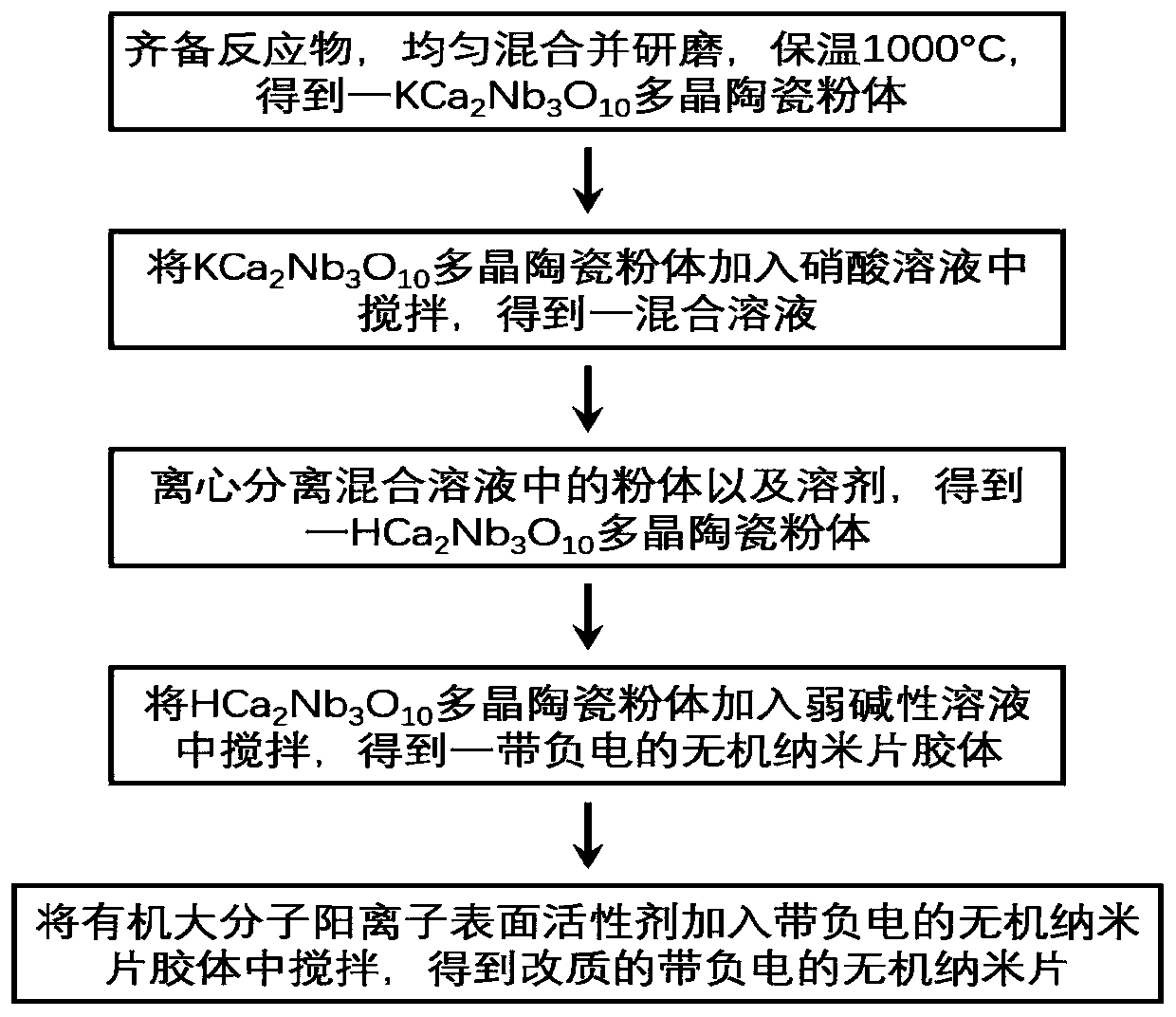

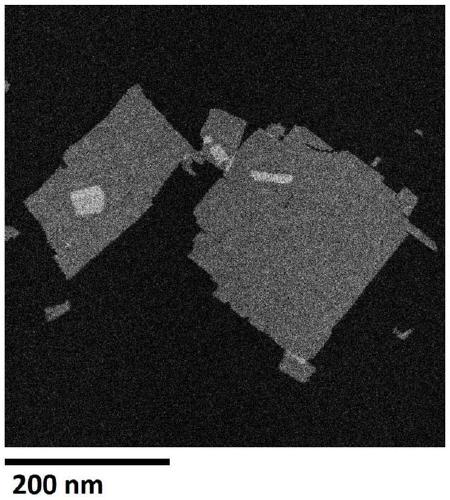

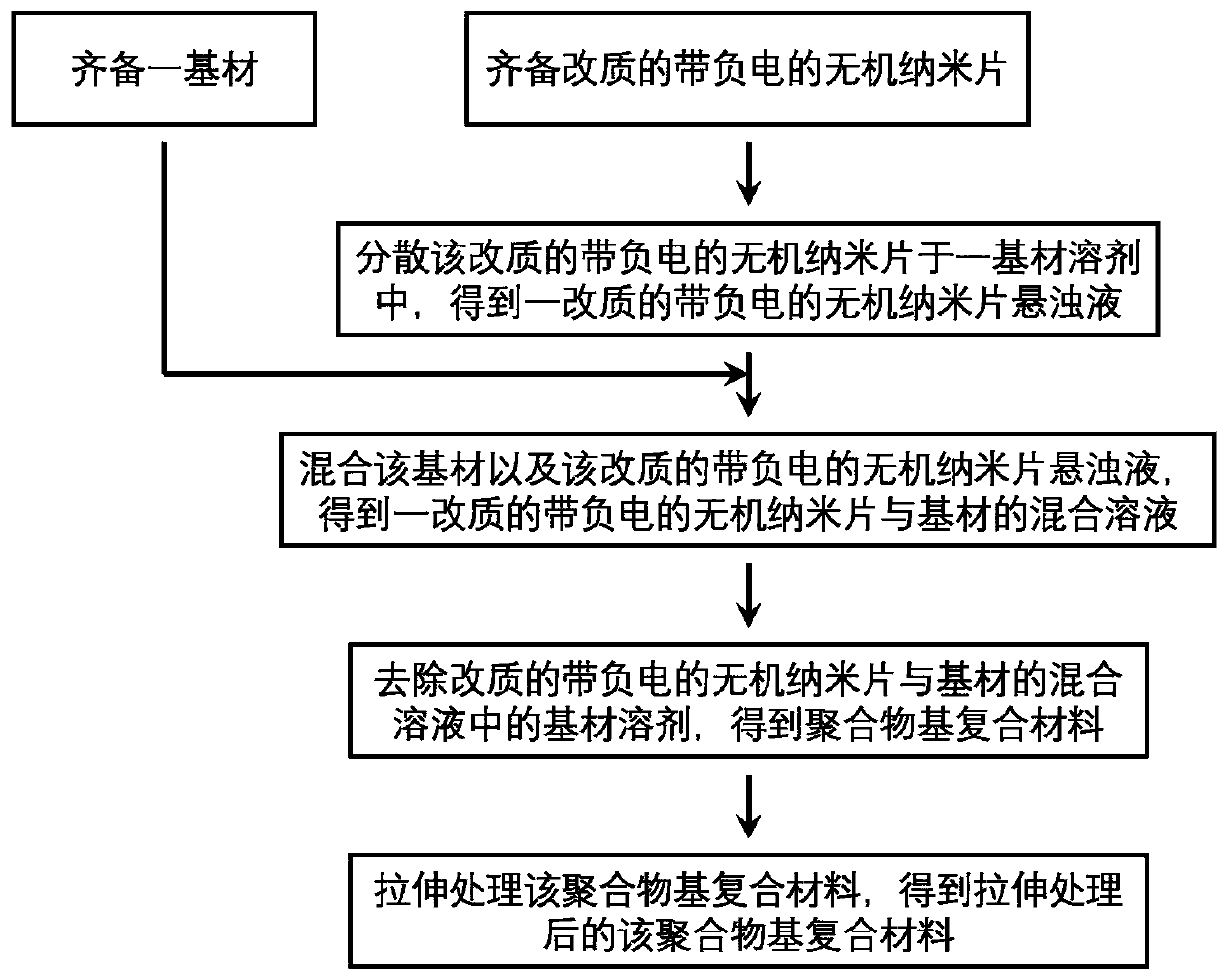

Polymer-based composite material and preparation method thereof

ActiveCN109705502AHigh breakdown electric fieldIncrease energy densityHigh energySecondary electrons

The invention provides a polymer-based composite material which is characterized by comprising a base material and modified negatively-charged inorganic nanosheets; wherein the base material is a polymer material; and the modified negatively-charged inorganic nanosheets are dispersed in the base material, the surface of the modified negatively-charged inorganic nanosheets is provided with non-removable negative charges, and an organic macromolecular cationic surfactant is adsorbed on the surface of the modified negatively-charged inorganic nanosheets. The polymer-based composite material provided by the invention utilizes a reverse local electric field generated by the modified negatively-charged inorganic nanosheets, and the number of secondary electrons caused by collision ionization isreduced, so that the polymer-based composite material has a high breakdown electric field so as to obtain high energy density, and the industrial application value of the material in the field of energy storage can be greatly improved.

Owner:UNIV OF SCI & TECH OF CHINA

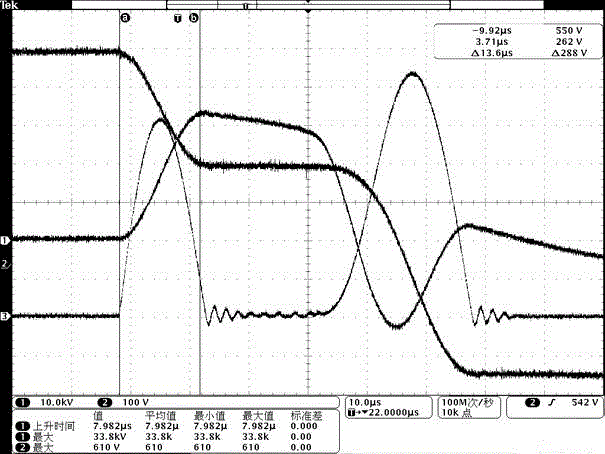

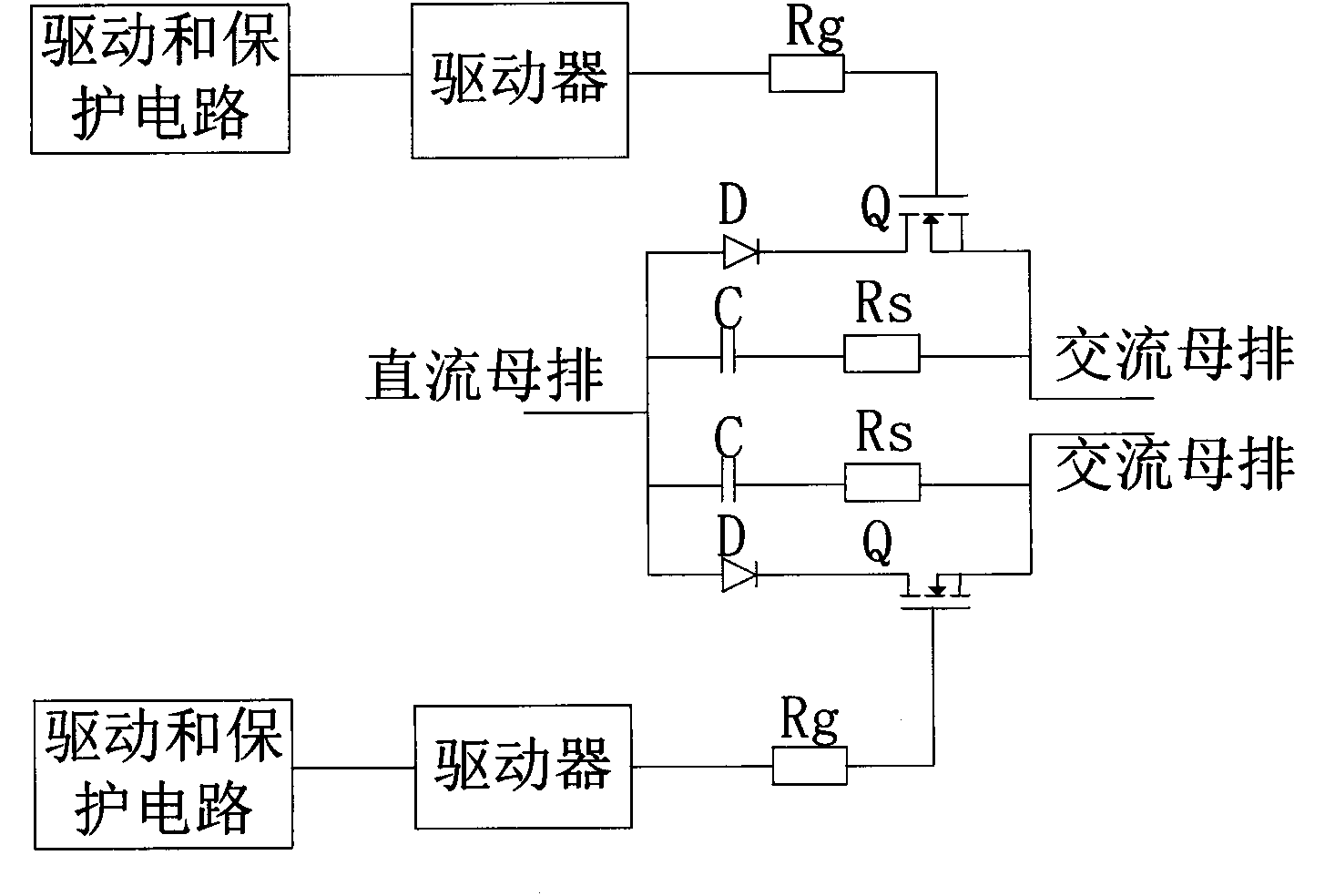

High-frequency inverter power unit and high-frequency treatment method

InactiveCN103731060AWide bandgapHigh breakdown electric fieldEfficient power electronics conversionAc-dc conversionUltrahigh frequencyOxide semiconductor

The invention provides a high-frequency inverter power unit. The high-frequency inverter power unit comprises two bridge arms of the same circuit topology; the two bridge arms are completely symmetrical; each bridge arm comprises a power device which comprises a silicon carbide MOSFET (Metal Oxide Semiconductor Field Effect Transistor), a silicon carbide Schottky diode and a grid resistor and a resistance-capacitance absorbing resistor of the MOSFET; three pins of each silicon carbide MOSFET are G, D and S respectively; two of three pins of each silicon carbide Schottky diode, which are arranged at two ends respectively, are positive poles; the middle pin of the three pins of each silicon carbide Schottky diode is a negative pole; one end of each grid resistor is connected with a driver and the other end of each grid resistor is connected with the G pole of each silicon carbide MOSFET; the negative pole of each silicon carbide Schottky diode is connected with the D pole of each silicon carbide MOSFET; the two positive poles of each silicon carbide Schottky diode is are connected onto a direct current busbar; the S pole of each silicon carbide MOSFET is connected with one end of each resistance-capacitance absorbing resistor and then connected onto an alternating current busbar. According to the high-frequency inverter power unit, the application requirements of the ultrahigh frequency can be met.

Owner:BAODING SIFANGSANYI ELECTRIC

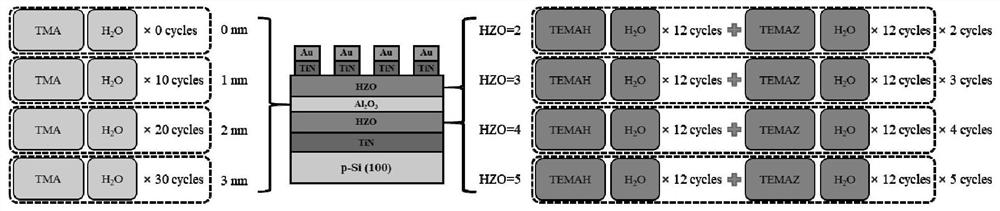

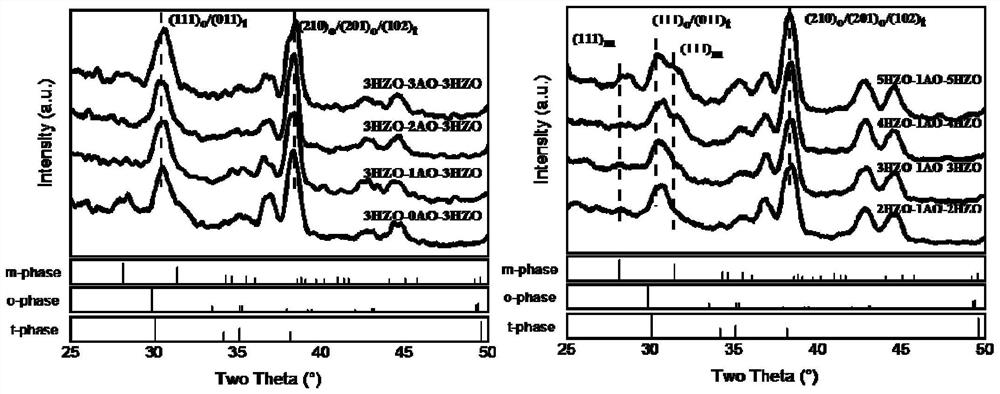

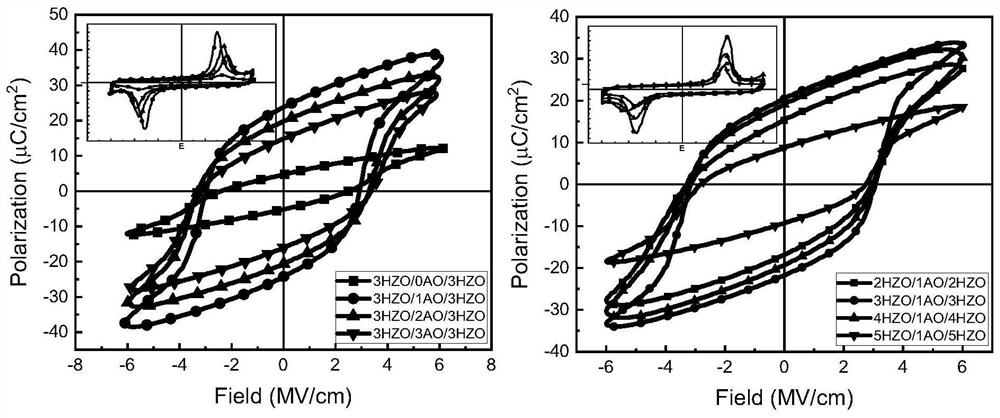

HZO/AO/HZO nano laminated film and preparation method and application thereof

PendingCN113658941AEvenly distributedInhibit growthMaterial nanotechnologySemiconductor/solid-state device detailsElectron injectionLeakage current density

The invention discloses an HZO / AO / HZO nano laminated film and a preparation method and application thereof. The film is composed of an HZO top layer, an AO middle layer and an HZO bottom layer, wherein the HZO top layer is formed by alternately laminating HfO2 film layers and ZrO2 film layers, the AO middle layer is an Al2O3 film layer, and the HZO bottom layer is formed by alternately laminating HfO2 film layers and ZrO2 film layers. According to the technical scheme, the HfO2 layers and the ZrO2 layers are alternately deposited, an interface is introduced through a nano laminated structure to regulate and control interface energy to stabilize a phase, growth of an electric tree is effectively hindered, and breakdown is avoided. In addition, the interface can reduce the electron injection depth and inhibit local phase decomposition, so that the fatigue performance is finally improved. On the other hand, the dielectric layer Al2O3 is introduced to promote the formation of a 180-degree domain so as to reduce a built-in electric field, weaken the fixed orientation degree of the electric domain and reduce the leakage current density. According to the invention, the technical problem of preparation of the HZO / AO / HZO nano laminated film with good ferroelectric performance can be solved, and the high-quality ferroelectric film can be produced in a simple and controllable mode.

Owner:CENT SOUTH UNIV

Low-resistance silicon on insulator-lateral insulated gate bipolar transistor (SOI-LIGBT) device capable of preventing snapback effect and manufacturing method thereof

InactiveCN106876454AImprove vertical breakdown voltageLower specific on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesLinearityBlocking layer

The invention provides a low-resistance silicon on insulator-lateral insulated gate bipolar transistor (SOI-LIGBT) device capable of preventing a snapback effect and a manufacturing method thereof. A cell structure of the low-resistance SOI-LIGBT comprises a substrate, a buried oxide layer, a thick dielectric layer, a thick silicon layer drift region, a P well region, a P-type heavily-doped emitter region, a first N-type heavily-doped region, an N-type buffer region, a P-type heavily-doped collector region, a second N-type heavily-doped region, a collector dielectric blocking layer, a collector contact electrode, an ultrathin top-layer silicon drift region, an emitter contact electrode, a gate oxide layer, a poly-silicon gate, P strips and N strips, wherein the N strips are alternatively arranged in the thick silicon layer drift region in longitudinal directions of the P strips. The electric field of the buried layer is improved by employing the ultrathin top layer silicon drift region to increase the longitudinal breakdown voltage of an SOI device; the specific on resistance of the device is reduced by employing the thick silicon layer drift region; and for the ultrathin top layer silicon drift region and the thick silicon layer drift region, lateral linearity variable doping is used for adjusting surface electric field distribution, so that the specific on resistance is greatly reduced as well as high breakdown voltage of the device is greatly maintained.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA +1

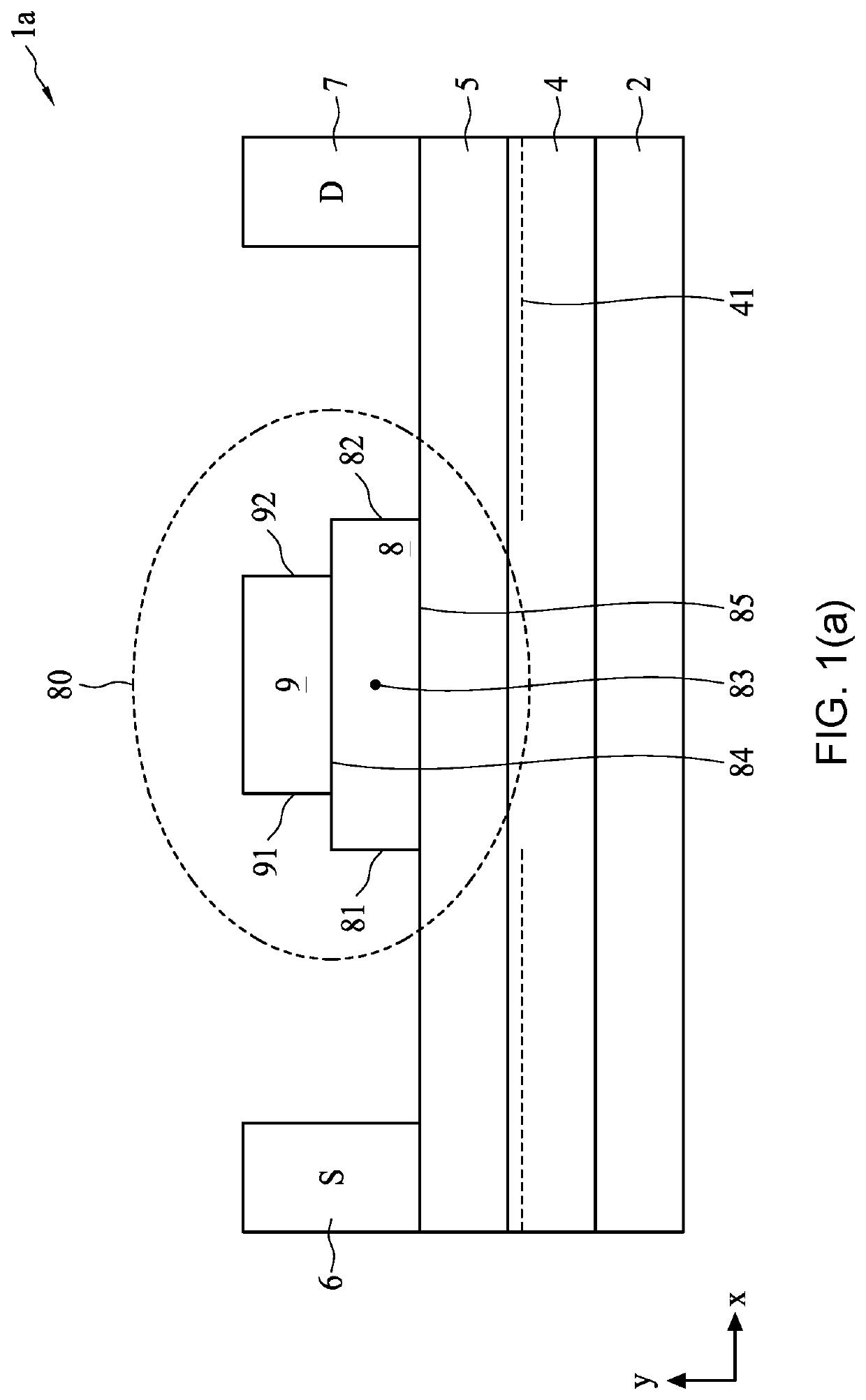

Semiconductor device having improved gate leakage current

PendingUS20210399123A1Wide bandgapVelocity increasesSolid-state devicesSemiconductor/solid-state device manufacturingGate leakage currentDevice material

The present invention relates to a semiconductor device having an improved gate leakage current. The semiconductor device includes: a substrate; a first nitride semiconductor layer, positioned above the substrate; a second nitride semiconductor layer, positioned above the first nitride semiconductor layer and having an energy band gap greater than that of the first nitride semiconductor layer; a source contact and a drain contact, positioned above the second nitride semiconductor layer; a doped third nitride semiconductor layer, positioned above the second nitride semiconductor layer and between the drain contact and the source contact; and a gate electrode, positioned above the doped third nitride semiconductor layer, where the doped third nitride semiconductor layer has at least one protrusion extending along a direction substantially parallel to an interface between the first nitride semiconductor layer and the second nitride semiconductor layer, thereby improving the gate leakage current phenomenon.

Owner:INNOSCIENCE (ZHUHAI) TECH CO LTD