A system and method for power detection and failure judgment

A power detection and judgment system technology, applied in the direction of electronic circuit testing, etc., can solve the problems of large output voltage jitter of power output devices, increased design cost and test time, and inability to quickly develop detection and failure judgment devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

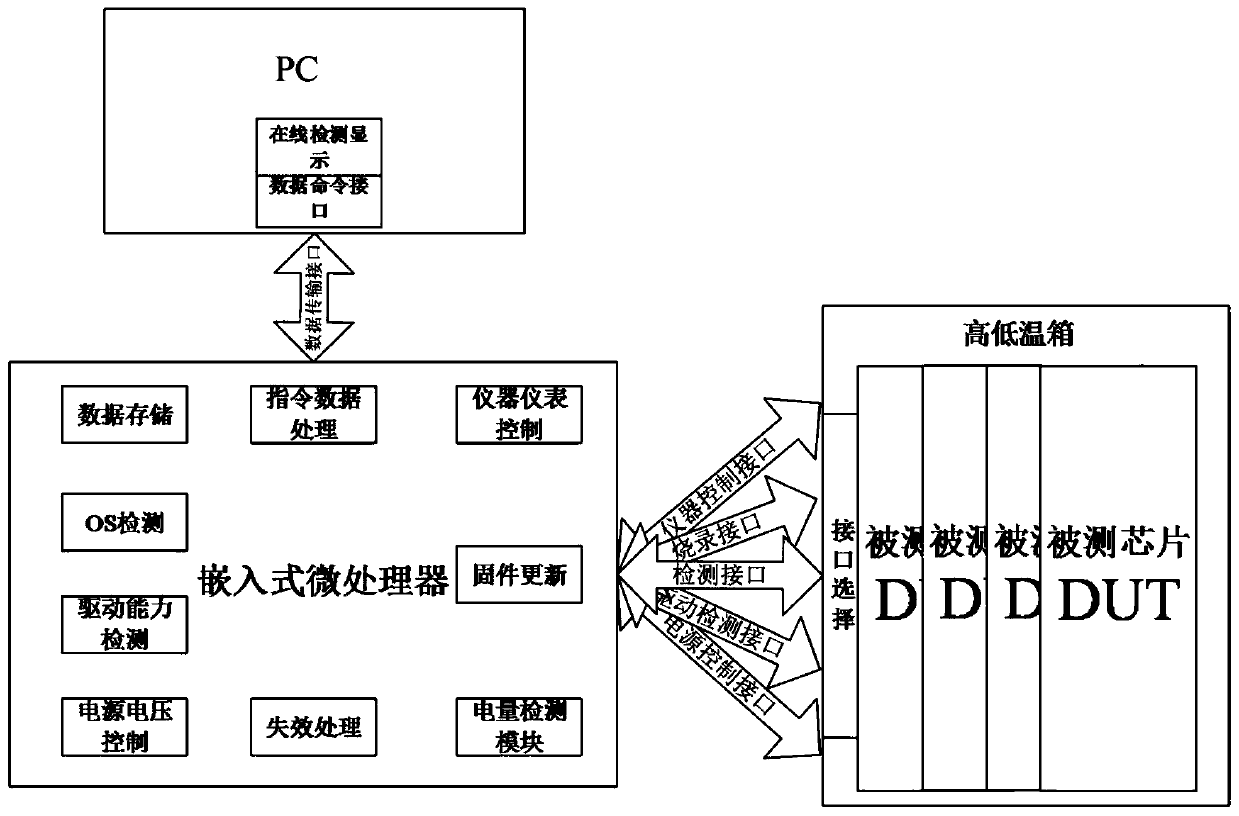

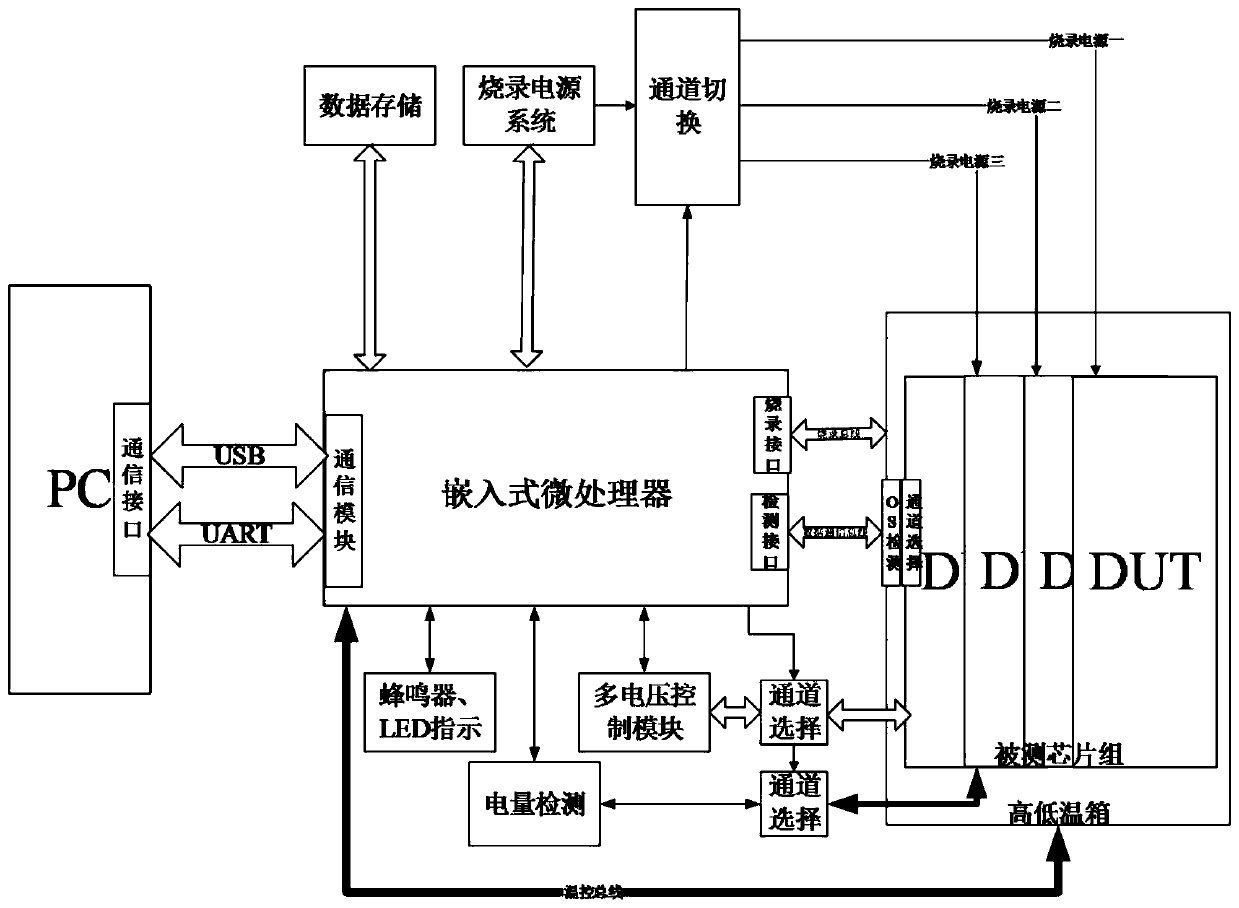

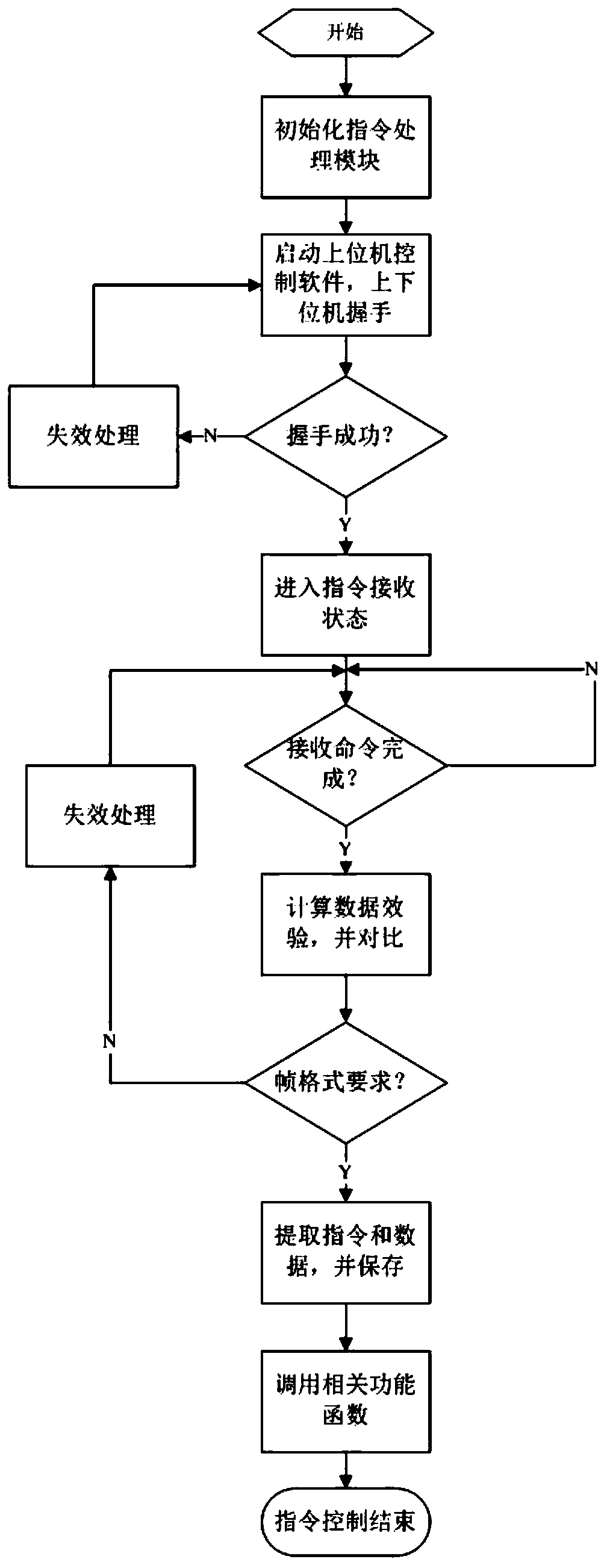

[0052] see figure 1 , 2 As shown, the present invention realizes the power detection and failure judgment system of the chip. The system integrates multiple power and electrical indicators into a system for detection and failure judgment, including the physical and electrical connection characteristics of the chip itself, which greatly improves work efficiency. And according to the relevant issues for analysis and instructions. The system consists of command processing module, data storage module, OS detection module, power control module, voltage self-calibration module, firmware update module, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More