Chip passivation layer and method for forming chip passivation layer

A passivation layer and chip technology, used in semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., can solve problems such as shedding, internal stress changes, and device failures.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

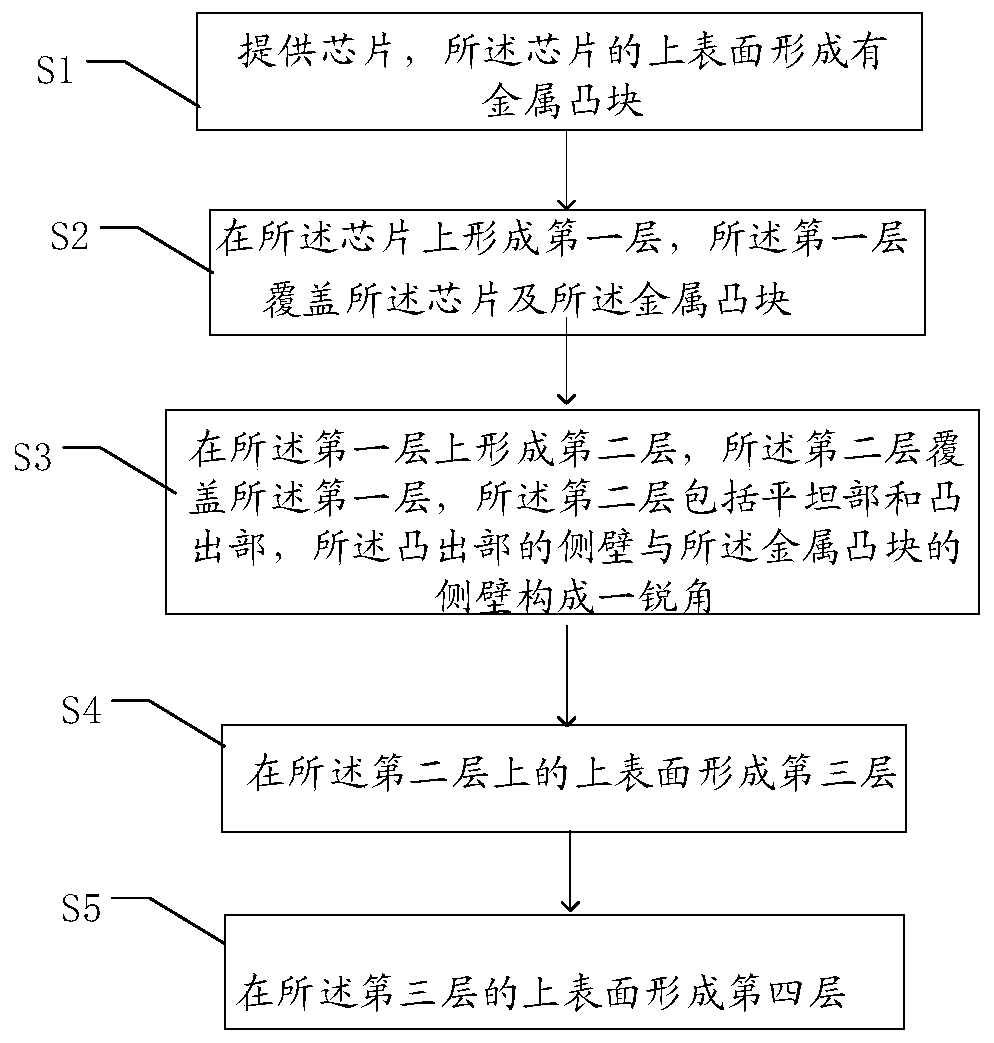

[0033] The specific implementations of the passivation layer of the chip and the method for forming the passivation layer of the chip provided by the present invention will be described in more detail below with reference to schematic diagrams. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

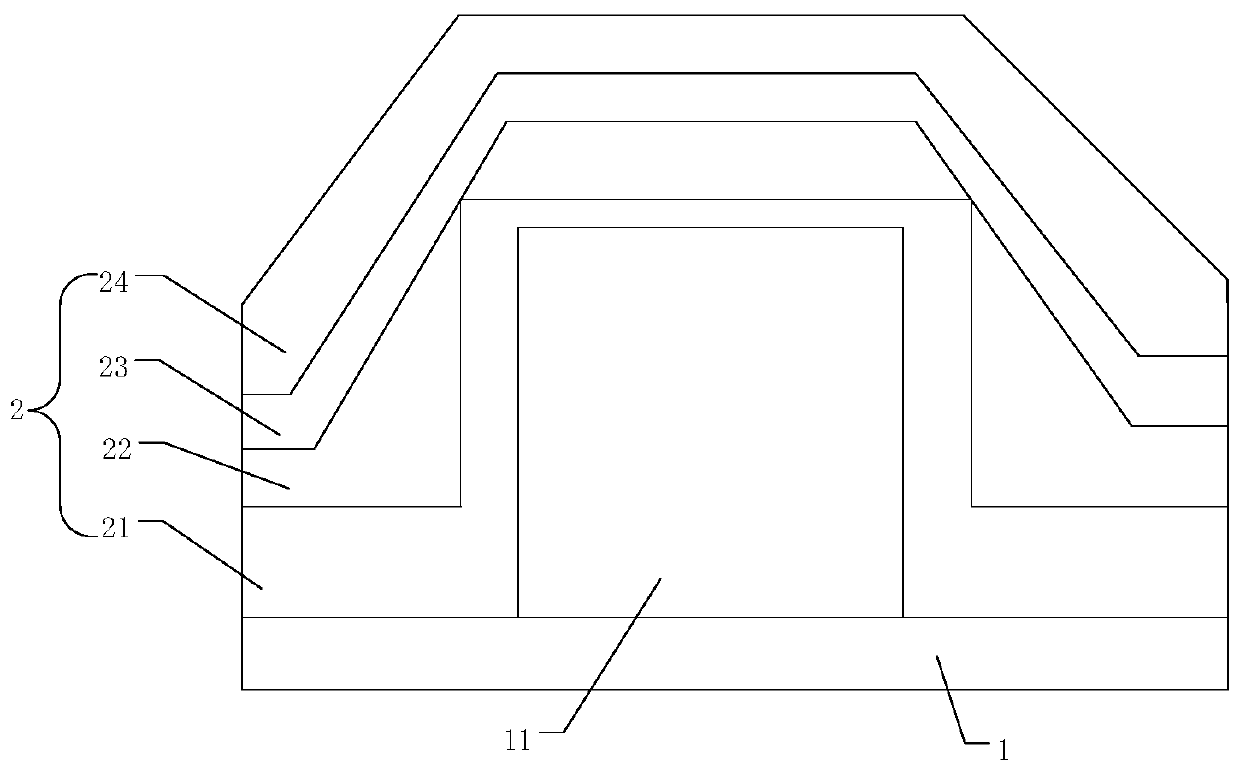

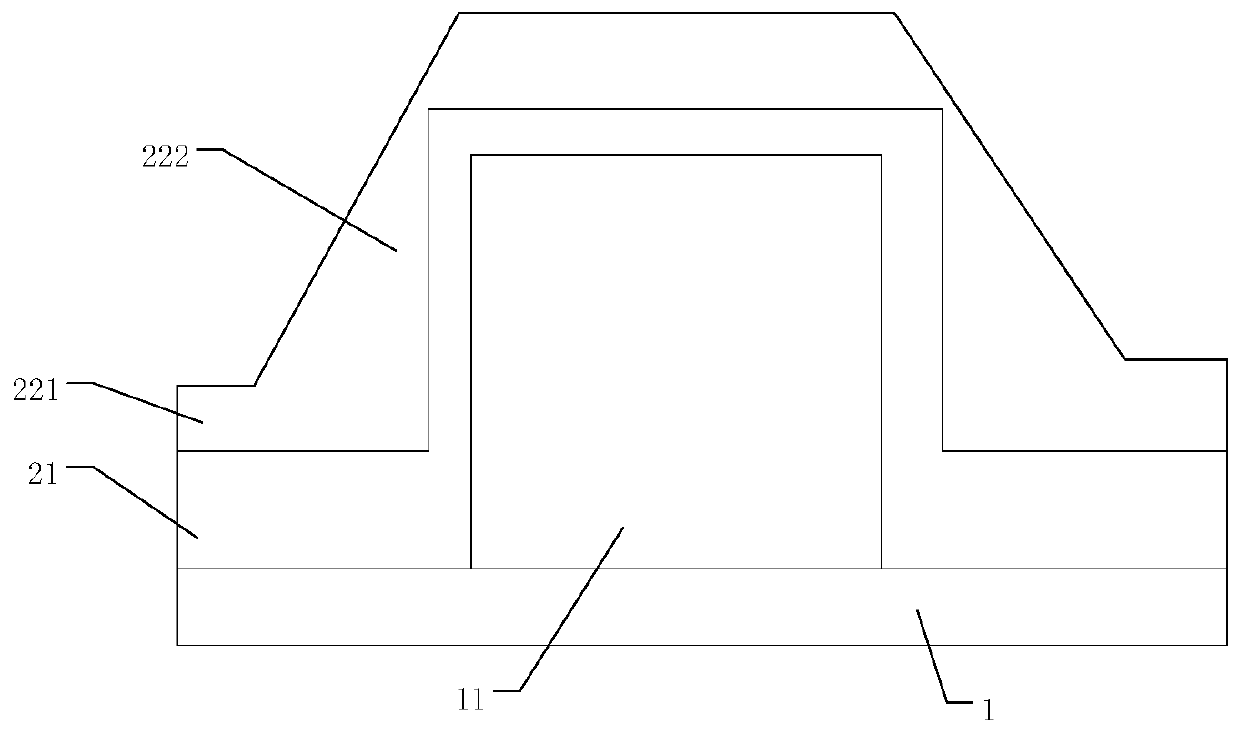

[0034] refer to figure 1 , which is a schematic diagram of the passivation layer of the chip provided by the embodiment, such as figure 1 As shown, the passivation layer 2 includes a first layer 21, a second layer 22, a third layer 23 and a fourth layer 24, and the first layer 21, the second layer 22, the third layer 23 and the fourth layer 24 are sequentially overlapped to cover the chip 1; metal bumps 11 are f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More