On-chip learning neural network processor

A neural network and neural network learning technology, applied in the direction of biological neural network model, physical realization, etc., can solve the problems of lack of general potential and not suitable for popularization, and achieve the goal of improving data throughput and computing speed and reducing hardware area Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

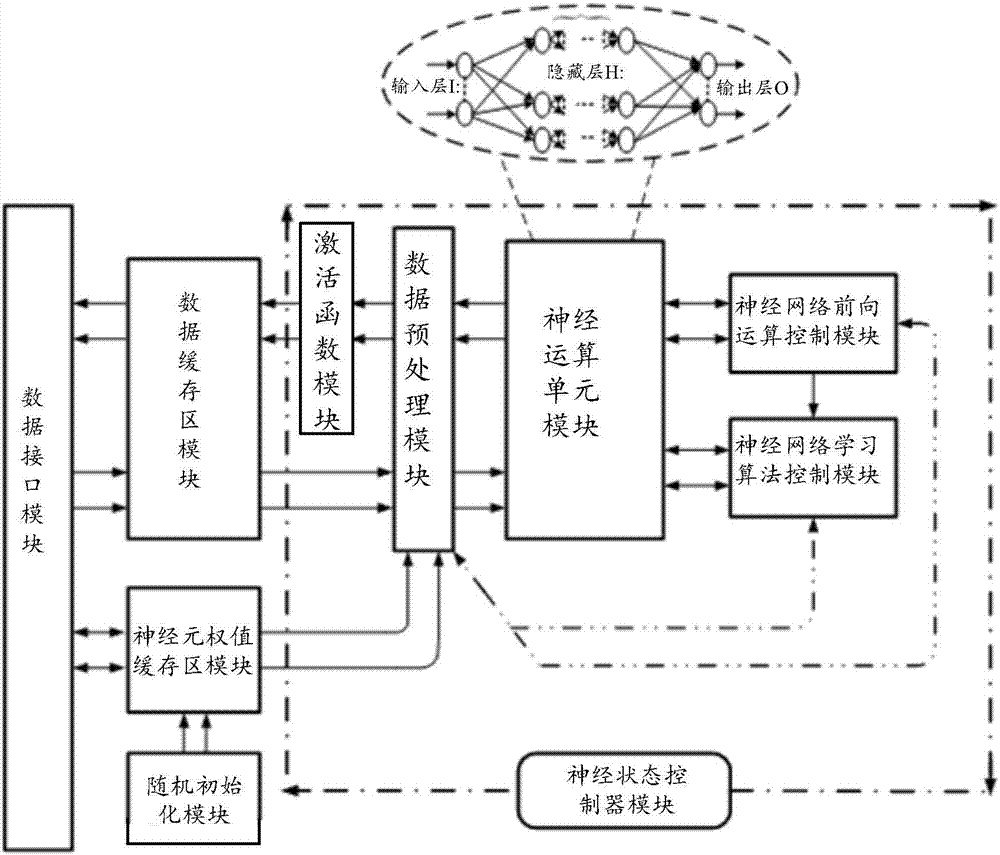

[0038] The present invention provides an on-chip learning neural network processor, see figure 1 , including: neural state controller module, data interface module, neural network forward operation control module, neural network learning algorithm control module, neural operation unit module, neuron weight buffer module, activation function module and data buffer module connection ;

[0039]The neural state controller module is respectively connected with the data interface module, the neuron weight buffer module, the neural network forward operation control module, the neural network learning algorithm control module, the activation function module, and the data buffer module. The neural state controller module controls the data interface module to perform data interaction, and monitors the working state of the neural network forward operation control module and the neural network learning algorithm control module, and simultaneously generates the current neural working state...

Embodiment 2

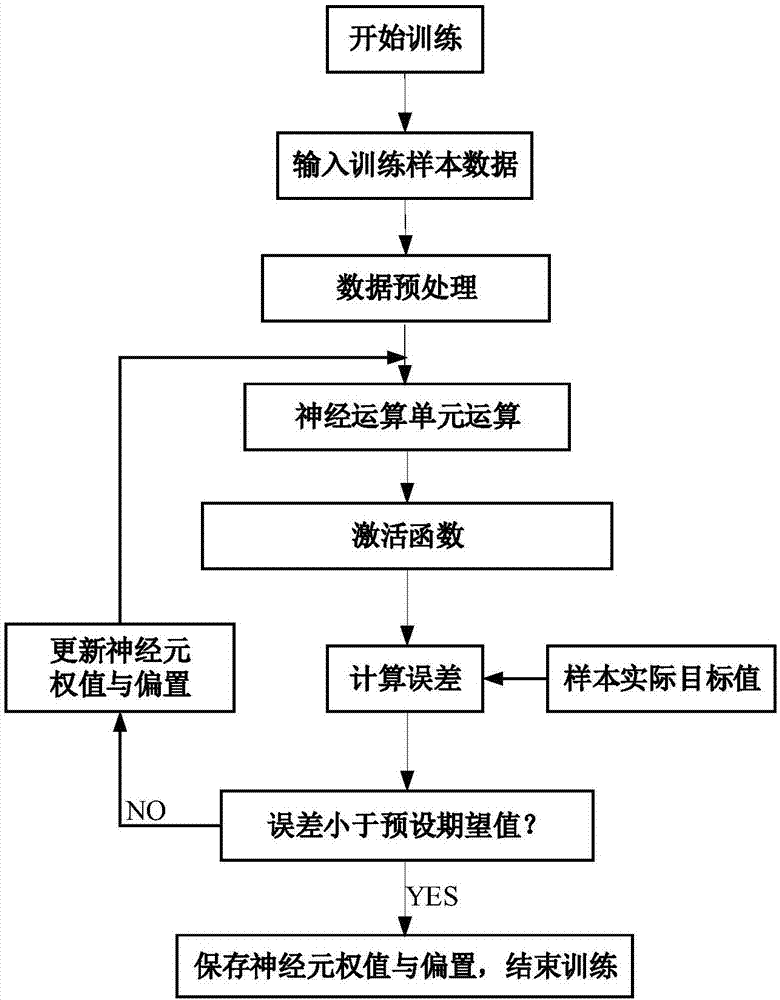

[0079] The present invention provides a kind of work based on on-chip learning neural network processor is divided into two stages, see figure 2 ,Specifically:

[0080] Phase 1: Training (learning) of the neural network

[0081] 1) Data preparation and preprocessing

[0082] Load the training sample data into the data buffer area through the data interface module, and randomly initialize the neuron weight buffer area through the random initialization module. After the data preparation is completed, load the data in the data buffer area and the neuron weight buffer area into the data The preprocessing module performs preprocessing.

[0083] 2) Neural network parameter configuration

[0084] Load the neural network parameters such as the number of neurons in the input layer, the number of neurons in the hidden layer, the number of neurons in the output layer, the activation function of the hidden layer, the activation function of the output layer, the learning rate, the erro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More