A method of manufacturing a semiconductor device

A manufacturing method and semiconductor technology, which is applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of target pattern distortion, poor surface roughness of spacer wall, and complicated process, so as to improve yield and performance, The effect of small process fluctuation and improved robustness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0050] In order to solve the above technical problems, the present invention provides a method for manufacturing a semiconductor device, such as image 3 As shown, it mainly includes the following steps:

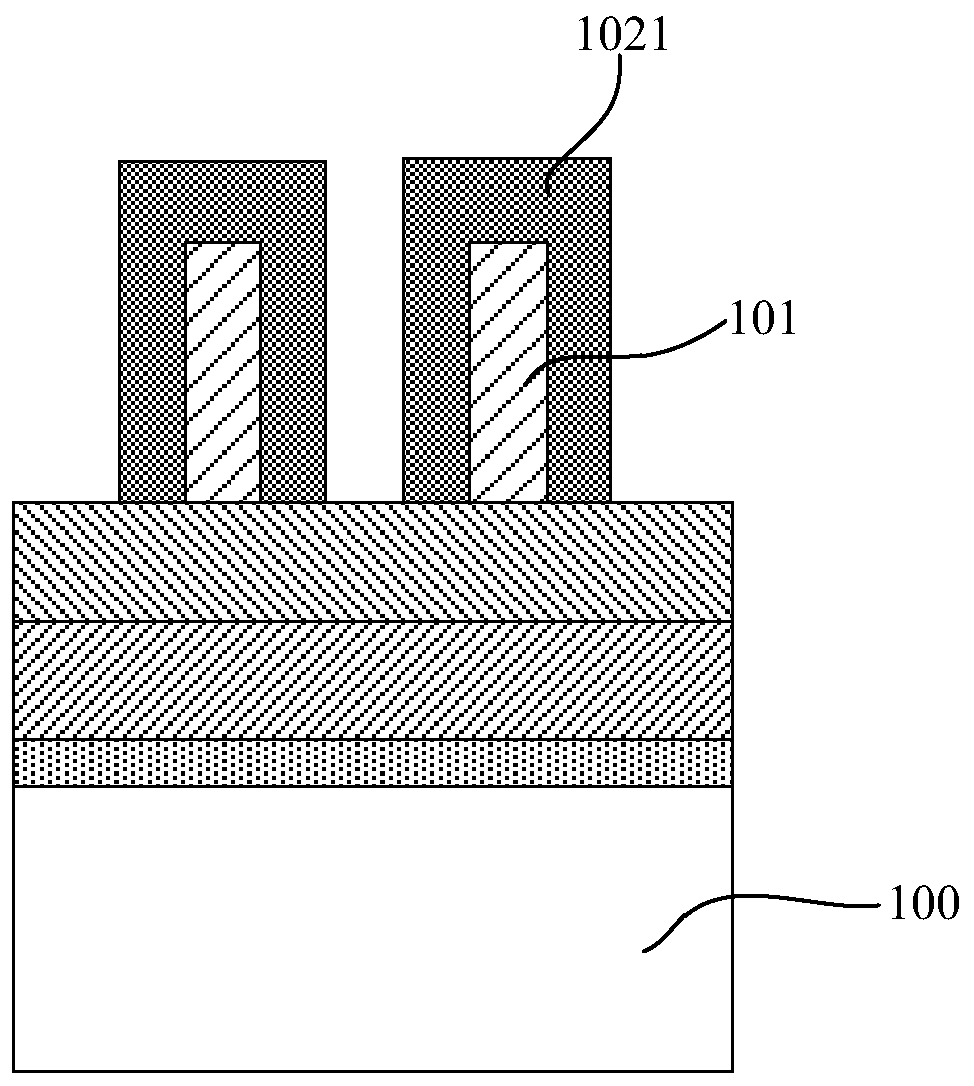

[0051] Step S301, providing a semiconductor substrate on which a target material layer is formed;

[0052] Step S302, forming a plurality of first spacers arranged at intervals on the target material layer;

[0053] Step S303, performing a first plasma treatment to modify the first spacer to form a modified first spacer;

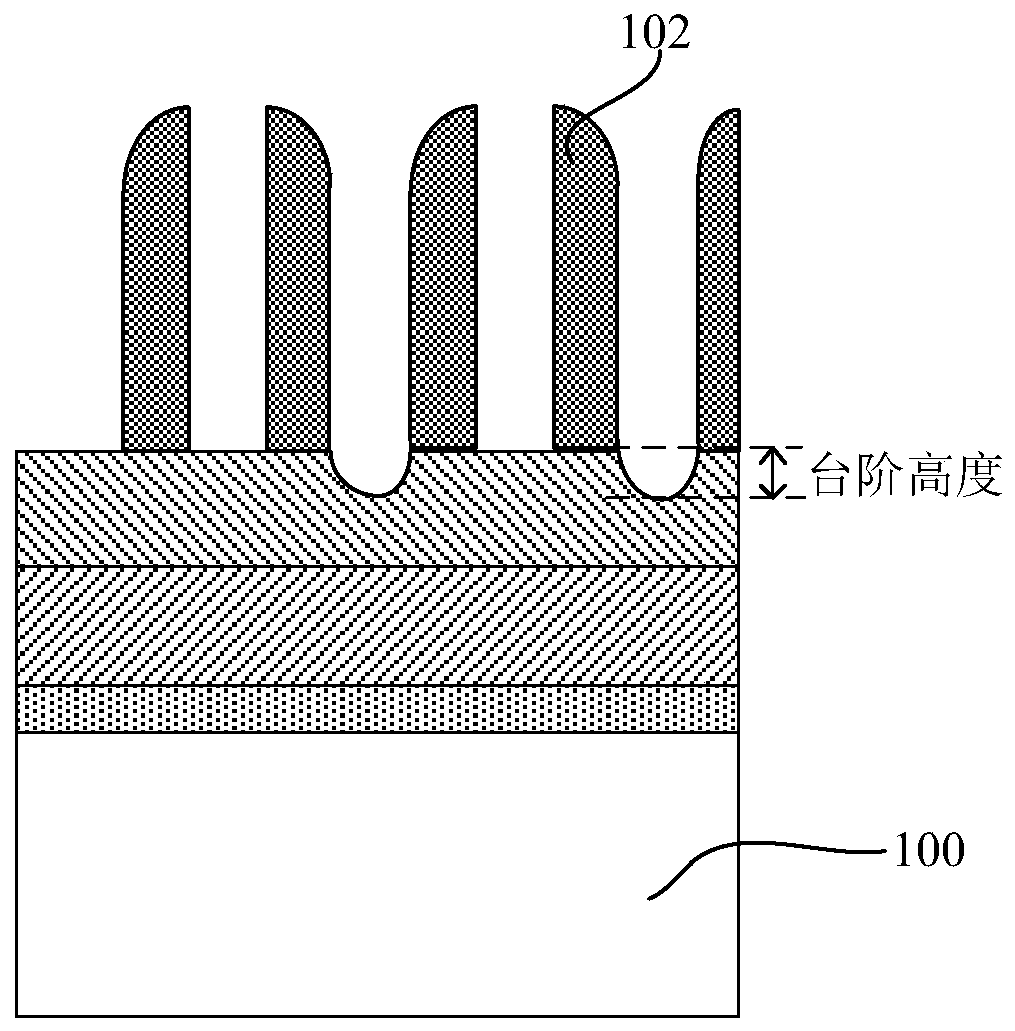

[0054] Step S304, forming a second spacer material layer to cover the modified first spacer and part of the surface of the semiconductor substrate;

[0055] Step S305, performing a second plasma treatment to modify the portion of the second spacer material layer located on the top surface of the modified first spacer and the portion located on the surface of the target material layer, thereby forming a modified second spacer material layer;

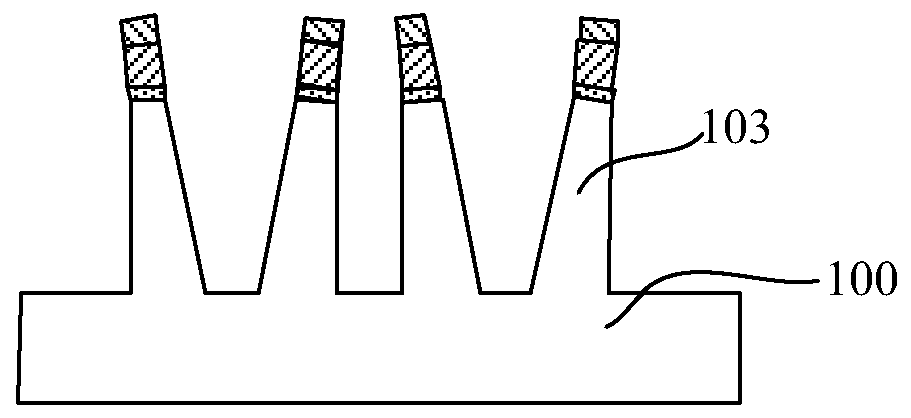

[0056] St...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More