A kind of preparation method of semiconductor device

A semiconductor and device technology, applied in the field of semiconductor preparation, to achieve the effects of small process fluctuation, high yield and low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

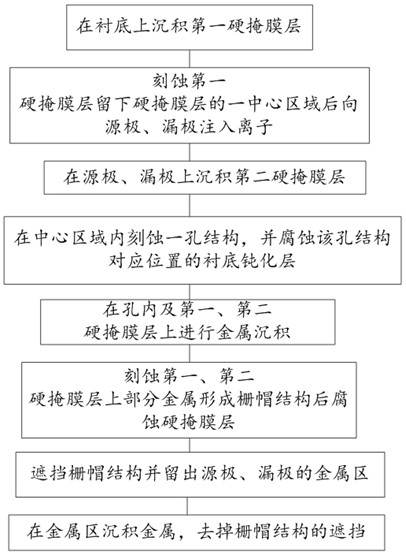

[0061] like figure 1 The shown preparation method of a semiconductor device can be widely used in the production of high-frequency millimeter-wave and terahertz chips, and the specific method includes the following steps:

[0062] Step S01: depositing a first hard mask layer on a substrate, the substrate comprising an epitaxial wafer 11 and a passivation layer 12 deposited on the epitaxial wafer 11;

[0063] Step S02: etching the first hard mask layer to leave the central region of the first hard mask layer, namely etching away the peripheral region of the first hard mask layer, and then implanting ions into the source and drain electrodes;

[0064] Step S03 : depositing a second hard mask layer on the source and drain electrodes after the ions have been implanted, that is, depositing a second hard mask layer on the outer edge of the first hard mask layer;

[0065] Step S04: etching a hole structure on the central region of the first hard mask layer, placing the hole structur...

Embodiment 2

[0071] Based on the principle of the above-mentioned Embodiment 1, this embodiment discloses a specific implementation manner, refer to Figure 2-Figure 19 . The substrate includes an epitaxial wafer 11 and a passivation layer 12 , and the substrate can be obtained by directly depositing the passivation layer 12 on the epitaxial wafer 11 . The epitaxial wafer needs to be cleaned in advance.

[0072] like figure 2 As shown, a first hard mask layer is deposited on a substrate comprising gallium nitride or gallium arsenide, and the passivation layer may be silicon dioxide or silicon nitride. The thickness of the passivation layer is at the nanometer level, such as 20 nm, 30 nm or other thickness, and the setting can be adjusted according to the actual situation. In this embodiment, 20 nm is taken as an example.

[0073] like image 3 As shown, a first medium 21 is deposited on the passivation layer 12 of the substrate. The first medium 21 can be silicon dioxide or silicon ni...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More